01 导言和概述

导言和概述

本数据表描述了台积电40nm ULP工艺中的TetraMem ADC IP。它的特点是:

占地面积小,适用于低速和多通道应用

异步架构,不需要外接高速时钟

可根据要求提供带隙

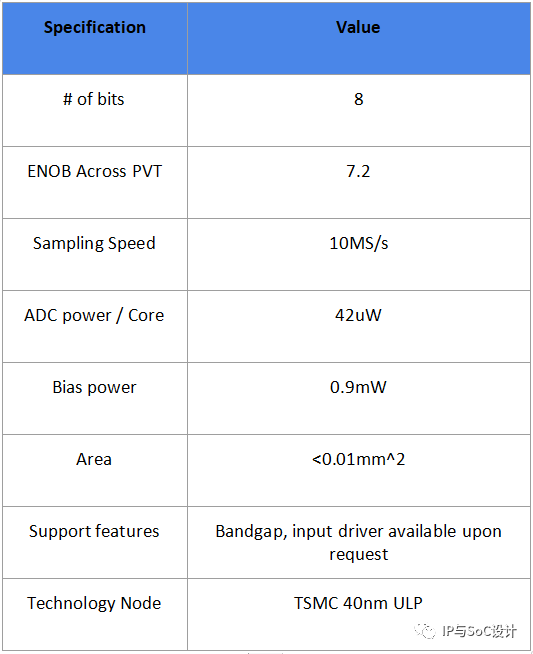

以下是主要规格表:

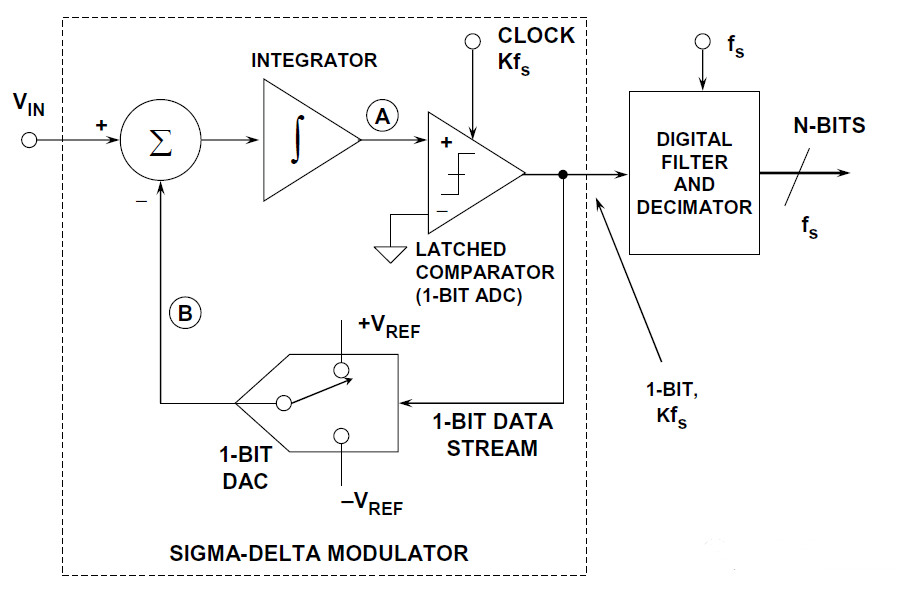

02ADC方框图

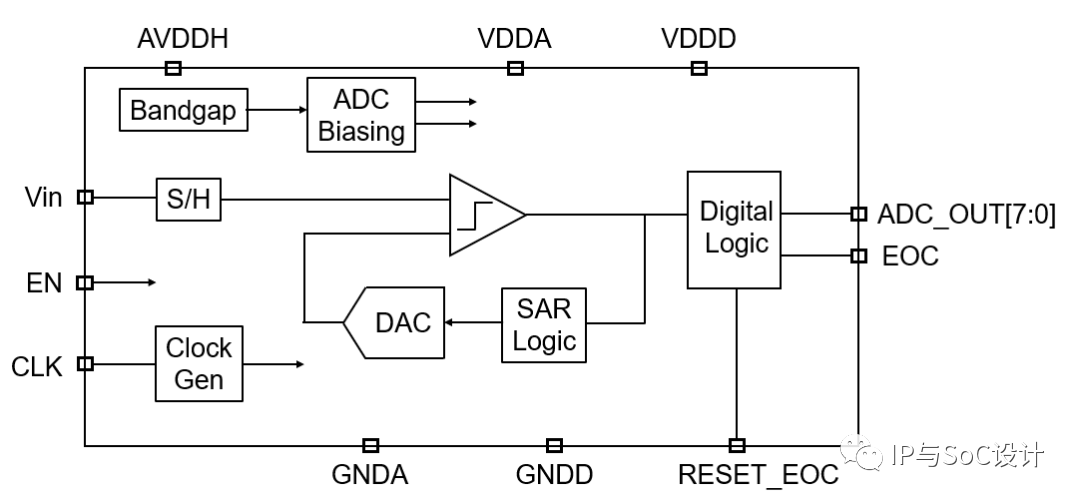

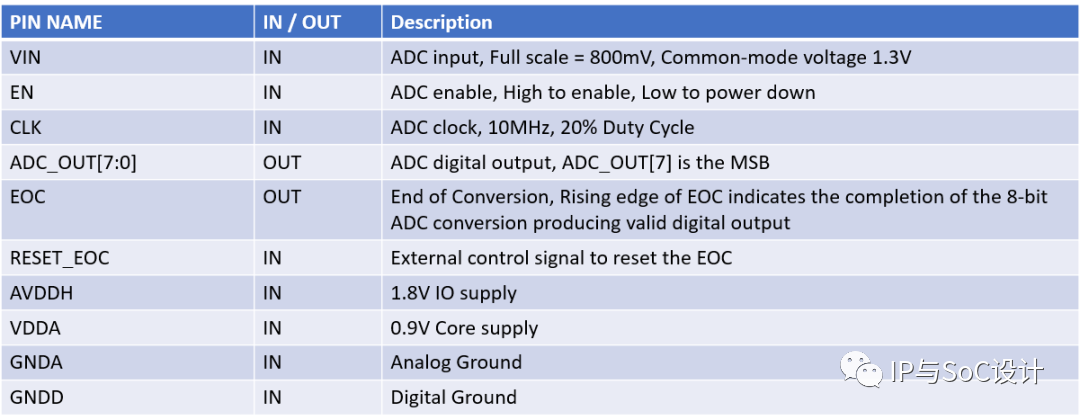

该IP的主要目标市场是物联网、模拟人工智能或温度传感器的低面积、低功耗和低速应用。以下是IP的框图:

我们设计了一个定制电容DAC(CDAC)阵列,其单位面积是业界最小的,可显著减少IP面积和开关能耗。此外,我们仔细调整性能敏感的电路,如比较器,基准驱动器等,以达到最佳的PPA组合。最后,我们使用了一个专有的带隙,以实现稳定的工作条件下,整个PVT的角落。

03ADC PIN描述

04ADC功率性能区

总功率:52uW

VDDA : 18uA x 0.9=16.2uW

AVDDH : 19uA x 1.8= 36uW

跨PVT角落的ENOB:7.3位

面积:7.76um x 120um = 931um2

Walden FoM = P /( fs x2 ^ ENOB )= 52u / (10M x 2 ^7.3)= 34FJ/凸步

05硅表征结果

2023年第三季度上市

06晶体管/金属使用

核心晶体管:LVT、ULVT

高压晶体管:1.8V晶体管

电容器:定制MOM和铸造PDK MOM

金属化:1P6M

电源:0.9V(铁芯),1.8V(高压)

审核编辑:汤梓红

-

传感器

+关注

关注

2552文章

51383浏览量

756444 -

台积电

+关注

关注

44文章

5685浏览量

166981 -

adc

+关注

关注

99文章

6533浏览量

545693 -

时钟

+关注

关注

11文章

1746浏览量

131780

原文标题:IP推荐:40nm ADC

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

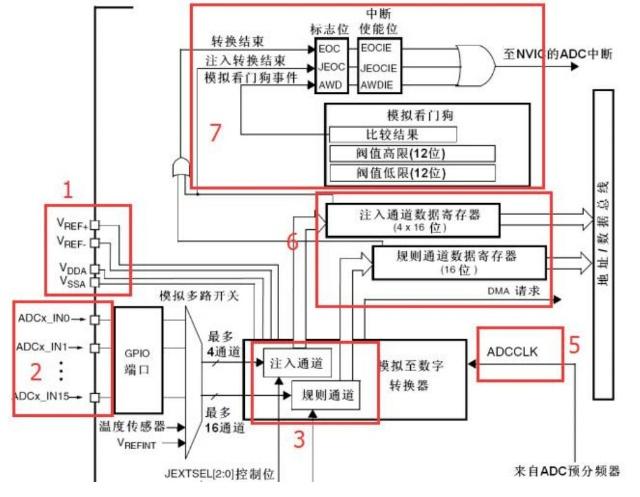

STM32F1 ADC主要特性和结构框图解析

时钟系统框图解读

STM32 ADC框图讲解

基于STM32单片机模块练习——ADC功能框图

STM32电源框图解析(VDD、VSS、VDDA、VSSA、VREF+、VREF-、VBAT等的区别)

ADC框图解析

ADC框图解析

评论