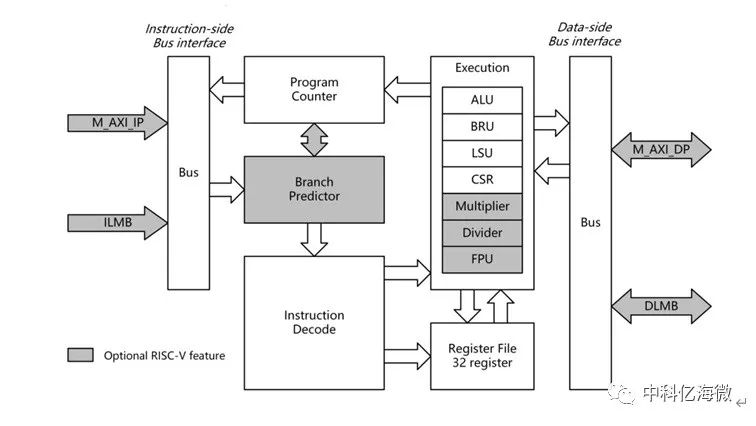

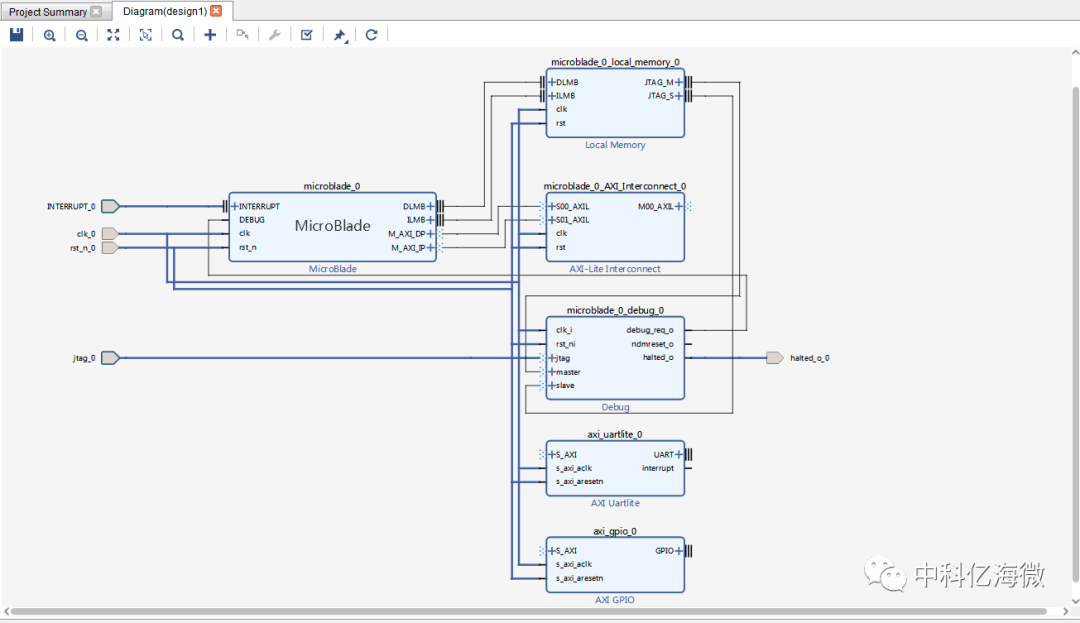

MicroBlade 处理器软核 IP是实现基于 RISC-V(Reduced Instruction Set Computer,精简指令集计算机)指令集架构的 32 位处理器软核,支持 RV32IM 指令集,支持 AXI4-Lite 接口,用于简化 FPGA 中复杂的控制逻辑。MicroBlade 处理器软核框架如下图所示:

MicroBlade 串口设计,开发板实现使用的是亿海神针系列EQ6HL45型FPGA。本篇通过原理图设计,学习MicroBlade基本结构,通过创建简单的MicroBlade工程,实现MicroBlade调用AXI Uartlite模块和AXI GPIO模块,完成串口打印功能,掌握在模块化设计中,MicroBlade最小系统的组成,学会导出、建立以及运行基于SDK的工程。

设计原理

本系统中的MicroBlade模块通过AXI Lite总线与AXI Uartlite IP和AXI GPIO IP进行通信,完成led指示灯的状态改变以及串口打印功能。

操作步骤

基于GUI界面创建工程

1

创建新的工程项目

1)双击桌面图标打开eLinx3.0;2)点击Create Project,或者单击File>New Project创建工程文件;3)将新的工程项目命名TEST_MICROBLADE,选择工程保存路径,勾选Create project subdirectory,创建一个新的工程文件夹,点击Next继续;4)选择新建一个RTL工程,由于本工程无需创建源文件,故将Do not specify sources at this time(不指定添加源文件)勾选上。点击 Next继续;5)选择目标FPGA器件:Family:eHiChip6 Package:CSG324Available devices: EQ6HL456)最后在新工程总结中,检查工程创建是否有误。没有问题,则点击Finish,完成新工程的创建。

2

创建原理图,添加IP,进行原理图设计

1)在Flow Navigator下,展开IP INTEGRATOR,选择Create Block Design创建新的原理图设计;2)将新的设计命名为design1;

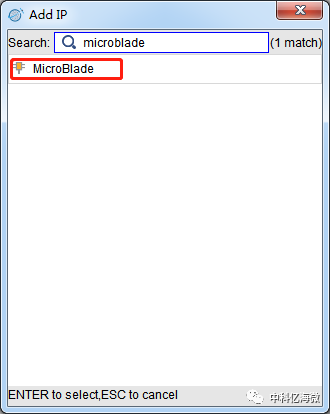

3)在Diagram中添加MicroBlade IP;

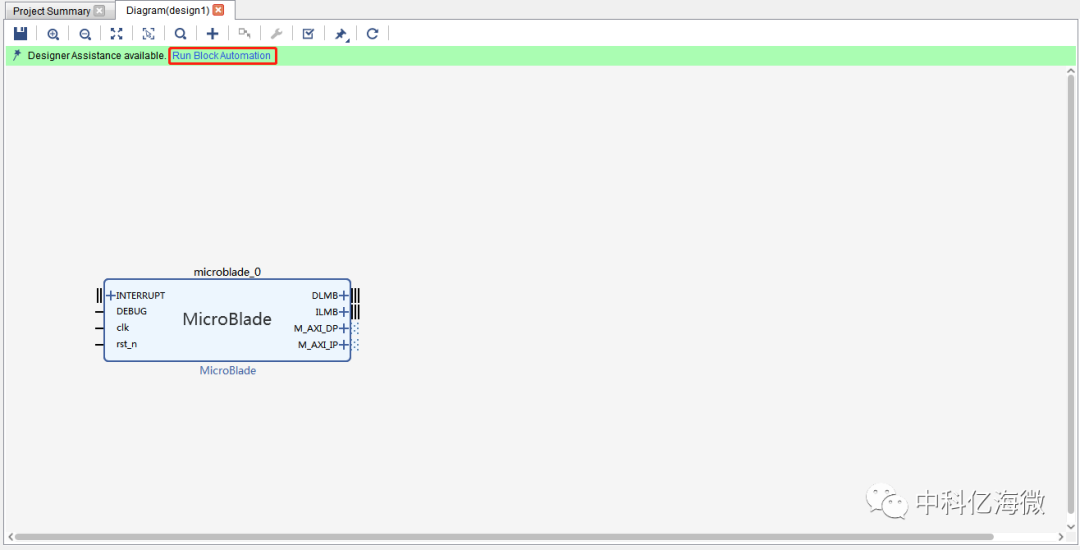

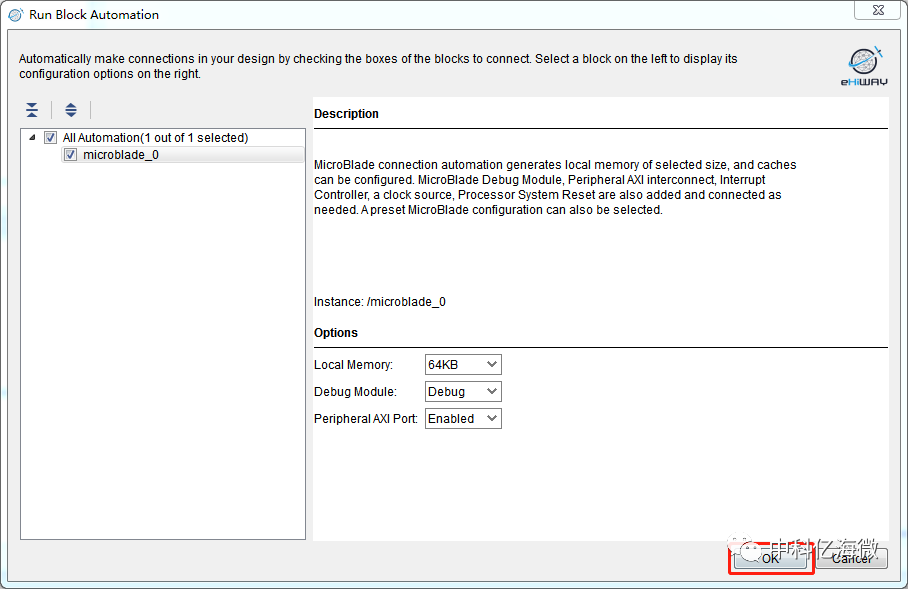

4)添加完成后如下图所示,点击Run Block Automation;

5) 在弹出窗口中,使用以下设置替换默认设置:

Local Memory: 64KB

Debug Module: Debug

Peripheral AXI Port: Enabled

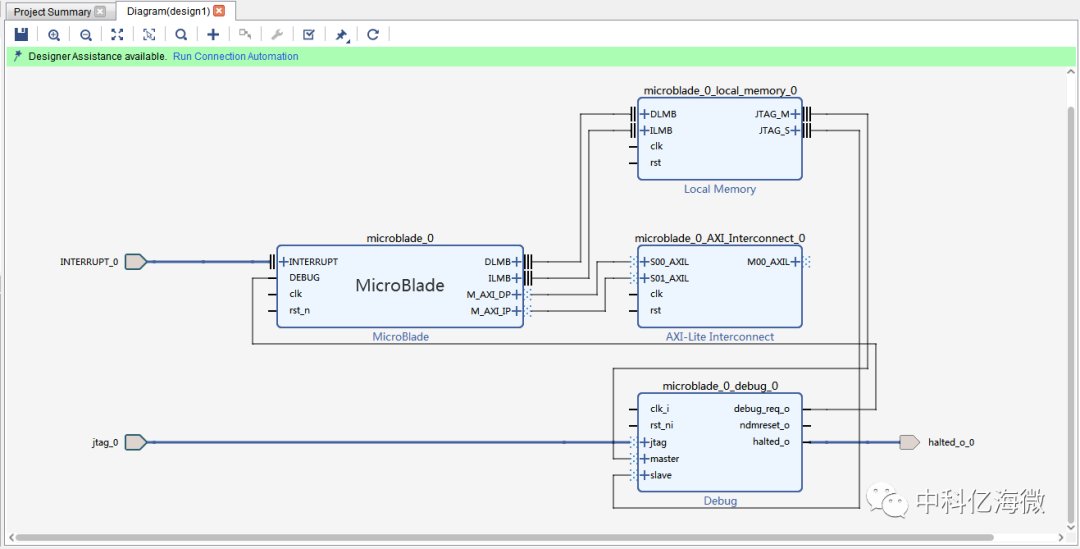

6)完成之后,eLinx会基于之前的设置自动生成一些额外的IP,并且会自动连接完毕,此时不要点击Run Connection Automation;

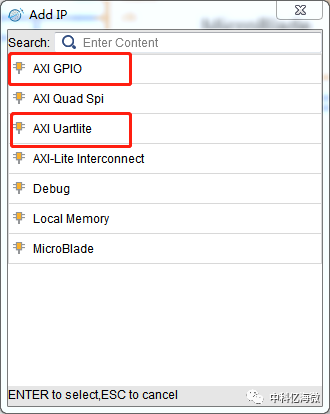

7)在Diagram中添加AXI Uartlite IP和AXI GPIO IP;

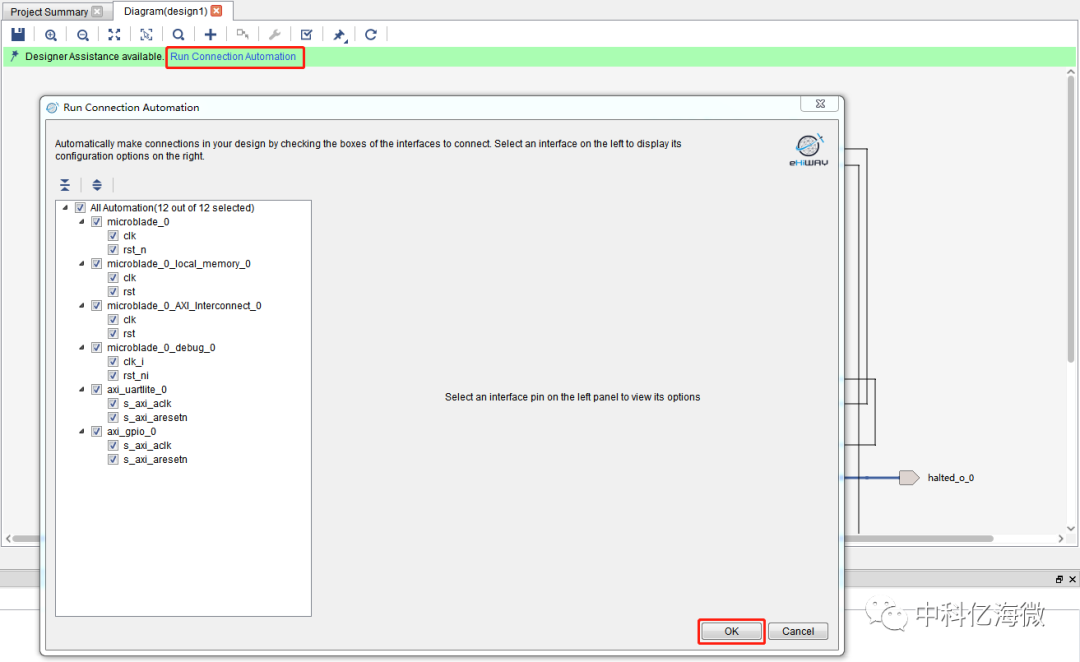

8)完成后,点击Run Connection Automation,在弹出窗口中勾选所有端口,点击OK继续;

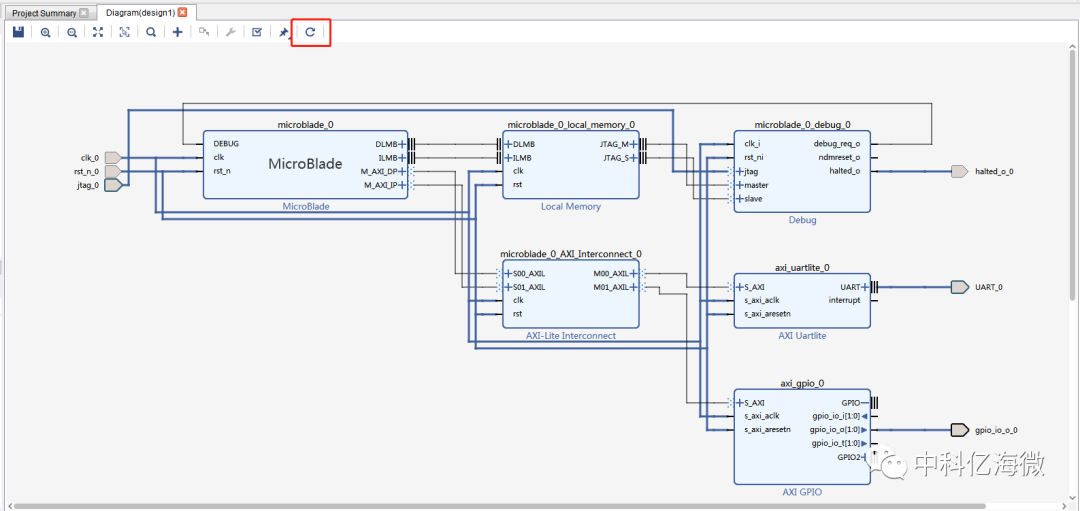

9)完成后,双击MicroBlade IP,打开界面,取消勾选Enable Interrupt隐藏Interrupt端口;10)双击AXI_Lite Interconnect IP,打开界面,把master端口的数量修改为2。手动完成AXI_Lite Interconnect IP与AXI Uartlite IP,与AXI GPIO IP的连线; 11)双击AXI Uartlite IP,打开界面,把AXI CLK Frequency修改为50(板卡晶振为50M)。单击UART端口,引出外设IO;12)双击AXI GPIO IP,打开界面,把GPIO通道GPIO Width修改为2,勾选Enable Dual Channel,把GPIO2通道GPIO Width修改为1。点击展开GPIO端口,点击gpio_io_o端口,引出外设IO;13)完成后,点击布局重置按钮重新布局,如下图所示:

14)Ctrl+S保存设计。

3

综合、实现、生成比特流文件

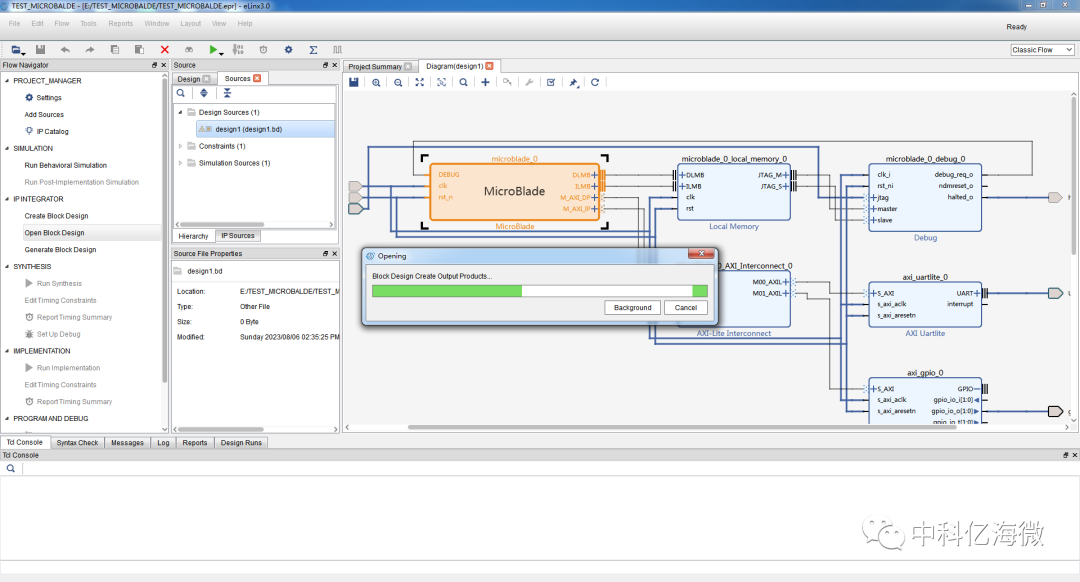

1)保存后,在Sources窗格中鼠标右键design1,选择Generate Output Products...,开始BD工程综合,如下图所示:

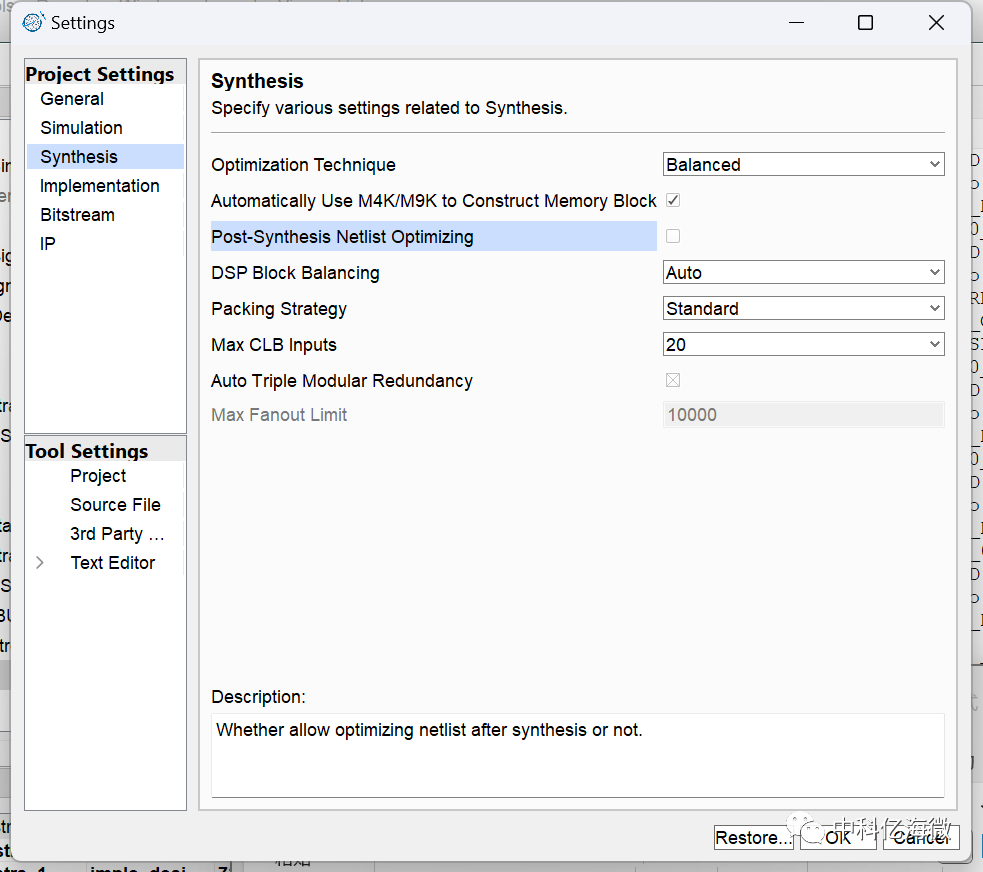

2)在Sources窗格中BD文件点击右键,选择Create HDL Wrapper,自动更新Sources列表,同时工程没有顶层,则自动设置为顶层;3)在界面上方工具栏中,选择Toos>Settings…在弹出的界面中点击Synthesis栏,取消勾选Post_Synthesis Netlist Optimizing;

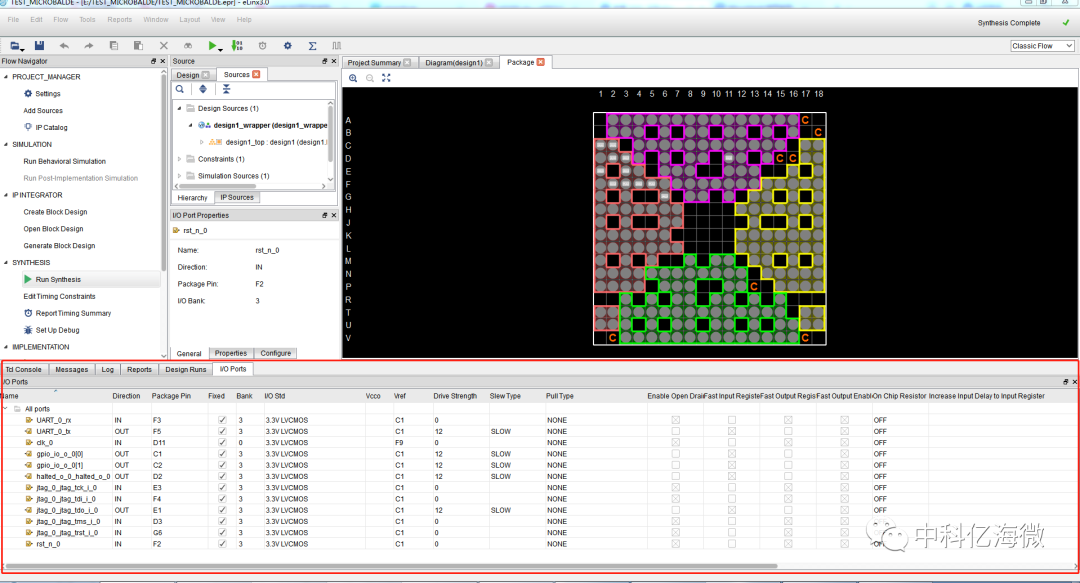

4)完成后继续点击Flow Navigator中的SYNTHESIS栏中的Run Synthesis进行工程综合;5)综合结束后在界面上方工具栏中,选择Toos >I/O Planning编辑管脚指定;

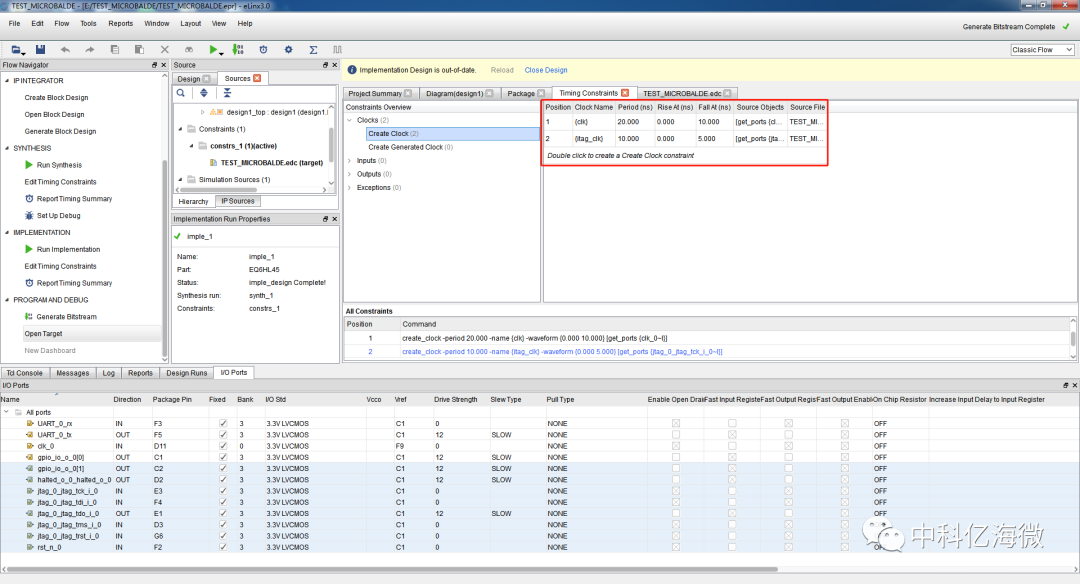

6)完成后在SYNTHESIS栏中点击Edit Timing Constraints添加2个时序约束后保存;

7)完成后继续点击左侧Run Implemenation按钮进行布局布线编译实现;8)在PROGRAM AND DEBUG栏点击Generate Bitstream。连接开发板,完成后点击Open target启动Programmer下载码流。下载成功后默认状态为led1和led2交替闪烁。

4

导出SDK并启动

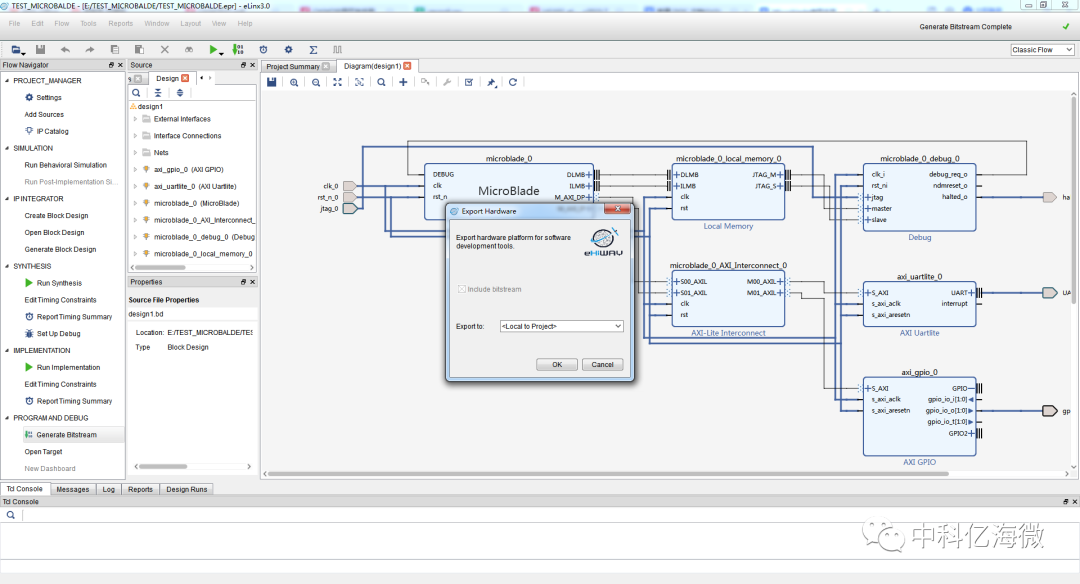

1)在顶部工具栏中,选择File>Export>Export Hardware导出硬件工程到SDK;

2)在工具栏中,选择File>Launch SDK,使用默认工程,启动SDK;

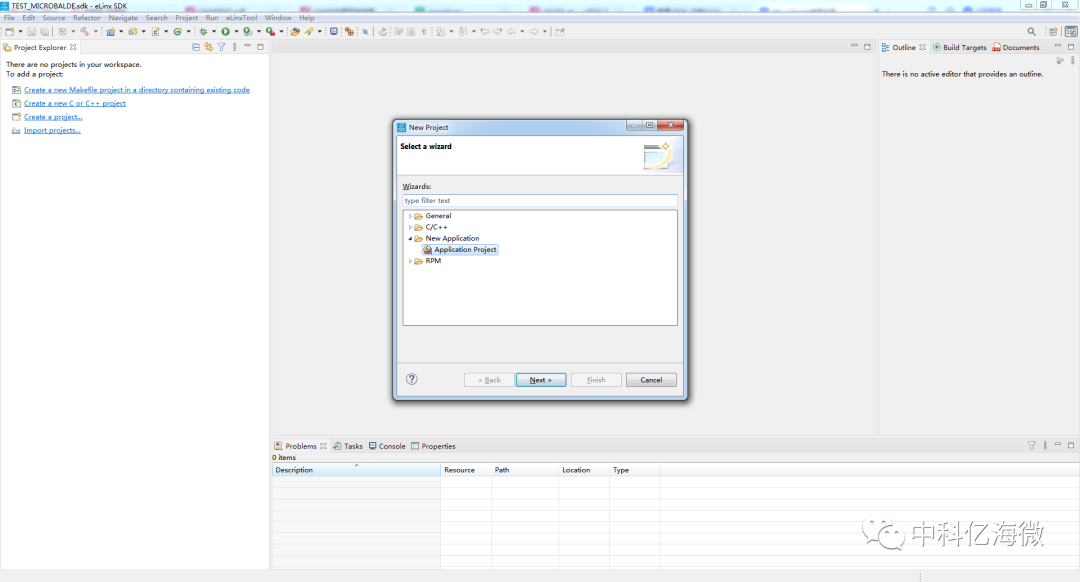

3)启动SDK后,如下界面,点击Create a project,弹出如下界面:

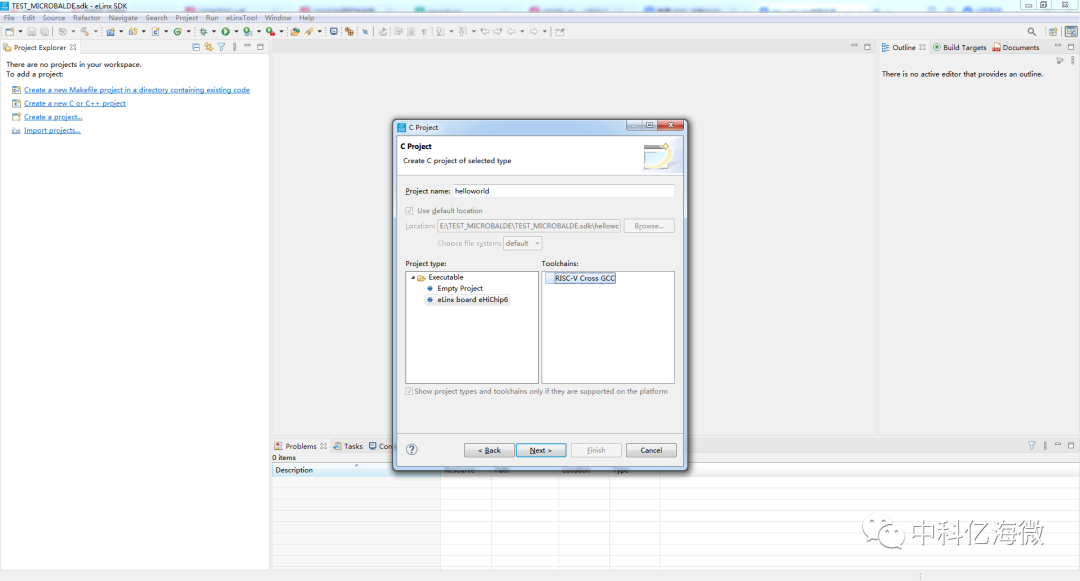

4)选择New Application->Application project,输入工程名helloworld,依次默认配置点击Finish完成创建;

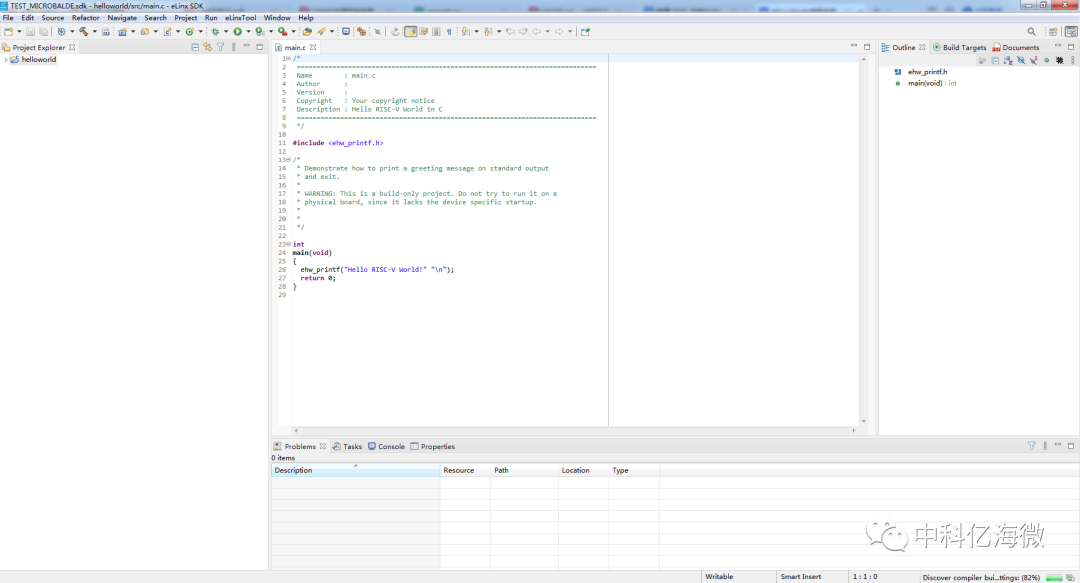

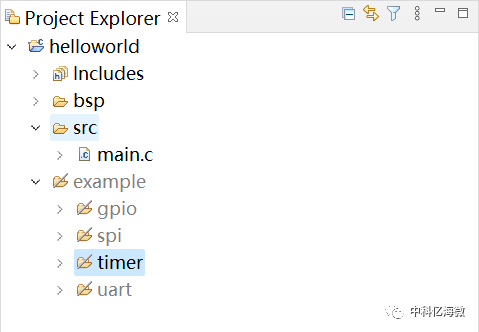

5)工程属性无需配置,工程中集成了例程,如下图:

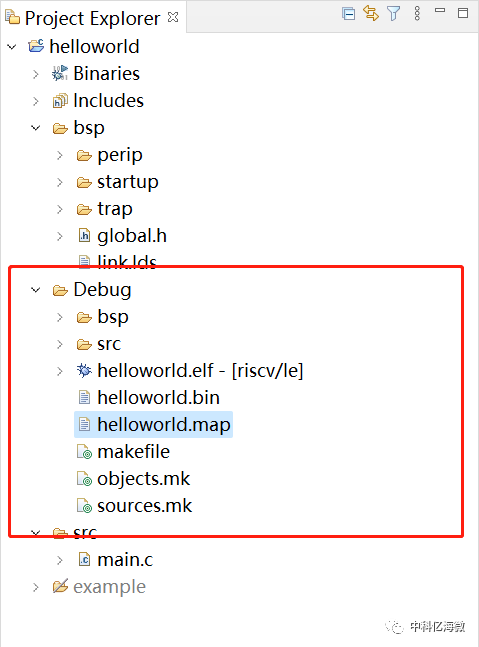

6)构建。构建成功后左侧生成Debug文件夹

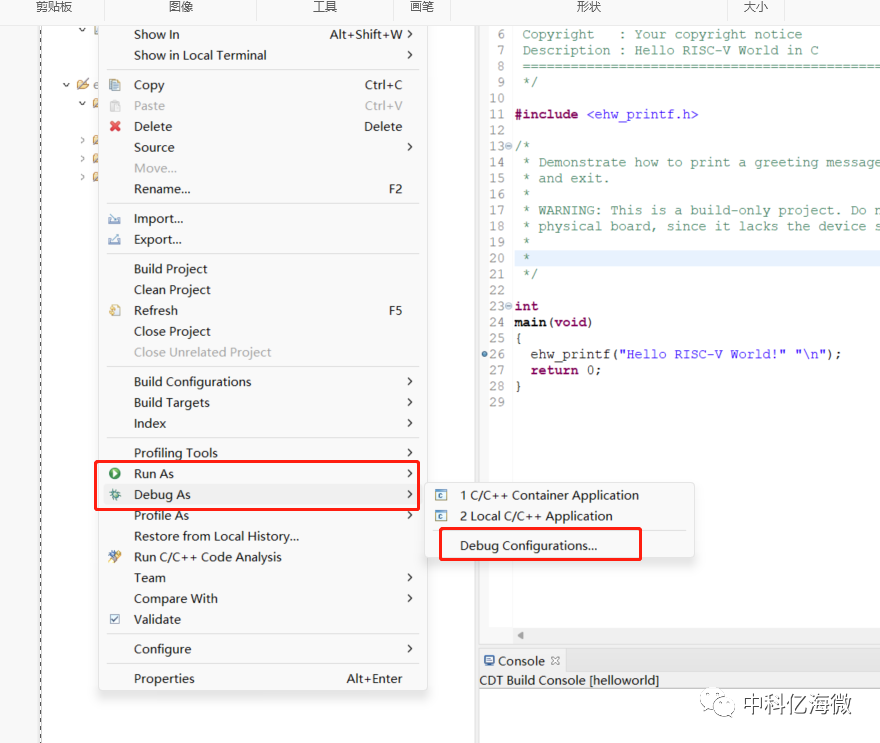

7)进行上板运行a)在工程名称上点击右键,弹出界面选择run as

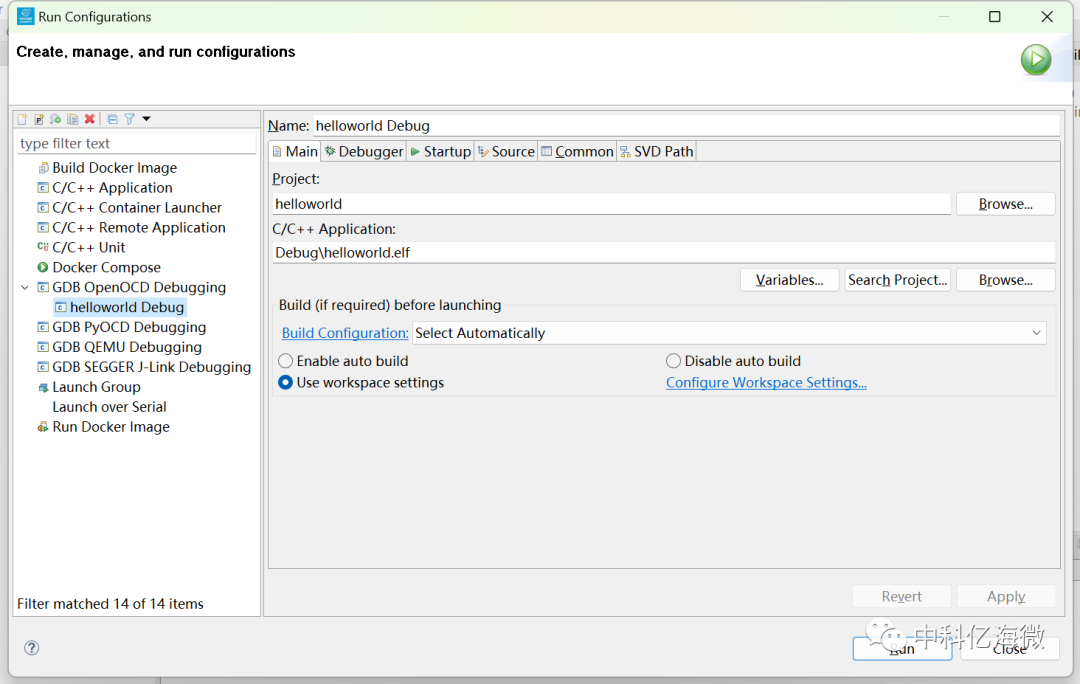

b)点击后弹出如下界面,在GDB OpenOCD Debugging按钮双击即可

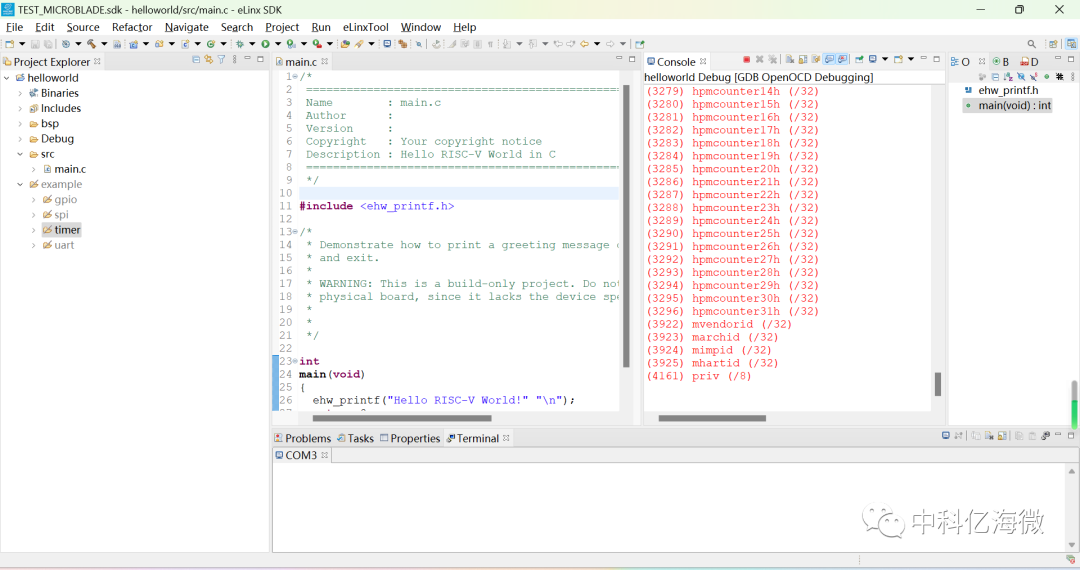

c)完成后,点击run可开始板卡联调,成功如下图所示:

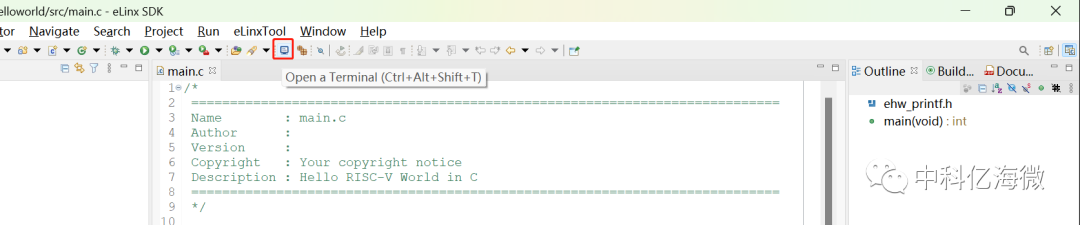

5)连接串口。选择SDK界面下方的Terminal窗口,点击下图的按钮

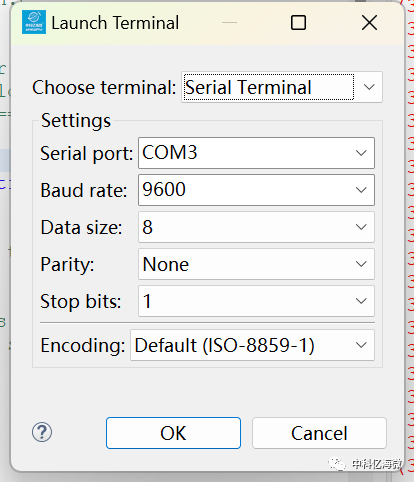

6)在弹出窗口中,进行如下配置:

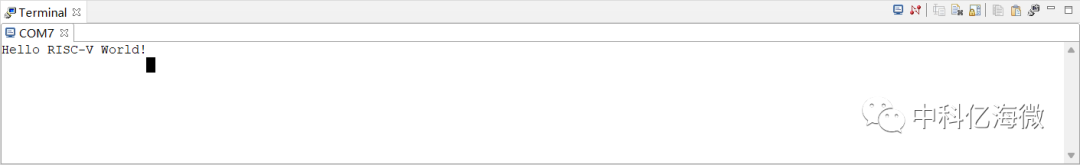

7)点击OK后,点击EQ6HL45板卡上的复位按钮(F2),Terminal界面出现了’Hello RISC-V World’字样。

-

处理器

+关注

关注

68文章

19286浏览量

229853 -

计算机

+关注

关注

19文章

7494浏览量

87963 -

IP

+关注

关注

5文章

1708浏览量

149554 -

串口

+关注

关注

14文章

1554浏览量

76523 -

串口传输

+关注

关注

0文章

33浏览量

1798

发布评论请先 登录

相关推荐

MicroBlade 串口设计

MicroBlade 串口设计

评论