近日,第五届集成电路EDA设计精英挑战赛正式启幕。作为国内EDA领域的专业赛事之一,芯华章已连续四年参与支持赛事,持续助力产业人才培养、深化产学研合作,为中国EDA产业培养和储备优秀的新生代技术力量。今年,芯华章发布“基于VCD的FSM覆盖率统计”企业赛题,欢迎各位同学们前来“破题”!

一、 赛题名称

基于VCD的FSM覆盖率统计

二、 背景知识

Coverage是衡量数字验证质量的重要指标,FSM Coverage作为其中重要一环,衡量了验证过程中的状态和状态转移覆盖状况。通过检查各状态和状态转移是否被覆盖到,我们可以检查预期的功能是否被覆盖;相反的,通过检查是否有不在设计范围内的状态或状态转移被意外覆盖到,进而检测到设计中的漏洞。

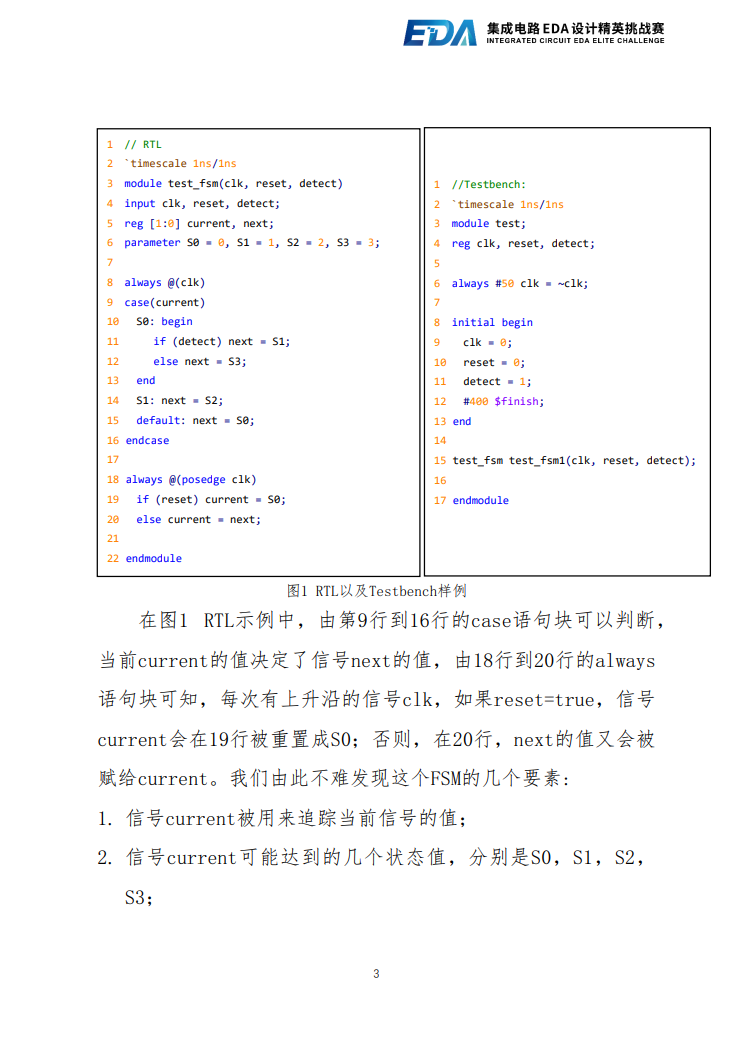

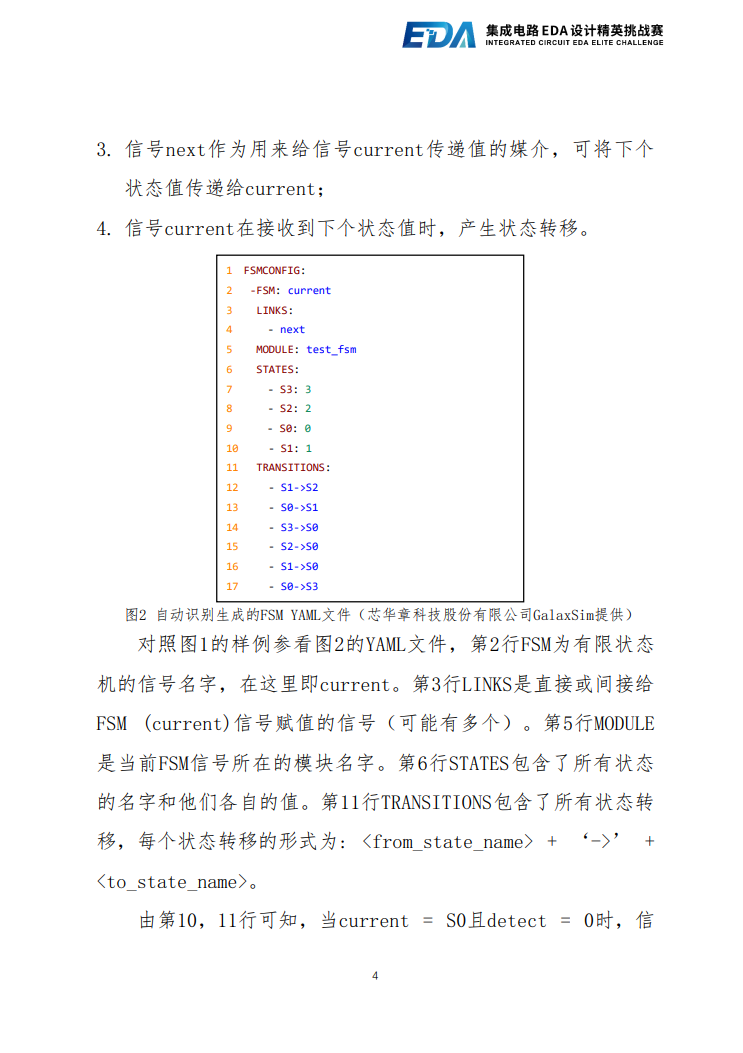

FSM Coverage通常包括两部分内容,第一部分是FSM(有限状态机)识别和模型提取,该模型描述了有限个状态以及这些状态之间的转移行为;第二部分是FSM覆盖情况,即提取的状态和状态转移模型是否在仿真过程中被覆盖到。

值得注意的是,第一部分有限状态机识别发生在静态分析的过程中,识别的是可能的状态和可能的状态转移,并不代表被识别的状态或状态转移一定能在仿真过程中被覆盖,这一点需要跟第二步区分开来。

在本赛题中,我们会关注其中更为重要的第二步,FSM Coverage的计算,对于第一步状态机的识别,我们已使用芯华章GalaxSim的自动识别提取FSM的功能,通过YAML文件提供了FSM的相关信息,包括FSM的信号名字、状态名字、状态值、状态转移。

三、 赛题指南

向左滑动查看更多内容>>

扫码下载芯华章赛题文档

四、 赛题Chair

李 康

李康博士,西安电子科技大学微电子学院副教授,硕士导师。研究方向主要包括数字集成电路设计、优化与自动化技术。熟悉体系结构与组成技术,并长期从事面向高速网络交换的电路设计以及PPA优化方法研究。同时开展可靠性器件与电路模型技术研究,开发数字电路可靠性退化与寿命的预测模型与高可靠性数字电路设计方法,建立起超深亚微米集成电路可靠性评估平台。研究AI与设计自动化领域的技术相结合的高效高精度功耗预测技术,研发出系统芯片的功耗评估工具。先后承担相关方向的VLSI 重大专项、国家自然基金项目、科技部重点研发计划、部委预研及企业合作研究项目10余项,发表SCI与EI索引论文20余篇,授权专利8项。

五、 大赛时间

2023(第五届)集成电路EDA设计精英挑战赛赛程时间安排如下:

EDA设计精英挑战赛现已正式开放报名,关注官网(http://eda.icisc.cn),获取更多大赛信息。

六、 奖项设置

麒麟杯(1支):20万

菁英杯(1-2支):8万

一等奖(最高15%):2万

二等奖(最高30%):1万

关于芯华章科技

芯华章聚集全球EDA行业精英和尖端科技领域人才,以智能调试、智能编译、智能验证座舱、智能云原生等技术支柱,构建芯华章平台底座,提供全面覆盖数字芯片验证需求的七大产品系列,包括:硬件仿真系统、FPGA原型验证系统、智能场景验证、形式验证、逻辑仿真、系统调试以及验证云,为合作伙伴提供自主研发、安全可靠的芯片产业解决方案与专家级顾问服务。同时,芯华章致力于面向未来的EDA 2.0 智能化电子设计平台的研究与开发,以技术革新加速系统创新效率,让芯片设计更简单、更普惠。

-

芯华章

+关注

关注

0文章

178浏览量

11447

原文标题:诚邀破题!集成电路EDA设计精英挑战赛芯华章赛题发布!

文章出处:【微信号:X-EPIC,微信公众号:芯华章科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

2024 FPGA和EDA双赛事安路科技再创佳绩

广立微助力2024中国研究生创“芯”大赛·EDA精英挑战赛

e络盟社区携手恩智浦发起智能空间楼宇自动化挑战赛

诚邀破题!集成电路EDA设计精英挑战赛芯华章赛题发布!

诚邀破题!集成电路EDA设计精英挑战赛芯华章赛题发布!

评论