TSN是目前国际产业界正在积极推动的全新工业通信技术,为下一代网络技术的核心。ZLG致远电子敢为人先,准确把握新一轮科技革命的历史机遇,在TSN领域积极布局,推出了TSN系列核心板产品M64xx-T。

TSN技术简介

TSN技术简介

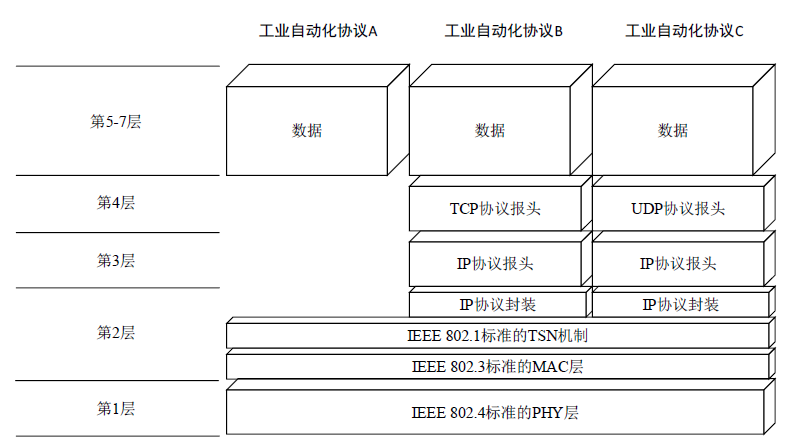

时间敏感网络(Time-sensitive Networking,TSN)是在IEEE 802.1标准以太网框架下制定的新一代标准以太网技术, 运行在OSI 模型中的数据链路层,如图1所示,TSN技术源于标准以太网的队列传输机制,网络帧格式也是采用包含VLAN 标签的标准以太网帧格式。

图1TSN的IEEE802.1框架

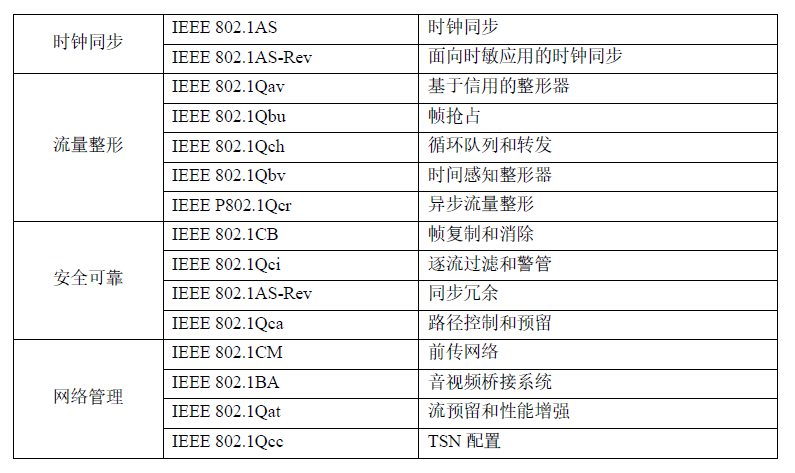

在标准层面,IEEE 802.1时间敏感网络工作组发布了一套用于工业和汽车网络的开放实时以太网标准TSN,包括IEEE 802.1Qbv、IEEE 802.1Qcc、IEEE 802.1AS 等标准,如图2所示,旨在降低布线成本,打破信息孤岛,同时在通信过程中传输不同时间敏感性的数据。

图2TSN的协议簇 TSN时间同步技术应用实践

TSN时间同步技术应用实践

当前时间敏感网络技术已经成为包括芯片厂商、通信设备厂商、自动化厂商、相关行业组织以及各类研究机构在内的产业链各个组成环节关注的热点,我司紧跟科技创新发展的新趋势,推出了TSN技术落地实践项目M64xx-T系列核心板。

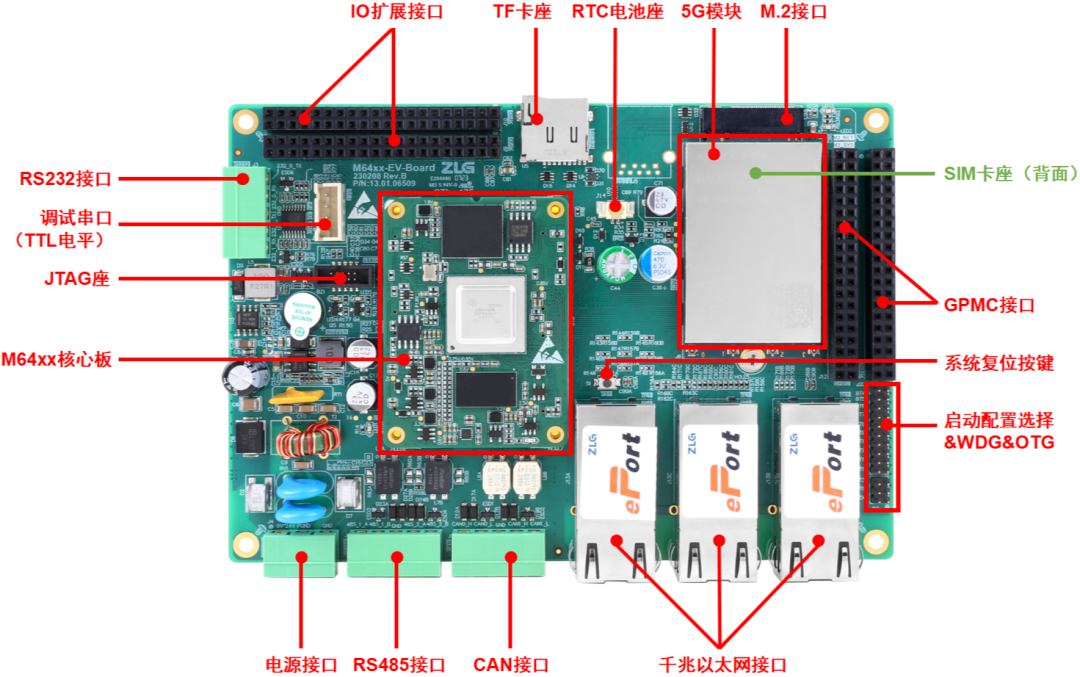

M6442-EV-Board是ZLG致远电子精心推出的集工控与评估于一身的评估板。该评估板了搭配M6442-1GF4GLI-T核心板做评估和扩展使用,方便灵活。可满足M64xx核心板的接口评估,也可以直接用于电机驱动器、工业网关、远程监控、工厂自动化等应用场合。

图3M6442-EV-Board评估板

Sitara AM6x处理器通过子系统支持TSN标准和其它工业协议下的千兆位传输速率,可在单一网络上融合以太网和实时数据传输。这一特性对于工业4.0应用中的实时通信至关重要,可在工厂中实现可重新配置软件的网络物理系统。

在通信网络中,许多业务的正常运行都要求网络时间同步。时间同步包括频率和相位两个方面的同步,通过时间同步可以使得整个网络各设备之间的频率和相位差保持在合理的误差范围内。

本文基于M64xx-T核心板,对其TSN时间同步功能进行了全方位的测试,测试结果可为用户进行TSN技术选型提供参考。

1. 测试环境内核版本,如下所示:

root@M6442:~# uname -aLinux M6442 5.10.100-rt83-gc1a1291911 #24 SMP PREEMPT_RT Thu Aug 10 0918 CST 2023 aarch64 GNU/Linux

ptp4l版本,如下所示:

root@M6442:~# /opt/ptp4l -v3.1-00108-g27bc9d5-dirty

2. 创建ptp配置文件,文件内容如下所示:

root@M6442:~# cat /opt/ptp.cfg [global]tx_timestamp_timeout 400

3. Master侧配置,如下所示:

root@M6442:~# /opt/ptp4l -E -2 -H -i net3 -l 6 -m -q -p /dev/ptp1 ptp4l[847.811]: selected /dev/ptp1 as PTP clockptp4l[847.812]: port 1 (net3): taking /dev/ptp1 from the command line, not the attached ptp2ptp4l[847.823]: port 1 (net3): INITIALIZING to LISTENING on INIT_COMPLETEptp4l[847.824]: port 0 (/var/run/ptp4l): INITIALIZING to LISTENING on INIT_COMPLETEptp4l[847.824]: port 0 (/var/run/ptp4lro): INITIALIZING to LISTENING on INIT_COMPLETEptp4l[854.119]: port 1 (net3): LISTENING to MASTER on ANNOUNCE_RECEIPT_TIMEOUT_EXPIRESptp4l[854.119]: selected local clock 001497.fffe.481912 as best masterptp4l[854.119]: port 1 (net3): assuming the grand master role

4. Slave侧配置与测试

root@M6442:~# /opt/ptp4l -E -2 -H -i net3 -s -l 6 -m -q -p /dev/ptp3 -f /opt/ptp.cfg ptp4l[1789.231]: selected /dev/ptp3 as PTP clockptp4l[1789.246]: port 1 (net3): INITIALIZING to LISTENING on INIT_COMPLETEptp4l[1789.247]: port 0 (/var/run/ptp4l): INITIALIZING to LISTENING on INIT_COMPLETEptp4l[1789.247]: port 0 (/var/run/ptp4lro): INITIALIZING to LISTENING on INIT_COMPLETEptp4l[1791.037]: port 1 (net3): new foreign master 001497.fffe.481912-1ptp4l[1795.038]: selected best master clock 001497.fffe.481912ptp4l[1795.038]: port 1 (net3): LISTENING to UNCALIBRATED on RS_SLAVEptp4l[1798.038]: master offset -703704169411022 s0 freq +0 path delay 526ptp4l[1799.040]: master offset -703704169406384 s1 freq +4637 path delay 324ptp4l[1800.038]: master offset -2900 s2 freq +1737 path delay 324ptp4l[1800.039]: port 1 (net3): UNCALIBRATED to SLAVE on MASTER_CLOCK_SELECTEDptp4l[1801.039]: master offset 2 s2 freq +3769 path delay 122ptp4l[1802.039]: master offset 596 s2 freq +4364 path delay 196ptp4l[1806.040]: master offset 234 s2 freq +4544 path delay 534ptp4l[1807.040]: master offset 137 s2 freq +4518 path delay 543ptp4l[1808.040]: master offset 65 s2 freq +4487 path delay 543ptp4l[1809.040]: master offset 11 s2 freq +4452 path delay 565ptp4l[1812.041]: master offset 0 s2 freq +4450 path delay 568

测试结果说明如下:

- master offset,表示ptp协议中定义的主从端时间差(单位:ns);

- s0、s1、s2,指示器显示时钟伺服的不同状态:s0表示已解锁,s1 表示时钟步进,s2 表示已锁定。如果伺服处于已锁定状态(s2),并且 pi_offset_const 选项在配置文件中设置为负值,则时钟不会步进,而只会缓慢调整;

- freq,表示时钟的频率调整(以十亿分率(ppb)为单位);

- path delay,表示从主时钟发送的同步消息的预计延迟(以纳秒为单位)。

由上可知M64xx-T核心板的TSN时间同步性能参数中,稳定单跳时延为600ns以下,抖动小于20ns,时间同步精度20ns。

-

网络

+关注

关注

14文章

7607浏览量

89389 -

工业

+关注

关注

3文章

1889浏览量

46987 -

核心板

+关注

关注

5文章

1037浏览量

30025 -

TSN

+关注

关注

3文章

244浏览量

16971

发布评论请先 登录

相关推荐

PET_RK3588_CORE核心板

PET_RK3562_CORE核心板

为什么要选择BGA核心板?

为何ZLG致远电子要推出LGA嵌入式核心板?

嵌入式核心板的分类及PCB设计

骁龙665安卓核心板_SM6125核心板参数_安卓核心板高通方案定制

为什么M3568核心板上由四个连接器,却有黑白两种颜色?

MT8390安卓核心板_MT8390 (Genio 700)核心板详细参数

功率电感在M6442工控主板中的应用

NXP i.MX 93核心板工业方案

NXP系列-NXP i.MX 93核心板开发板-入门级嵌入式核心板-产品资料

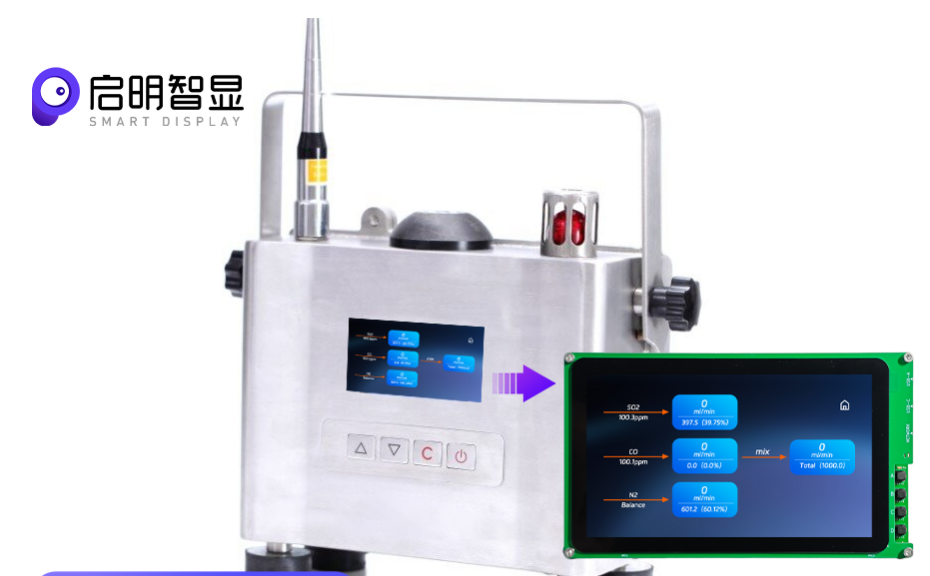

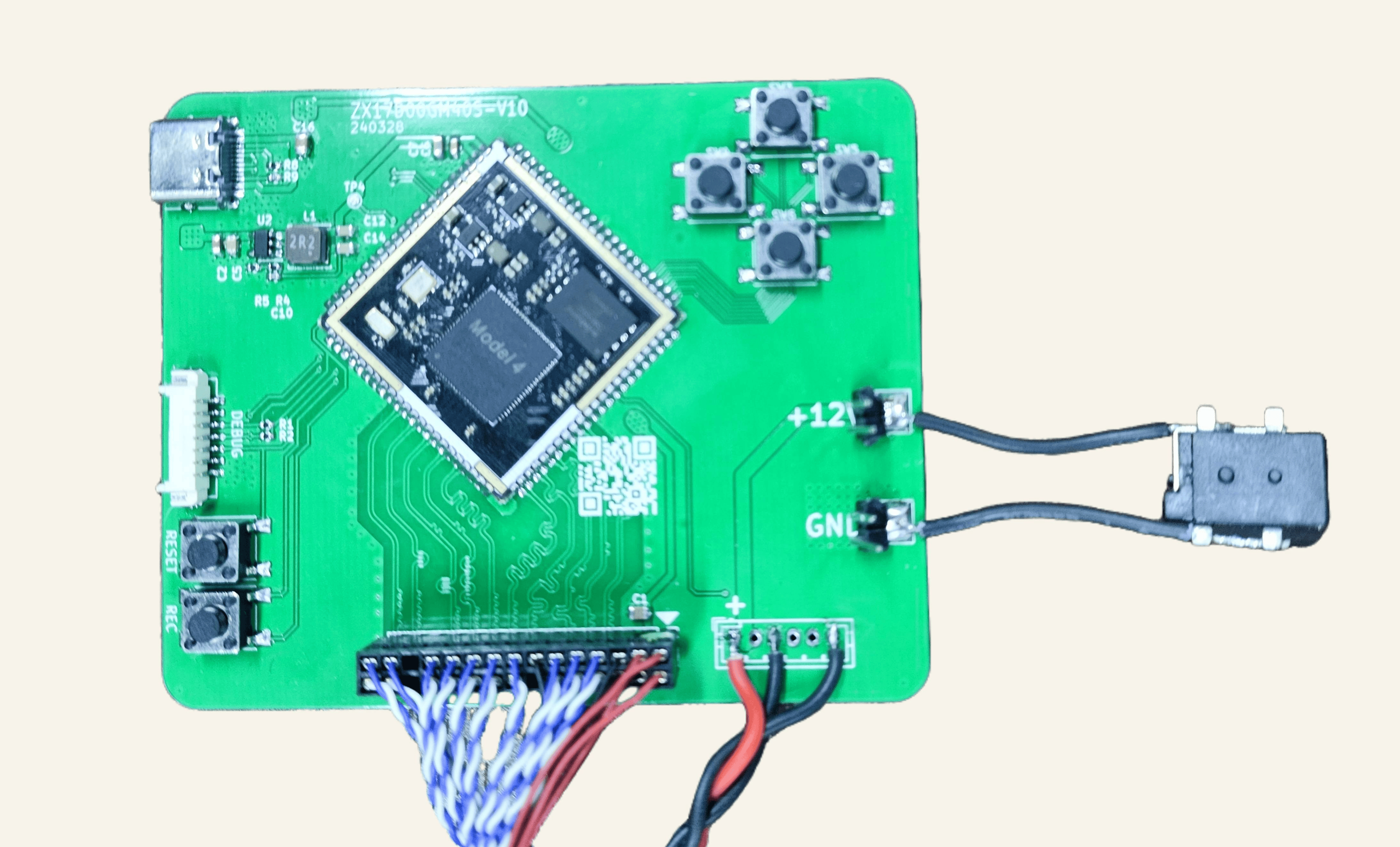

基于M3核心板的7寸串口屏:为气体检测设备带来全新交互体验

M6442核心板TSN初体验

M6442核心板TSN初体验

评论