01 概述

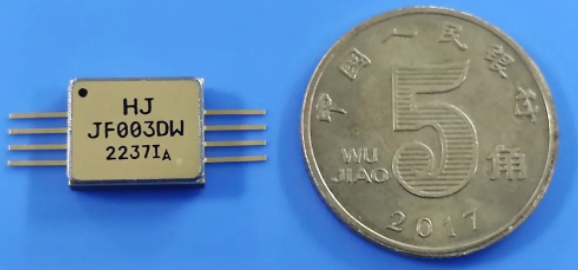

HJJF003半导体桥塞点火/起爆激发单元是一种快速放电的高端开关。它是基于符合GJB2438要求的厚膜集成制作而成。具有体积小、放电电流大、放电快速等特点。加装了抗射频(EMI)及静电(ESD)防护。适用于高可靠地激发对射频和静电敏感的1Ω/3Ω半导体桥塞(SCB)。也可用做半导体激光器泵源高可靠的激发单元。

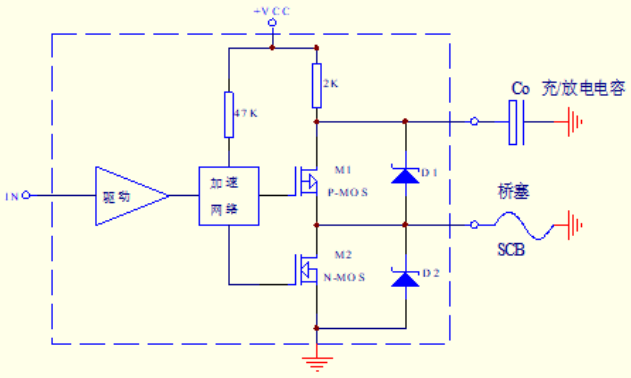

02 电原理图

图1 HJJF003电原理图

设计思路

半导体桥塞相对于合金桥丝而言,具有点火所需要的能量小、时间短、能够形成高温等离子放电等特性。要求其激发单元必须具备快速放大电流的能力。桥塞一端必须接地(GND),出于安全性的考虑,必须选用高端开关执行。在一定的供电电压及电流要求下,P-MOS管是最好的选项。而成品P-MOS管的应用又遇到了两个挑战,一是引线寄生电感,二是不合理的驱动方式会造成P-MOS管儿的开启损耗偏大,进而影响激发效果。

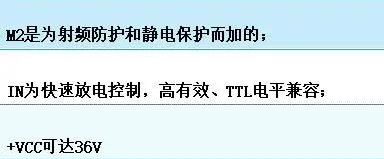

实际工况条件,半导体桥塞还会受静电放电(ESD)和射频干扰(EMI)的影响。静电会损伤桥塞。强射频干扰会造成误触发。静电、射频干扰、放电的V-t波形图如图2所示。

图2 放电的V-t波形图

静电脉冲有时可能高达几万伏,但其作用时间Δt1≤2~3μs;射频干扰虽在几十伏到上百伏不等,但其持续的时间Δt2在几十μs到几十ms之间;正常需要的放电脉冲在15~36V,有效作用时间Δt3在1μs~10μs之间。因此,HJJF003设计的主要思路就是:通过合理的驱动P-MOS管获取强放电脉冲;通过M2(NMOS管)来吸收ESD/EMI。由于厚膜集成工艺均用裸管芯通过超声换能焊接成系统,故寄生电感可降至最小。

对静电放电(ESD)和射频干扰(EMI)的防护机理分两种情况:

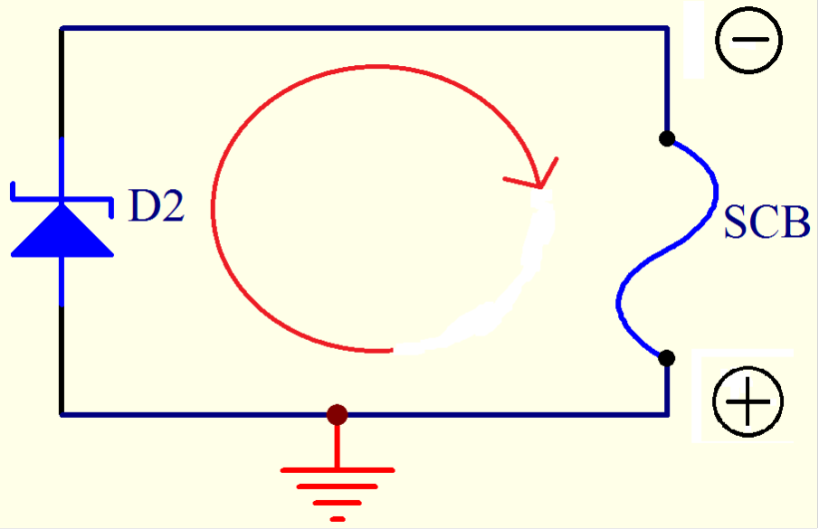

1.在系统不加电的情况下,此时M1、M2关断,若半导体桥塞(SCB)感受到一个负向的ESD/EMI,则能量会通过D2泄放,如下图3所示:

图3

此时,SCB上的最大感受电压≤1.2V(@IF≤38A),能够有效地保护SCB不激发/亚点火。

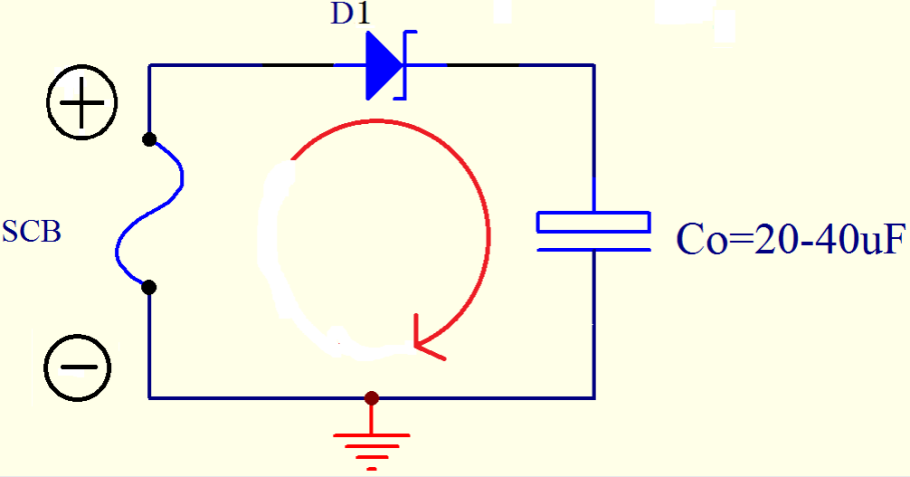

若SCB上感受到一个正向的ESD/EMI,则能量会通过D1和CO释放,如下图4所示:

图4

此时,因为CO没有充电,正负极相当于短路态。静电放电(ESD)属于极窄脉冲,其时间不足以使CO解除短路态。而EMI放电脉冲虽然较宽,但只要小于300ms,也不足以使CO充电。从而有效保护SCB不激发/亚点火。

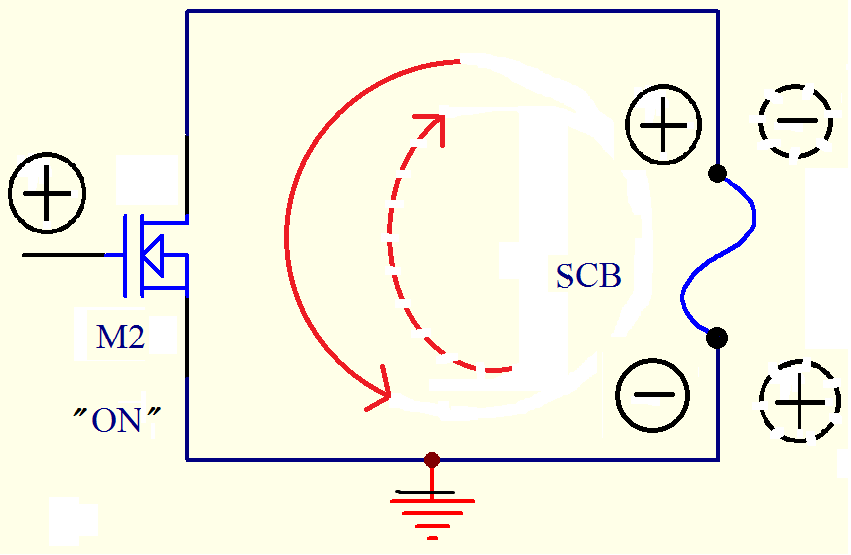

2.在系统加电但未发点火命令时,M1关断,M2导通,CO已充电完成。此时SCB不管感受到正向ESD/EMI,还是负向ESD/EMI,均会通过导通的M2强泄放掉,如下图5所示:

图5

由于M2是一个导通电阻约60mΩ的管子,因而能承受约50A的非重复浪涌电流,因而能有效地保护1Ω/3Ω的SCB免受ESD/EMI影响。

03

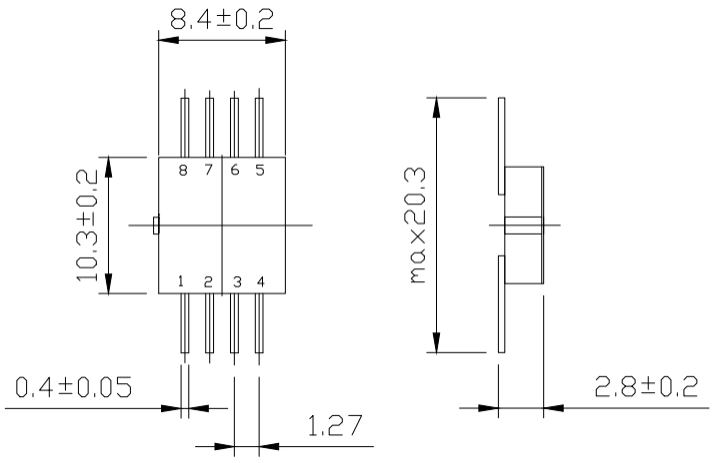

封装形式及引出端功能 3.1 采用F08-04B 紫瓷扁平封装,封装尺寸如图 6所示。

图 6 F08-04B封装尺寸图

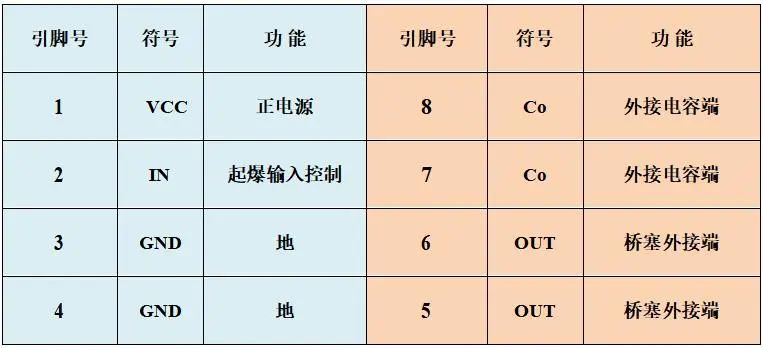

3.2 引出端功能如下:

04

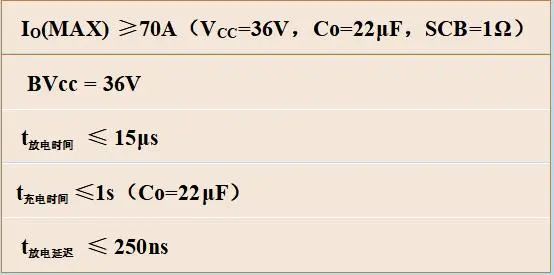

绝对最大额定值

05

电特性

除非另有规定外,VCC=15V,CO=68μF,SCB阻值为1Ω,TA=25℃

06

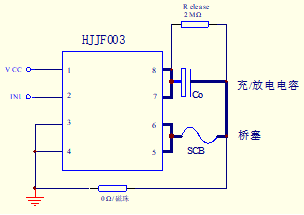

典型应用原理图

图7 HJJF003典型应用

应用注意事项:

a.为消除寄生电感对放电能量的损失,充/放电电容、桥塞应尽可能靠近器件排布、互连线尽可能短且粗;

b.为了防止快速放电GND噪声对输入信号的影响,在充/放电电容与桥塞公共点到电源地之间,应考虑0Ω电阻;

c. VCC端不用做电源旁路;

d.器件可重复做实验,但是一定要留够足够的充电时间,确保Co完全充饱,否则会影响二次激发效果。

e.放电信号脉冲宽度一定要≥200μs,且上升沿要≤200ns,否则内部的P-MOS管儿瞬时导通特性会变差,进而影响激发效果。

f. SCB一般由高掺杂的多晶硅组成,其电阻率上升较为缓慢,且在达到约800K时,电阻率就开始下降。当有电流通过时,SCB中心区域会快速升温,随着负阻效应的作用,电阻值降低,电流的路径集中于低阻区域,温度进一步升高,这一作用使得高温区域迅速融化。温度继续升高时中心区域开始汽化,大量热量通过载流子扩散和热辐射向四周发射。随着电离的增强,电阻变小,最后形成一个较强的高温等离子层,产生高温等离子体辐射放电,从而引爆装载的药剂。

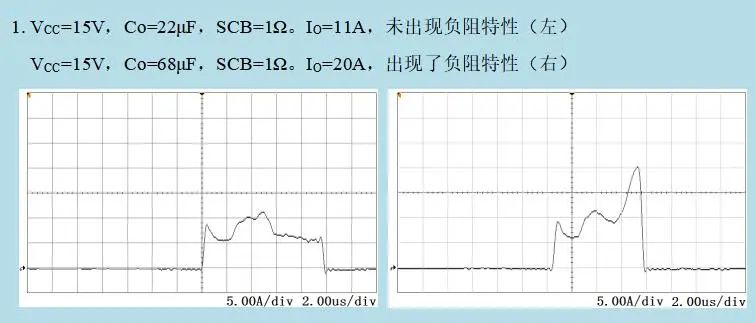

g. 根据电容放电能量公式E=(C×U2)÷2,若VCC较小时,Co应选用容值较大的电容,便于使桥塞在起爆时有充足能量进入负阻态。

07

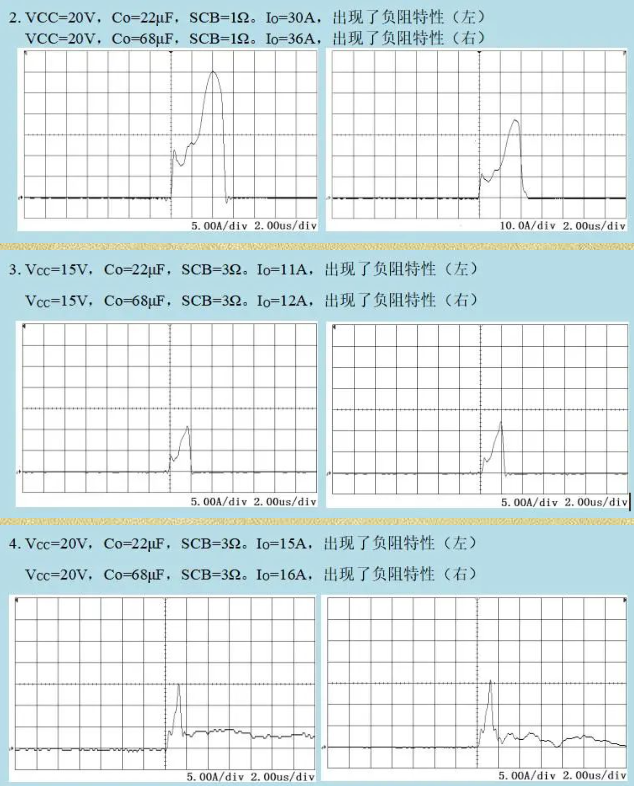

典型应用数据

08

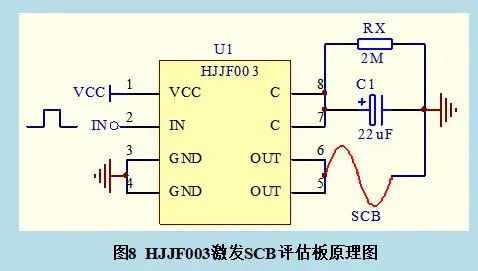

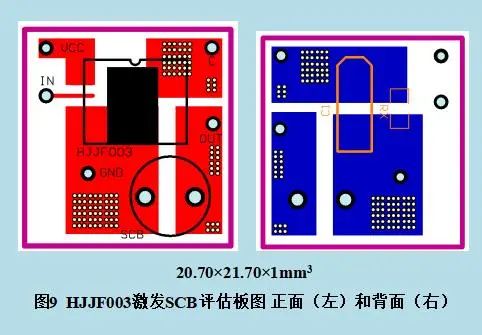

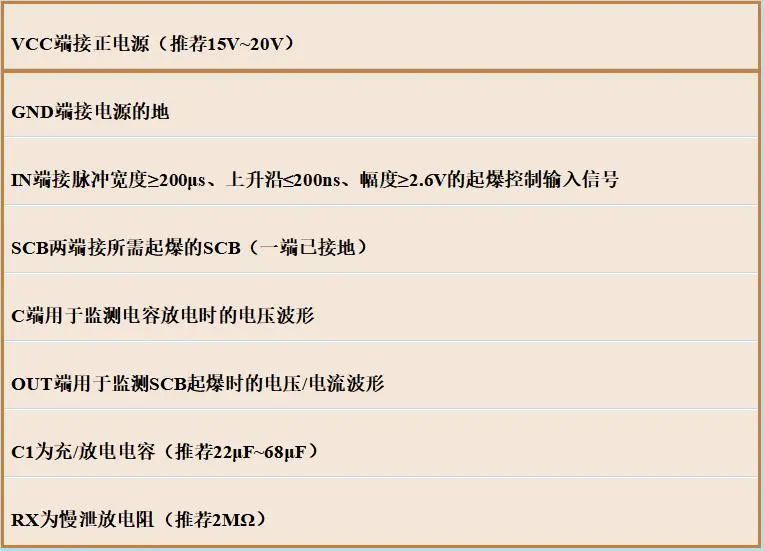

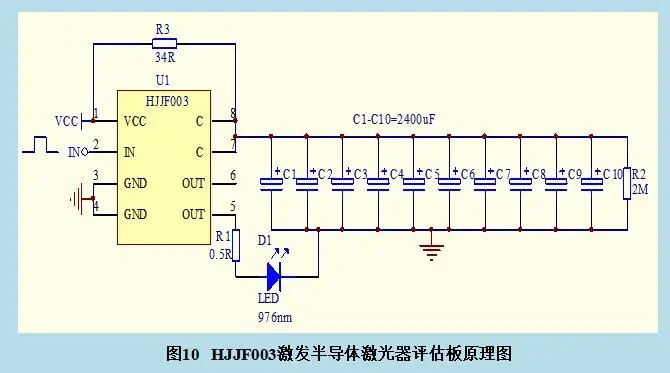

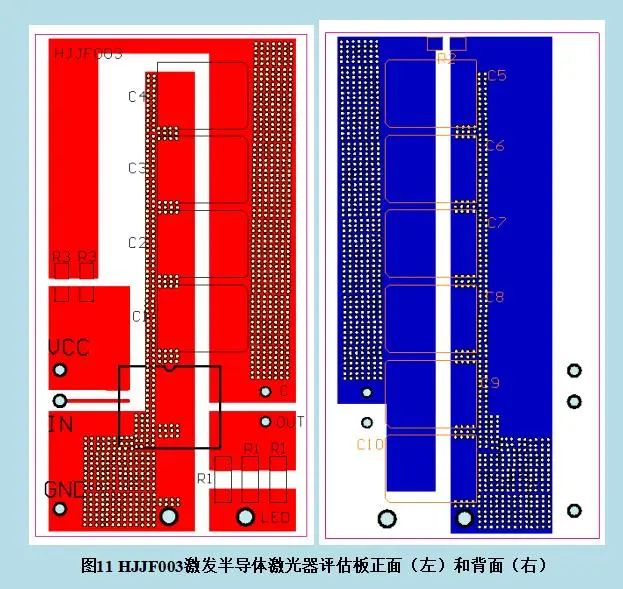

评估板

1.SCB激发单元

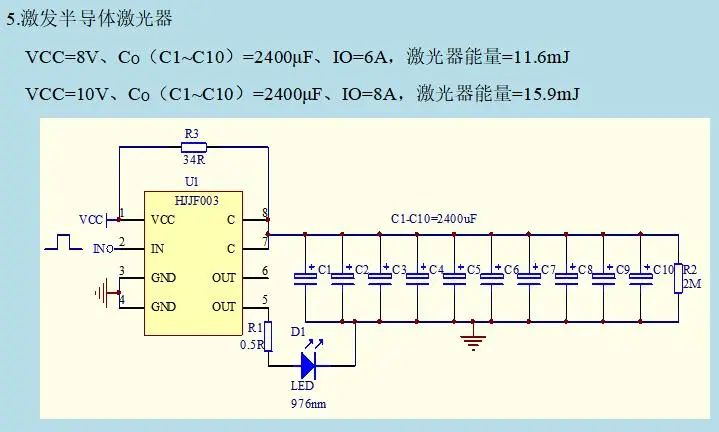

2.半导体激光器激发单元

发布评论请先 登录

相关推荐

点火器的种类及其特点介绍 电子点火器与传统点火器的比较

半导体测试的种类与技巧

半导体光增益与放大特性

中国半导体的镜鉴之路

第六届意法半导体工业峰会2024

p型半导体和n型半导体区别是什么

信号发生器怎么控制点火线圈

喜讯 | MDD辰达半导体荣获蓝点奖“最具投资价值奖”

STM8S003外部干扰,频繁复位重启怎么解决?

新一代半导体桥点火技术的微观世界——高速拍摄揭秘

HJJF003半导体桥塞点火/起爆激发单元

HJJF003半导体桥塞点火/起爆激发单元

评论