来源:《半导体芯科技》期刊

半导体制造商如今拥有的新设备可达到最佳晶圆良率,这种新设备的兆声波系统应用了空间交变相位移(SAPS)和时序能激气穴震荡(TEBO)技术。

半导体芯片的特征尺寸正快速缩小。动态随机存取存储器(DRAM)制造商现在正在生产12纳米级16GB芯片,电容器纵横比为60:1。NAND结构达到232层,蚀刻纵横比更大。而逻辑电路正向3纳米节点全环绕栅极(GAA)晶体管的第一阶段迈进。

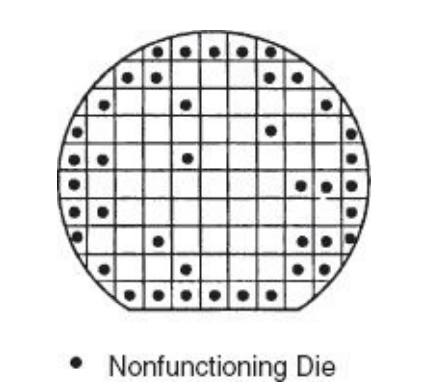

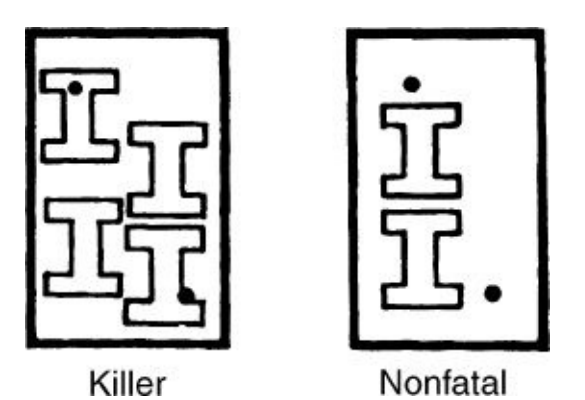

随着结构尺寸越来越小,工艺技术变得更具挑战性,去除污染和随机缺陷变得极其困难。当特征尺寸和薄膜厚度达到10纳米(100埃)级时,即使是1纳米(10埃)微粒也可能成为导致晶体管失效的致命缺陷。随着芯片特征尺寸不断降低至10纳米以下,如何去除微粒及其它污染物质以获得理想良率,将是半导体制造商所面临的一项重大技术挑战。

随着结构尺寸越来越小,工艺技术变得更具挑战性,去除污染和随机缺陷变得极其困难。当特征尺寸和薄膜厚度达到10纳米(100埃)级时,即使是1纳米(10埃)微粒也可能成为导致晶体管失效的致命缺陷。随着芯片特征尺寸不断降低至10纳米以下,如何去除微粒及其它污染物质以获得理想良率,将是半导体制造商所面临的一项重大技术挑战。

当今的先进技术使得特征尺寸更小更精细,传统的颗粒去除清洗技术因此面临着挑战。具体来说,喷淋清洗技术的压力水平太强;物理力会损坏晶体管和电容器结构的表面特征,有可能使其脱离晶圆。喷淋技术也无法深入到纵横比很高的沟槽中。

由于能量不能均匀传递到深层结构中,传统兆声波清洗很难处理小型深沟槽。传统的兆声波技术不能保证整个晶圆的均匀表面覆盖,这往往会导致某些晶圆区域的清洗不足。这会导致良率下降。这些工艺还会造成表面粗糙、材料损耗等问题,当1埃对芯片性能至关重要时,这些问题就会极大地影响这些先进器件的性能。本质上,兆声波晶圆清洗方法和传统清洗方法的水平都已达到极限,在不损坏芯片上的特征的情况下,不再能够去除极其微小的致命缺陷。

目前,从图形化半导体中去除颗粒的方法正逐步成为一门重点科学。随着芯片特征尺寸不断缩小,并向立体化发展,使用刷洗设备、喷淋设备、超声波和兆声波进行强力清洗的方式逐渐得以改良,以免损坏芯片结构。新的单晶圆清洗工艺技术解决了清洗目前和下一代半导体芯片上图案结构的关键问题。

新一代清洗技术

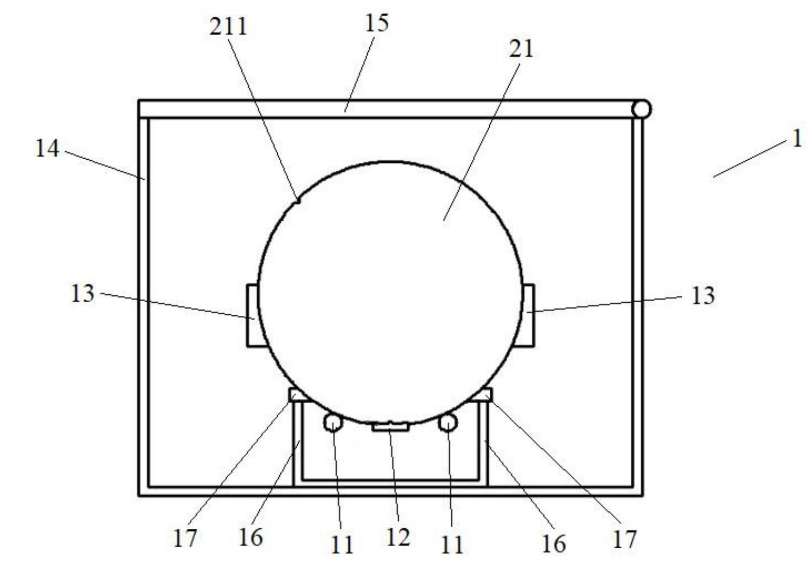

为了解决半导体设备制造商面临的清洗挑战,盛美开发了Smart Megasonix™——一套更具智能和创新性的单晶圆湿法清洗技术,可以应用于现有或未来工艺节点,在不影响器件特性的情况下,通过一系列工艺步骤,达到更加彻底、全面的清洗。这些专有技术可以控制兆声波清洗的功率强度和分布范围。

公司已经开发了两项关键技术,以增强兆声波清洗系统的清洗能力。第一项是空间交变相位移(SAPS™)晶圆清洗技术。SAPS技术是一种先进的兆声波工艺,这种工艺利用兆声波传感器与晶圆间的空隙,使兆声波相位发生变化。SAPS技术可以在晶圆旋转的同时移动或倾斜传感器,即使晶圆翘曲,也能在晶圆的每一点上均匀提供兆声波能量。

这确保了最佳的能量输送,当与适当的稀释化学成分相结合时,为去除晶圆缺陷创造了合适的环境。SAPS技术精确度高,可有效地提高颗粒去除过程中的传质速率,及系统中颗粒去除效率。应用SAPS技术可以提高生产效率,及颗粒去除效率,从而提高产能,降低晶圆生产成本。

兆声波技术的第二项创新技术是时序能激气穴震荡(TEBO™)技术。传统兆声波技术通过空化效应来产生气泡,这些气泡能够有效进行清洗。在传统系统中,这些气泡可能发生内爆或破裂,进而破坏精细图形。采用TEBO技术后,空化效应更加稳定,不会产生气泡内爆或破裂。从而能够在不损坏DRAM的高纵横比电容器和3D NAND的高纵横比沟槽和孔洞等精细图形的前提下,成功地去除缺陷。该技术还能去除先进的鳍式场效晶体管(FinFET)和GAA结构的缺陷。随着芯片特征尺寸不断变小,纵横比不断增大,去除蚀刻、光刻胶的残余物和化学机械研磨颗粒的挑战变得更大。晶圆特征更易被破坏,原子作用力更大,这导致晶圆表面的瑕疵更难去除。对于先进节点的加工而言,需要采用不会损坏关键特征的新型清洁化学成分和机械方法来去除缺陷。随着SAPS和TEBO技术被引入兆声波系统,半导体制造商如今在力争实现最佳的晶圆良率方面拥有了新的工具。

审核编辑:汤梓红

-

半导体

+关注

关注

334文章

27253浏览量

217924 -

DRAM

+关注

关注

40文章

2309浏览量

183420 -

晶圆

+关注

关注

52文章

4884浏览量

127918 -

清洗技术

+关注

关注

0文章

17浏览量

6490

发布评论请先 登录

相关推荐

台积电进入“晶圆代工2.0”,市场规模翻倍,押注先进封测技术

浅谈影响晶圆分选良率的因素(1)

芯德科技扬州晶圆级芯粒先进封装基地项目封顶

半导体工艺之生产力和工艺良率

先进的清洗技术如何助力先进节点实现最佳晶圆良率

先进的清洗技术如何助力先进节点实现最佳晶圆良率

评论