1 系统设计

1.1 设计要求

1.1.1 设计任务

设计并制作一台数字日历。

1.1.2 性能指标要求

① 用EDA实训仪的I/O设备和PLD芯片实现数字日历的设计。

② 数字日历能够显示年、月、日、时、分和秒。

③ 用EDA实训仪上的8只八段数码管分两屏分别显示年、月、日和时、分、秒,即在一定时间段内显示年、月、日(如20080101),然后在另一时间段内显示时、分、秒(如00123625),两个时间段能自动倒换。

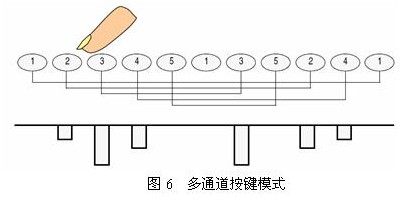

④ 数字日历具有复位和校准年、月、日、时、分、秒的按钮,但校年和校时同用一个按钮,即在显示年、月、日时用此按钮校年,在显示时、分、秒时则用此按钮校时,依此类推。

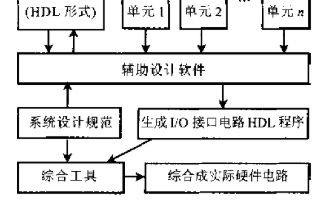

1.2 设计思路及设计框图

1.2.1设计思路

根据万年历的实际特点,本设计最基础的部分就是24小时计数器部分。它由两片60进制计数器和一片24进制计数器构成,输入clk为1Hz(秒)的时钟,经过60分频后产生1分钟的时钟信号,再经过60分频后,产生1小时的时钟信号,最后进行24分频,得到1天的脉冲送cout输出。

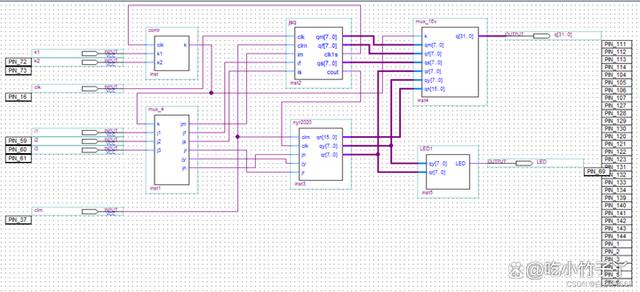

当计时器设计完成后,可以为它产生一个元件符号,作为万年历设计的基本元件。除了基础的计时器模块(day),万年历电路还包括年月日模块(nyr2013),控制模块(contr),校时选择模块(mux_4)和显示选择模块(mux_16)。

在基础计数器完成的天计数脉冲完成之后,送入年月日模块中进入进一步的计数,最终进一步得到日,月,年的计数结果。由于设计要求8只八段数码管分两屏分别显示年、月、日和时、分、秒,所以控制模块便通过控制信号k来控制数码管是显示时、分、秒还是年、月、日,或者自动轮流显示。

相应的显示选择模块也是通过k信号来控制是选择将计时器模块的时、分、秒结果信号,还是将年月日模块的年、月、日结果信号送到数码管显示。设计还要求数字日历具有复位和校准年、月、日、时、分、秒的按钮,但校年和校时同用一个按钮,所以应运而生有校时选择模块,同样也是在k信号的控制下,对j1、j2、j3这三个公共校时按钮所产生的校时信号选择是送到计时器模块的校时端,还是年月日模块的校年端,从而实现校时选择功能。以上就是大体的设计思路,各个模块相辅相成,最终满足设计要求。

1.2.2总体设计框图

2 各个模块程序的设计

2.1 控制模块contr的设计

控制模块的元件符号如上图所示。由于设计要求8只八段数码管分两屏分别显示年、月、日和时、分、秒,因此需要通过在控制模块中通过分频电路来实现,在此模块中采用了一个16秒的分频电路,占空比为50%,即8秒高电平,8秒低电平,因此很容易实现万年历年、月、日和时、分、秒的自动切换显示功能。其中clk是1秒脉冲信号输入端,k1和k2是控制输入端:当{k1,k2}=00或11时即进入自动切换显示模式,当{k1,k2}=01时,数码管仅显示时、分、秒,当{k1,k2}=10时,数码管仅显示年、月、日。{k1,k2}的值决定了控制信号k的输出。

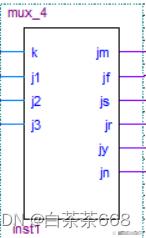

2.2 校时选择模块mux_4v的设计

校时选择模块的元件符号如上图所示。k是控制信号的输入端,由控制模块输出,控制对j1、j2、j3这三个公共校时按钮所产生的校时信号选择是送到计时器模块的校时端,还是年月日模块的校年端,其中当k=0时,将j1、j2、j3产生的信号送到计时器模块的jm(校秒)、jf(校分)、js(校时)端;其中当k=1时,将j1、j2、j3产生的信号送到年月日模块的jr(校日)、jy(校月)、jn(校年)端,从而校年和校时可以同用一组按钮。

2.3 年月日模块nyr2020的设计

年月日模块的元件符号如上图所示。k是控制信号的输入端,由控制模块输出。其中,clrn是异步清除输入端,低电平有效;clk是时钟输入端,上升沿有效;jn、jy、jr分别是校年、校月。校日的输入端,qn、qy、qr则分别是年、月、日的状态输出端。

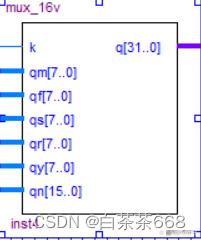

2.4 显示选择模块mux_16v的设计

显示选择模块的元件符号如上图所示。k是控制信号的输入端,由控制模块输出。因为控制模块决定了数码管有多中不同的显示模式,所以当k=0时,将计时器模块输出的qm、qf、qs的状态信号送到数码管显示;而当k=1时,将年月日模块输出的qr、qy、qn的状态信号送到数码管显示。其中我加入了扩展功能,在数码管只显示时、分、秒的时候,有2个数码管并没有数值显示,因此我将其中一个数码管选择显示A或F,当时间在12点之前是显示A,代表上午(AM),当时间在12点之后时显示F,代表下午(FM)。

2.5 计时器模块jsq的设计

计时器模块的元件符号如上图所示。clk是秒时钟输入端;clrn是清除输入端,低电平有效;jm、jf、js分别是校秒、校分、校时的输入端,下降沿有效;qm、qf、qs分别是秒、分、时的输出端;day是“天”脉冲输出端。计时器模块是万年历电路最基础的组成部分。它由分频器、两片60进制计数器和一片24进制计数器构成,具体构成如下图:

2.6 LED显示模块LED1的设计(扩展功能的实现)

qy和qr和nyr模块中的输出相连,LED是输出,在实验时用一个LED灯把管脚锁住锁住,每到节日来的脉冲便会使LED灯亮。加入的扩展功能,能让万年历在节日的时候能亮一盏LED灯,比如在元旦节、情人节一些比较重要的节日,起到提醒的作用,也可以从而使万年历的显示内容更为完整。

3 调试过程

把写好的程序经验证仿真确认无误并且锁定好管脚后经下载端口下载到EDA实训仪上,通过实际操作来验证是否能实现相应功能。

4 功能测试

4.1 测试仪器与设备

① EDA实训仪 1台

② 电脑 1台

4.2 性能指标测试

① 数字日历能够正确显示年、月、日、时、分和秒。

② EDA实训仪上的8只八段数码管能够分两屏分别显示年、月、日和时、分、秒。

③ EDA实训仪上的8只八段数码管能够自动切换显示年、月、日和时、分、秒。

④ 数字日历具有复位和校准年、月、日、时、分、秒的按钮,且校年和校时同用一个按钮就能实现。

4.3 误差分析

由于在程序编写的过程中经过了反复的思考和检查,因此在下载到硬件电路后,所有基础功能都达到了设计要求,并且自己的扩展功能也成功的实现。

部分程序清单

1、计算器模块(jsq)

(1)分频器

module fenpin(clk,cout);

input clk;

output reg cout;

reg[24:0]qq;

always @(posedge clk)

begin

if(qq==19999999) begin qq=0;cout=1;end

else begin qq=qq+1;cout=0;end

end

endmodule

(2)cnt60

module cnt60(clk,clrn,j,q,cout);

input clrn,clk,j;

output reg[7:0]q;

output reg cout;

always @(posedge clk^j or negedge clrn)

begin

if(~clrn) q=0;

else begin

if(q=='h59) q=0;

else q=q+1;

if(q[3:0]=='ha) begin q[3:0]=0; q[7:4]=q[7:4]+1;end

if(q=='h59) cout=1;

else cout=0;

end

end

endmodule

-

分频器

+关注

关注

43文章

447浏览量

49912 -

数码管

+关注

关注

32文章

1882浏览量

91124 -

LED显示

+关注

关注

0文章

361浏览量

38039 -

计时器

+关注

关注

1文章

420浏览量

32712 -

PLD芯片

+关注

关注

0文章

35浏览量

17815

发布评论请先 登录

相关推荐

如何利用I/O设备和PLD芯片实现数字日历的设计?

如何利用I/O设备和PLD芯片实现数字日历的设计?

评论