SDRAM是现代计算机中使用的一种主要内存类型。它具有高速和大容量的特点,能够满足高要求的性能和数据存储需求。然而,SDRAM的高速也意味着在设计中需要严格遵循走线等长规则。这篇文章将介绍SDRAM走线等长规则,以及为什么需要遵守这些规则,以及如何应用这些规则来确保设计的正确性和可靠性。

一、SDRAM概述

SDRAM是同步动态随机存储器的缩写,它是动态随机存储器(DRAM)的一种。它的寄存器和内部电路是与系统时钟同步的,这意味着处理器和SDRAM之间的通信是高度协调的。SDRAM的存储单元由存储器芯片和SDRAM控制器共同管理,用于将数据存储在处理器可以访问的位置。

SDRAM有多种标准,包括DDR(Double Data Rate)、DDR2、DDR3和DDR4。每个标准都具有不同的物理规格和数据传输速率。DDR4是现代计算机中使用的最新型号,它具有更高的频率和更大的容量。

二、SDRAM走线等长规则简介

SDRAM设计中最基本的规则之一是走线等长规则,这意味着处理器和SDRAM之间的信号路径应该尽可能的相等。这是因为互联线路的长度和信号传输速度之间存在密切的关系。较长的线路意味着较高的延迟和更慢的信号传输速度,这可能导致信号在到达目的地之前过早失效或变形。

如何实现SDRAM走线等长规则?

首先,需要设计者进行精确的电路布局,确保处理器和SDRAM之间的信号的物理延迟相等。这意味着信号线的长度必须尽可能的相同,并且需要使信号线的路径尽可能的平直和短。

其次,需要严格控制布线目标信噪比。布线时使用低噪声的电源和地线,同时还需要使用屏蔽和滤波器来降低噪声和射频干扰的影响。这些措施有助于保持信噪比和信号完整性,从而确保信号在SDRAM和处理器之间传输的清晰和准确。

最后,对于DDR4这样的高带宽SDRAM,处理器和存储器模块之间需要有一个DDRx时钟总线。设计时必须使时钟和信号路线尽可能的短,以确保数据的传输速率和时序正确。

三、为什么需要遵守SDRAM走线等长规则?

严格遵守SDRAM走线等长规则是非常重要的,因为它可以保证信号的准确性和稳定性。违反规则可能导致信号失真和传输错误,从而导致系统性能下降或系统崩溃。由于SDRAM是大容量存储器,它通常用于存储关键数据和代码。任何数据损坏或错误都可能导致崩溃或安全漏洞,因此必须保证数据的准确性和可靠性。

另外,符合SDRAM走线等长规则还可以提高系统的稳定性和可靠性。由于SDRAM是高速存储器,它需要处理大量数据,并且必须与其他系统组件进行高速通信。如果SDRAM走线不平衡或长度不相等,可能会导致数据传输错误,从而破坏系统的完整性。如果数据被破坏或丢失,可能需要重新启动整个系统,从而导致时间和资源的浪费。

四、结语

本文介绍了SDRAM走线等长规则及其重要性。SDRAM是现代计算机系统中使用的重要内存类型之一,因此需要进行严格的设计和布线。精确和符合规则的布线可以确保SDRAM信号的准确性和可靠性,保证系统的高性能和稳定性。未来,我们需要继续探索和发展SDRAM的技术,以满足不断提高的计算机性能和存储需求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

处理器

+关注

关注

68文章

19448浏览量

231359 -

SDRAM

+关注

关注

7文章

433浏览量

55409 -

存储器

+关注

关注

38文章

7533浏览量

164450

发布评论请先 登录

相关推荐

pcb设计中常见的走线等长要求是什么

1、在做 PCB 设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形

使用SDRAM外设的时候,数据线、地址线、控制线是单独等长还是所有类型的线路一起等长?

请问使用SDRAM外设的时候,数据线、地址线、控制线是单独等长还是所有类型的线路一起等长?

LT

发表于 04-10 06:37

请问Altium designer中单线等长和差分等长以及保持原间距走线和等间距走线该怎么用?

跪求Altium designer中单线等长和差分等长以及保持原间距走线和等间距走线是怎么使用的

发表于 09-25 05:35

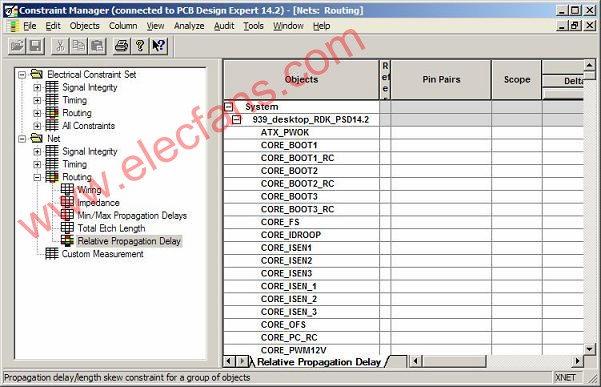

教您在Allegro中设置走线等长进阶

对于简单走线等长在以前文档中都有涉及这里不再复述了,下面内容将给大家介绍一下有关Xnet等长的设置问题, 如现在主板DD

发表于 06-28 09:38

•2.9w次阅读

PCB设计做等长走线的目的是什么

在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。 由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高

PCB设计中如何实现等长走线

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随

sdram走线等长规则

sdram走线等长规则

评论