PCB走线是PCB设计过程中重要的一步。不恰当的走线会影响电路的性能,甚至导致电路不稳定甚至不工作。因此,正确的PCB走线非常重要。

首先,PCB走线应该遵循以下原则:

1. 短路:走线应尽可能地短,以减少信号的传输时间和噪音的影响。短路也有助于减少信号衰减,并降低PCB的成本和尺寸。

2. 阻抗匹配:在高速时钟和数据信号中,保证信号质量至关重要。因此,走线的阻抗应与板上线路的阻抗匹配,以保证信号质量。

3. 信号分层:为避免信号干扰,PCB的各层应穿插使用VCC、GND、信号层。供电层和地层应尽可能地接近进行屏蔽。

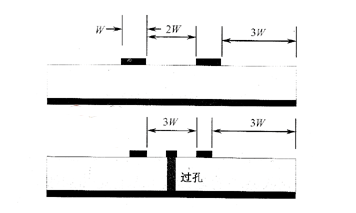

4. 避免信号环路:为避免信号回流和差分信号的相互干扰,信号线应布置为两线之间具有其他信号线、接地或VCC。

5. 隔离高频信号:高频信号对电路干扰大,因此对于高频信号线,需要做好隔热处理来保证信号质量。

有了这些原则,我们可以讨论一下具体的走线策略:

1. 低电平信号:低电平信号可以通过走线缩短路径来避免噪声的干扰。我们可以优先考虑布局更加紧凑的区域,如中央区域,来布置低电平信号线路。

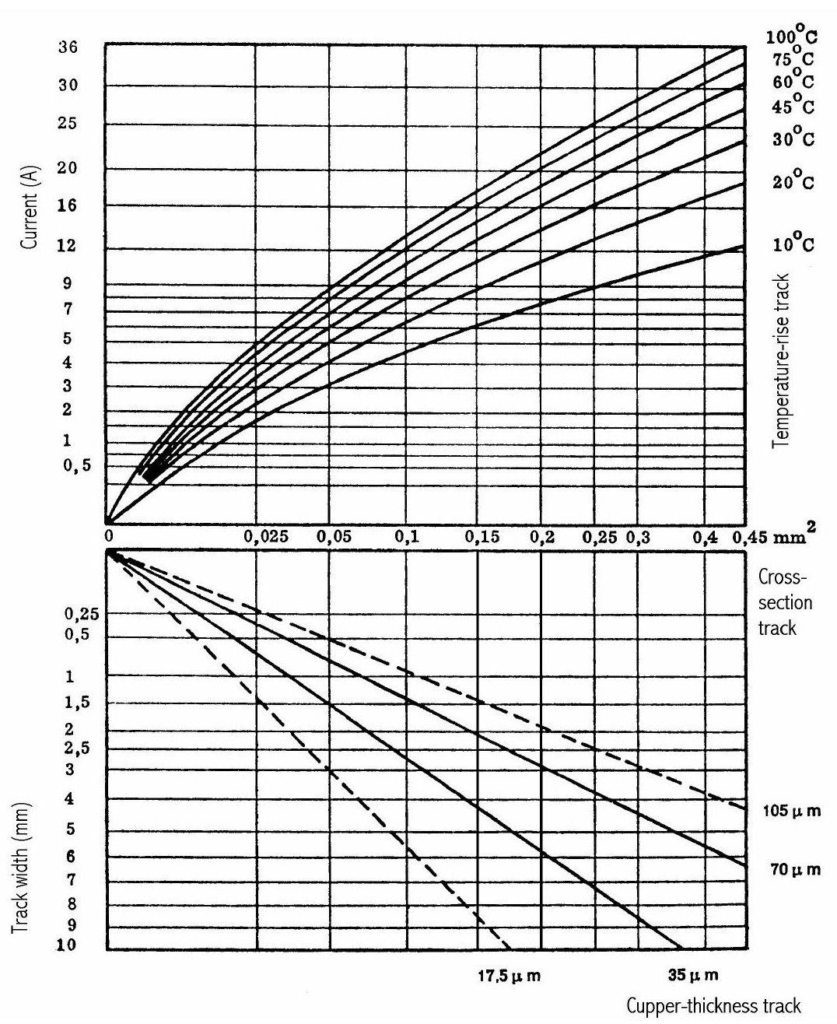

在进行走线时,还应注意减少线路的弯折,并保证线宽合适。线宽太细会导致信号衰减,而线宽太宽会导致信号反射。同时,还应注意在布局时预留足够的空间,预留修订余地。

2. 复杂的中速信号:复杂的中速信号(1 Mhz到100 Mhz)可以采用分层式布局。可以将已有的生产工艺中细分为四层,两层用于地和供电,另外两层用于信号层,同时也不会造成射频噪声干扰。

在进行走线时,应优先布置水平、直线和点线,优先使用不需要插接头、延长线的走线方案。如必要,也可采用弯曲线路,但要保持光滑和不过分弯曲。

3. 高速信号(>100 Mhz):布局时应将高速信号隔离开,同时考虑作为差分对布置,并应用分层式布局。针对较高的阻抗匹配要求,仅使用铜蚀技术的PCB传输线需要使用锗或P型半导体进行芯片层匹配。

在进行走线时,应优先选用线宽最小的线路,引脚输出中间无线直线优先用差分走线方式。跨线连接时,不能将信号线交叉,而应采用穿孔、拆插、回路或引出等方式来实现信号的传递。

综上所述,PCB走线是PCB设计的重要环节,需要遵循一定的原则和策略。PCB走线可以通过在线分析,并结合仿真和实测进行优化和完善。PCB走线的正确性将直接影响电路的性能,因此,这段时间的投入必将为五分之一的时间的工程提供最好的保障。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4335文章

23247浏览量

402277 -

阻抗

+关注

关注

17文章

962浏览量

46489 -

高频信号

+关注

关注

1文章

141浏览量

21825

发布评论请先 登录

相关推荐

PCB layout中的走线设计

PCB layout需要丰富的经验和扎实的理论基础支持,还要多踩几个坑,多做几个仿真加深对走线的理解,才能形成闭环的走线设计。

发表于 07-19 15:10

•3976次阅读

PCB走线的设计细节详解

尽可能的宽。音频输出的所有元器件应该尽可能靠近耳机插座。建议把这些与音频有关的元器件和走线放在一起,并尽可能的与系统音频输出在PCB的同一部分。尽量避免从其他的信号耦合噪声。音频输出走

发表于 04-13 16:09

PCB走线辟谣总结,究竟应该怎么找拐角

现在但凡打开 SoC 原厂的 PCB Layout Guide,都会提及到高速信号的走线的拐角角度问题,都会说高速信号不要以直角走线,要以

PCB直角走线的影响

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布线在高速 PCB

发表于 02-11 15:24

•30次下载

pcb应该如何走线,为什么

pcb应该如何走线,为什么

评论