节通过硬件描述语言Verilog HDL对二十进制编码器的描述,介绍Verilog HDL程序的基本结构及特点。

二十进制编码器及Verilog HDL描述

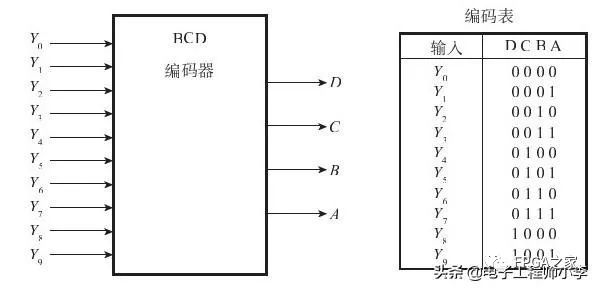

二十进制编码器是数字电路中常用的电路单元,它的输入是代表0~9这10个输入端的状态信息。输入信号为高电平时,输出相应的BCD码,因此也称为10线4线编码器。其功能表及电路符号如图3-1所示。

图3-1二十进制编码器

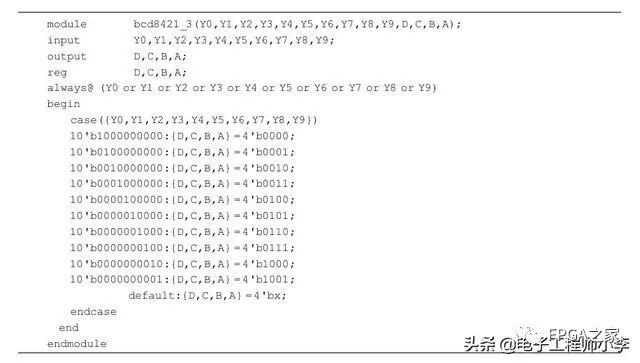

【例3-1】利用Verilog HDL对二十进制编码器进行设计。

Verilog HDL程序的基本构成

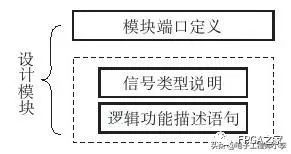

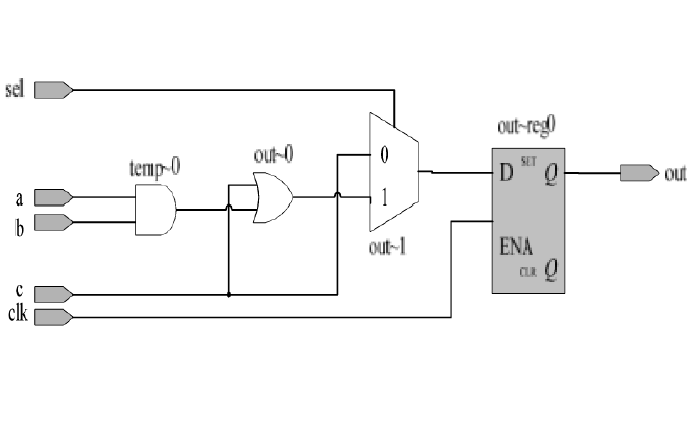

从例3-1可以看出,一个完整的Verilog HDL程序由3个基本部分构成,分别是:模块端口定义部分、信号类型说明部分和逻辑功能描述语句部分。其结构图如3-2所示。

图3-2Verilog HDL程序基本结构

模块端口定义部分

对于硬件描述语言来说,一个程序代表了一个具有某种逻辑功能的电路,模块端口定义部分描述了该电路的接口部分的信息,即输入输出信号的信息。

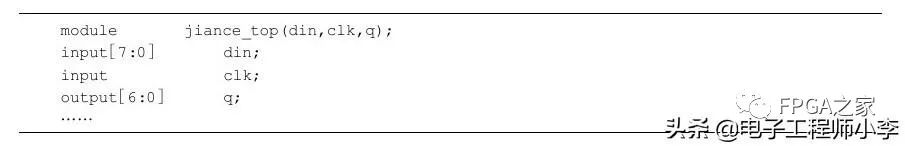

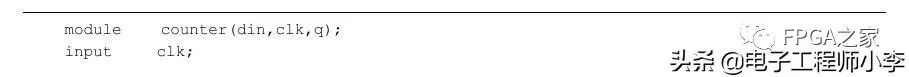

模块端口定义部分的语法结构如下:

module模块名(端口信号1,端口信号2,端口信号3,端口信号4,……);

input[width:0]端口信号1,端口信号3,……;

output[width:0]端口信号2,端口信号4,……;

程序以关键词module引导,模块名是设计者对于设计的电路所取的名字,在模块端口定义的第1行列出了所有进出该电路模块的端口信号,在第2行和第3行中定义了各端口信号流动方向。流动方向包括输入(input)、输出(output)和双向(inout),[width:0]表示信号的位宽,如果位宽没有特别说明,则系统默认为1位宽度。

【例3-2】模块端口定义举例。

信号类型说明部分

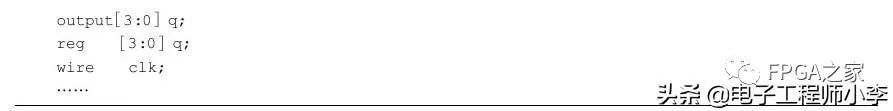

在Verilog HDL语法中,信号共有两种数据类型,分别为:网线类型(net型)和寄存器类型(register型)。在信号类型说明部分除了要对输入/输出端口的信号类型进行说明之外,还要对程序中定义的中间量的数据类型进行说明。

信号类型说明部分的语法结构如下:

wire[width:0]信号1,信号2,……;

reg[width:0]信号3,信号4,……;

【例3-3】信号类型说明举例。

逻辑功能描述语句部分

逻辑功能描述语句部分对输入/输出信号之间的逻辑关系进行了描述,是Verilog HDL程序设计中最主要的部分,在电路上相当于器件的内部电路结构。在Verilog HDL语言中,常用的逻辑功能描述语句可以分为以下3种:

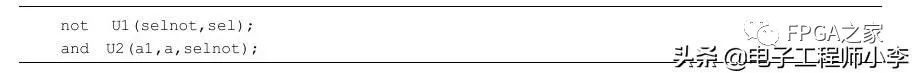

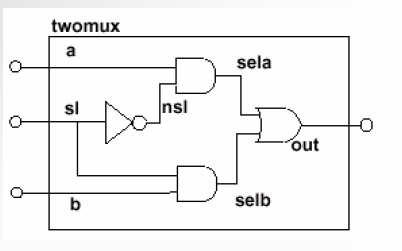

例化语句:调用已进行元件化封装的程序。这种语句常应用于层次化设计的顶层文件设计中。

【例3-4】例化语句举例。

该语句分别调用了一个非门和与门电路模块。

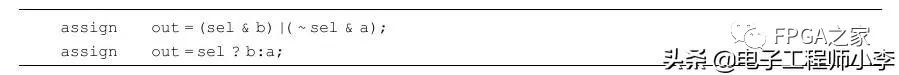

连续赋值语句:描述信号之间简单的赋值关系。在连续赋值语句中,右边表达式使用的操作数无论何时发生变化,右边表达式都重新计算。这类描述通常以关键词assign引导。

【例3-5】连续赋值语句举例。

该语句描述了输出信号与输入信号的赋值关系。

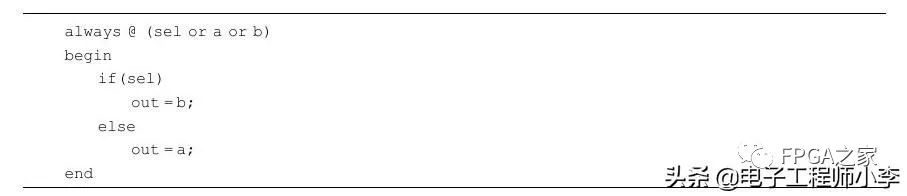

过程语句:以关键词always、initial等关键词引导的语句,描述了一定条件下信号之间的赋值关系。这种变量数据被赋值后,其值保持不变,直到下一次条件具备时对它们重新赋值。

【例3-6】过程语句举例。

与连续赋值语句一样,always和initial也描述了输出信号与输入信号的赋值关系,但是这种赋值往往是一种比较复杂的条件赋值,例如,例3-6就用了if……else语句描述了输出信号与输入信号的条件关系。

-

编码器

+关注

关注

45文章

3584浏览量

134105 -

Verilog

+关注

关注

28文章

1343浏览量

109970 -

HDL

+关注

关注

8文章

327浏览量

47336 -

程序

+关注

关注

116文章

3773浏览量

80830

原文标题:逻辑功能描述语句部分

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Verilog-HDL实践与应用系统设计

什么是Verilog HDL?

Verilog HDL入门教程之Verilog HDL数字系统设计教程

Verilog教程之Verilog HDL程序设计语句和描述方式

二十进制编码器及Verilog HDL描述 Verilog HDL程序的基本结构及特点

二十进制编码器及Verilog HDL描述 Verilog HDL程序的基本结构及特点

评论