首先,想说上拉电阻几乎都是应运三极管电路而生的,但是本文基本上都属于定性的分析,避免对其定量分析,相信即使没有学过三极管晶体电路的同学还是可以基本理解的。

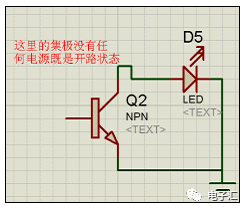

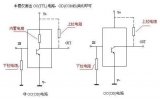

首先还要明确一个术语,所谓开漏(OD),开集(OC)电路就

是场效应管的漏极和三极管的集电极是断开的电路。如下图所示,这里希望大家不要纠结于我这个三极管用的是否正确只是想定性的解释一下什么是开漏(OD)或开集(OC)。

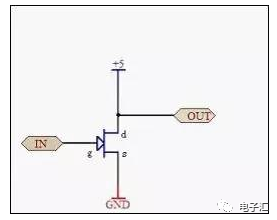

下面通过场效应管的漏极开路门电路的例子简单说明一下上拉电阻:

(1)如果没有上拉电阻(10k),将5V电源直接与场效应管相连。

当管子导通时,管子等效一电阻,大小为1k左右,因此5v电压全部加在此等效电阻上,输出端Vout=5v。

当管子截止时,管子等效电阻很高,可以理解为无穷大,因此5v的电压也全部加在此等效电阻上,Vout=5v。在这两种情况下,输出都为高电平,没有低电平。

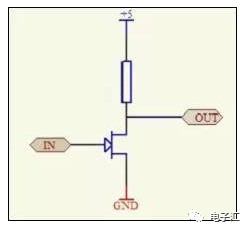

(2)如果有上拉电阻(10k),将5v电源通过此上拉电阻与与场效应管相连。

当管子导通时,管子等效一电阻,大小为1k左右,与上拉电阻串联,输出端电压为加在此等效电阻上的电压,其大小为Vout = 5v *管子等效电阻/(上拉电阻+管子等效电阻)=5v * 1/(10+1)=低电平。

当管子截止时,管子等效电阻很高,可以理解为无穷大,其与上拉电阻串联,输出端电压为加在此等效电阻上的电压,其大小为Vout = 5v *管子等效电阻/(上拉电阻+管子等效电阻)=5v*无穷大/(无穷大+1)=高电平。

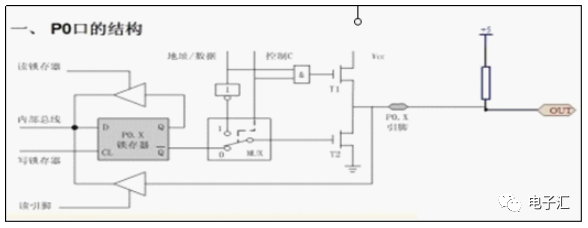

看到这里估计大家基本懂了七八分了吧,但是想必大家肯定还有一个疑问:难道P0口的高低电平输出与实际的输出是相反的吗?呵呵,现在让我们看一下8051单片机P0口的逻辑电路图:

其实,笔者一开始也纠结了很久,还专门查了一下场效应管的书,但是没有任何收获。这里请大家认真看一看P0.x 的D锁存器的输出端吧。没错问题就在这里D锁存器最终输出的是,根据D锁存器的原理,输出在这里经过了一次取反才又输出的,所以其本质是经过了两次取反才得到最终的外部输出的。不知这里跟大家讲清楚了没有。

现在让我们再来总结一下上拉下拉电阻的作用:

1) 上拉就是将不确定的信号通过一个电阻嵌位在高电平!电阻同时起限流作用!下拉同理,下拉就是将不确定的信号通过一个电阻嵌位在低电平!电阻同时起限流作用!

2) 上拉是对器件注入电流,下拉是输出电流。

3) 弱强只是上拉电阻的阻值不同,没有什么严格区分。

4) 对于非集电极(或漏极)开路输出型电路(如普通门电路)提升电流和电压的能力是有限的,上拉电阻的功能主要是为集电极开路输出型电路输出电流通道。

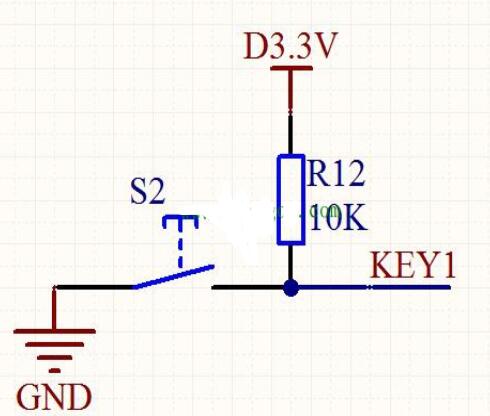

5) 一般作单键触发使用时,如果IC本身没有内接电阻,为了使单键维持在不被触发的状态或是触发后回到原状态,必须在IC外部另接一电阻。

6) 数字电路有三种状态:高电平、低电平、和高阻状态,有些应用场合不希望出现高阻状态,可以通过上拉电阻或下拉电阻的方式使处于稳定状态,具体视设计要求而定!

7) 一般说的是I/O端口,有的可以设置,有的不可以设置,有的是内置,有的是需要外接。

8) 上拉电阻是用来解决总线驱动能力不足时提供电流的。一般说法是拉电流,下拉电阻是用来吸收电流的,也就是我们通常所说的灌电流。

9) 在I/O引脚悬空时,接电阻就是为了防止输入端悬空,从而提高系统的抗干扰能力。减弱外部电流对芯片产生的干扰。

10) 通过上拉或下拉来增加或减小驱动电流。

11) 上下拉电阻改变电平的电位,常用在TTL-CMOS匹配。

12) 上拉电阻可以为OC门或者OD门提供电流。

三、上拉电阻的应用场景

1) 当TTL电路驱动COMS电路时,若TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平值。注:此时上拉电阻连接的电压值应不低于CMOS电路的最低高电压,同时又要考虑TTL电路方电流(如某端口最大输入或输出电流)的影响。

2) OC门或者OD门电路必须加上拉电阻,才能使用。

3) 为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4) 在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻,降低输入阻抗,提供泄荷通路。

5) 芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

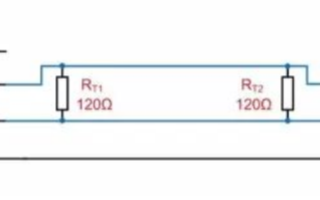

6) 长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

7) 在数字电路中不用的输入脚都要接固定电平,通过1k电阻接高电平或接地。

上拉电阻阻值选择原则

1) 从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2) 从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3) 对于高速电路,过大的上拉电阻可能边沿变平缓。综合考虑以上三点,通常在1k到10k之间选取。对下拉电阻也有类似道理。

4) 对上拉电阻和下拉电阻的选择应结合开关管特性和下级电路的输入特性进行设定,主要需要考虑以下几个因素:

a)驱动能力与功耗的平衡。以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计时应注意两者之间的均衡。

b)下级电路的驱动需求。同样以上拉电阻为例,当输出高电平时,开关管断开,上拉电阻应适当选择以能够向下级电路提供足够的电流。

c)高低电平的设定。不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出正确的电平。以上拉电阻为例,当输出低电平时,开关管导通,上拉电阻和开关管导通电阻分压值应确保在零电平门槛之下。

d)频率特性。以上拉电阻为例,上拉电阻和开关管漏源级之间的电容和下级电路之间的输入电容会形成RC延迟,电阻越大,延迟越大。上拉电阻的设定应考虑电路在这方面的需求。

5) 关于电阻的参数不能一概而定,要看电路其他参数而定,比如通常用在输入脚上的上拉电阻如果是为了抬高峰峰值,就要参考该引脚的内阻来定电阻值的!

6) 一般LED的电流有几个mA就够了,最大不超过20mA,根据这个你就应该可以算出上拉电阻值来了。

7) 对于驱动晶体管,又分为PNP和NPN管两种情况:

a)对于NPN:毫无疑问NPN管是高电平有效的,因此上拉电阻的阻值用2K~20K之间的。具体的大小还要看晶体管的集电极接的是什么负载,对于LED类负载,由于发管电流很小,因此上拉电阻的阻值可以用20k的,但是对于管子的集电极为继电器负载时,由于集电极电流大,因此上拉电阻的阻值最好不要大于4.7K,有时候甚至用2K的。

b)对于PNP管:毫无疑问PNP管是低电平有效的,因此上拉电阻的阻值用100K以上的就行了,且管子的基极必须串接一个1~10K的电阻,阻值的大小要看管子集电极的负载是什么,对于LED类负载,由于发光电流很小,因此基极串接的电阻的阻值可以用20k的,但是对于管子的集电极为继电器负载时,由于集电极电流大,因此基极电阻的阻值最好不要大于4.7K。

8) 对于驱动TTL集成电路,上拉电阻的阻值要用1~10K之间的,有时候电阻太大的话是拉不起来的,因此用的阻值较小。但是对于CMOS集成电路,上拉电阻的阻值就可以用的很大,一般不小于20K,通常用100K的。

9) 关于I2C的上拉电阻:因为I2C接口的输出端是漏极开路或集电极开路,所以必须在接口外接上拉。上拉电阻的取值和I2C总线的频率有关,工作在standard mode时,其典型值为10K。在FAST mode时,为减少时钟上升时间,满足上升时间的要求,一般为1K。电阻的大小对时序有一定影响,对信号的上升时间和下降时间也有影响。总之一般情况下电压在5V时选4.7K左右,3.3V在3.3K左右.这样可加大驱动能力和加速边沿的翻转。

那么关于RS-485上下拉电阻如何选择呢?

RS-485总线广泛应用于通信、工业自动化等领域,在实际应用中,通常会遇到是否需要加上下拉电阻以及加多大的电阻合适的问题,下面我们将对这些问题进行详细的分析。

一、为什么需要加上下拉电阻?

1)当485总线差分电压大于+200mV时,485收发器输出高电平。

2)当485总线差分电压小于-200mV时,485收发器输出低电平。

3)当485总线上的电压在-200mV~+200mV时,485收发器可能输出高电平也可能输出低电平。但一般总处于一种电平状态,若485收发器的输出低电平,这对于UART通信来说是一个起始位,此时通信会不正常。

当485总线处于开路(485收发器与总线断开)或者空闲状态(485收发器全部处于接收状态,总线没有收发器进行驱动)时,485总线的差分电压基本为0,此时总线就处于一个不确定的状态。同时由于目前485芯片为了提高总线上的节点数,输入阻抗设计的比较高,例如输入阻抗为1/4单位阻抗或者1/8单位阻抗(单位阻抗为12kΩ,1/4单位阻抗为48kΩ),在管脚悬空时容易受到电磁干扰。

因此为了防止485总线出现上述情况,通常在485总线上增加上下拉电阻(通常A接上拉电阻,B总线下拉电阻)。若使用隔离RS-485收发模块(例如RSM485PCHT),由于模块内部具有上下拉电阻(对于RSM485PCHT,内部上下拉电阻为24kΩ),因此在模块外部一般不需要增加上下拉电阻。

二、什么情况下需要加上下拉电阻?

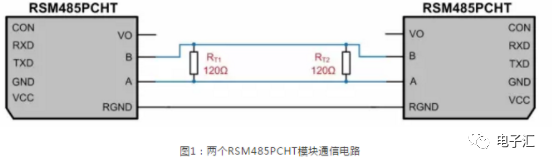

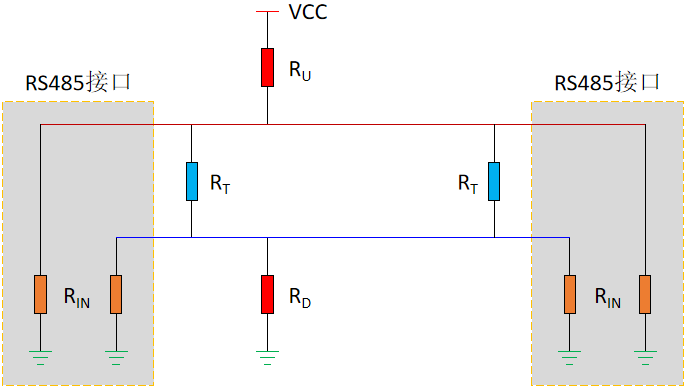

当遇到信号反射问题时,通常会通过增加匹配电阻来避免信号反射,以1对1通信为例,如图1所示。由于485总线通常使用特性阻抗为120Ω的双绞线,因此在485总线的首尾两端增加120Ω终端电阻来避免信号反射问题。

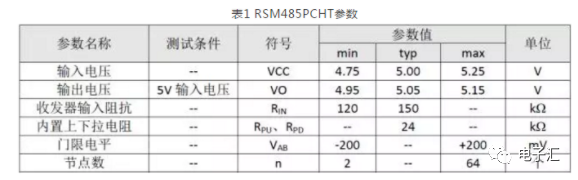

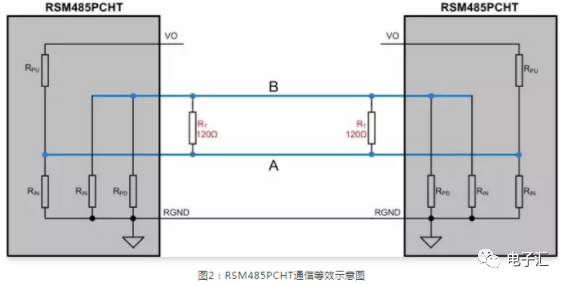

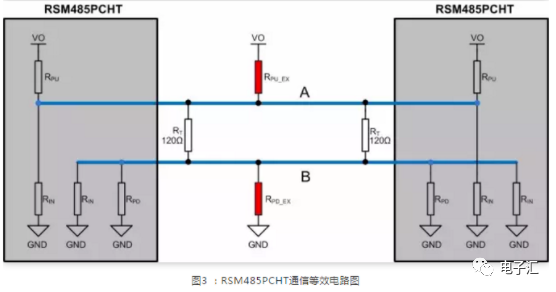

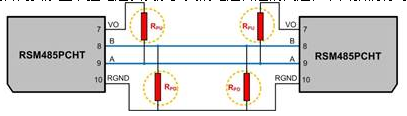

根据RSM485PCHT的具体参数(如表1)可以得到如图2所示等效电路,其中RPU、RPD为模块内部在485总线上加的上下拉电阻,RIN为模块的输入阻抗。

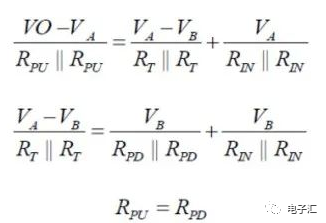

当两个模块都处于接收状态时,可以根据基尔霍夫电流定律对节点A和节点B列出下列公式:

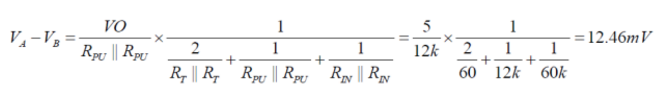

根据上述公式可以计算AB之间的差分电压为:

此时模块已处于不确定状态,模块接收器可能输出为高电平,也可能输出为低电平,这时就需要在模块外部增加上下拉电阻保证模块在空闲时不处于不确定状态。

三、上下拉电阻如何选择?

假设模块的输出电源电压V¬O相同,由于RGND接在一起,因此可以认为模块内部的上拉电阻是并联在一起的,为了方便解释,对图2的电路进行整理,如图3所示,在模块外部增加上下拉电阻可以选择只增加一组,也可以选择在每个模块都增加上下拉电阻,为了解释方便,我们在485总线上增加一组上下拉电阻。

-

三极管

+关注

关注

142文章

3610浏览量

121847 -

上拉电阻

+关注

关注

5文章

359浏览量

30602 -

下拉电阻

+关注

关注

4文章

147浏览量

20523 -

RS485

+关注

关注

39文章

1156浏览量

82286 -

门电路

+关注

关注

7文章

199浏览量

40154

原文标题:关于上下拉电阻的探究以及RS485上下拉电阻如何选择?

文章出处:【微信号:电子汇,微信公众号:电子汇】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

详解RS-485上下拉电阻的选择

RS485总线上下拉电阻的选择

如何选择RS-485上下拉电阻?

RS-485总线知识:什么情况下需要加上下拉电阻?资料下载

详解RS-485上下拉电阻的选择

【RS-485总线】详解RS-485上下拉电阻的选择

上拉下拉电阻的作用和应用场景 RS-485上下拉电阻如何选择

上拉下拉电阻的作用和应用场景 RS-485上下拉电阻如何选择

评论