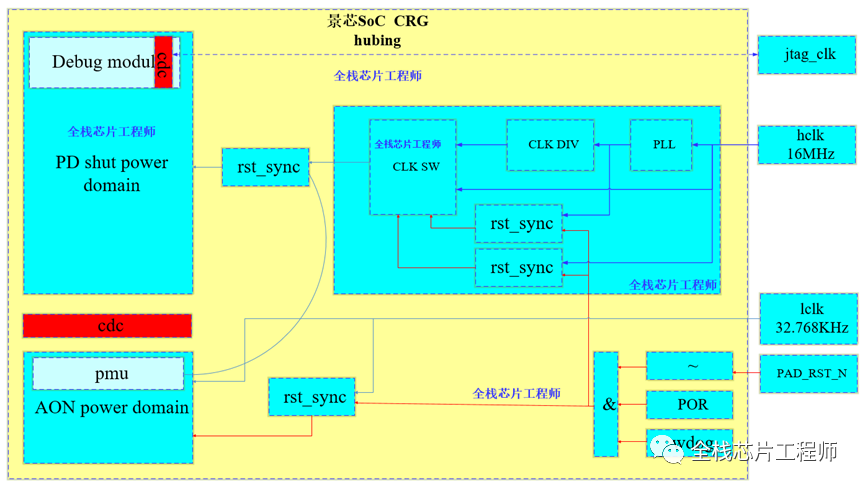

本章节讲解数字前中后端都不得不熟练的clock switch设计。

芯片运行过程中需要时钟切换时,要考虑到是否会产生glitch,小小的glitch有可能导致电路运行的错误。所以时钟切换时需要特别的处理。

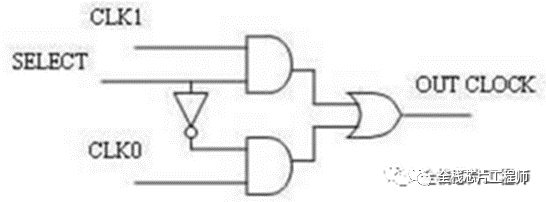

直接使用MUX进行时钟切换或者采用如下电路结构进行时钟切换:

assignoutclock=select?clk1:clk0;assignoutclock= (clk1 & select) | (~select & clk0);

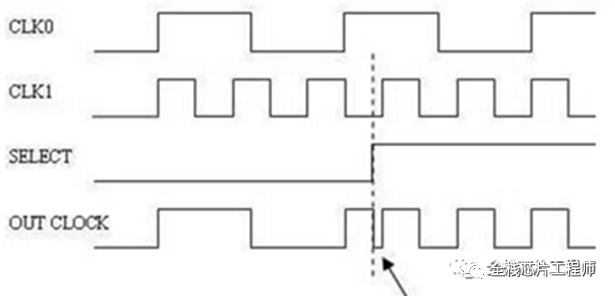

两种做法都会产生时钟切换毛刺的,芯片系统很容易进入亚稳态的情况。

为了解决时钟切换的毛刺问题,对于时钟源分为同步和异步的情况,分为如下两种解决方案:

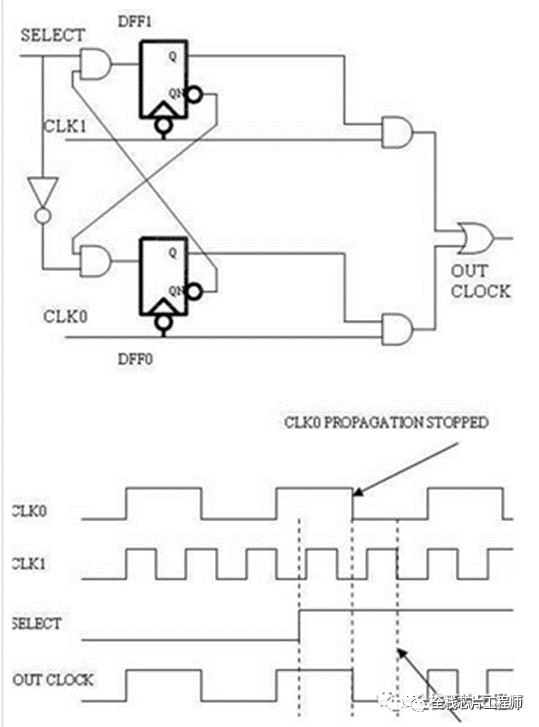

CLK0与CLK1为同步时钟源,即CLK0与CLK1成整数倍关系

插入下降沿触发的D触发器,当前已打开的时钟路径上的时钟会在其下降沿之后先关闭,然后待打开时钟路径上的时钟在其下降沿之后即打开。

如下所示:从下图第二个箭头开始,实际发生时钟切换。

那么,请问CLK0与CLK1为异步时钟时,电路如何设计?

审核编辑:刘清

-

D触发器

+关注

关注

3文章

164浏览量

47917 -

Mux

+关注

关注

0文章

38浏览量

23382 -

CLK

+关注

关注

0文章

127浏览量

17175 -

时钟切换电路

+关注

关注

0文章

7浏览量

5774

原文标题:不得不熟练的clock switch设计

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

数字前中后端都不得不熟练的clock switch设计

数字前中后端都不得不熟练的clock switch设计

评论