*本文作者:David Schnaufer,Qorvo技术营销传播经理

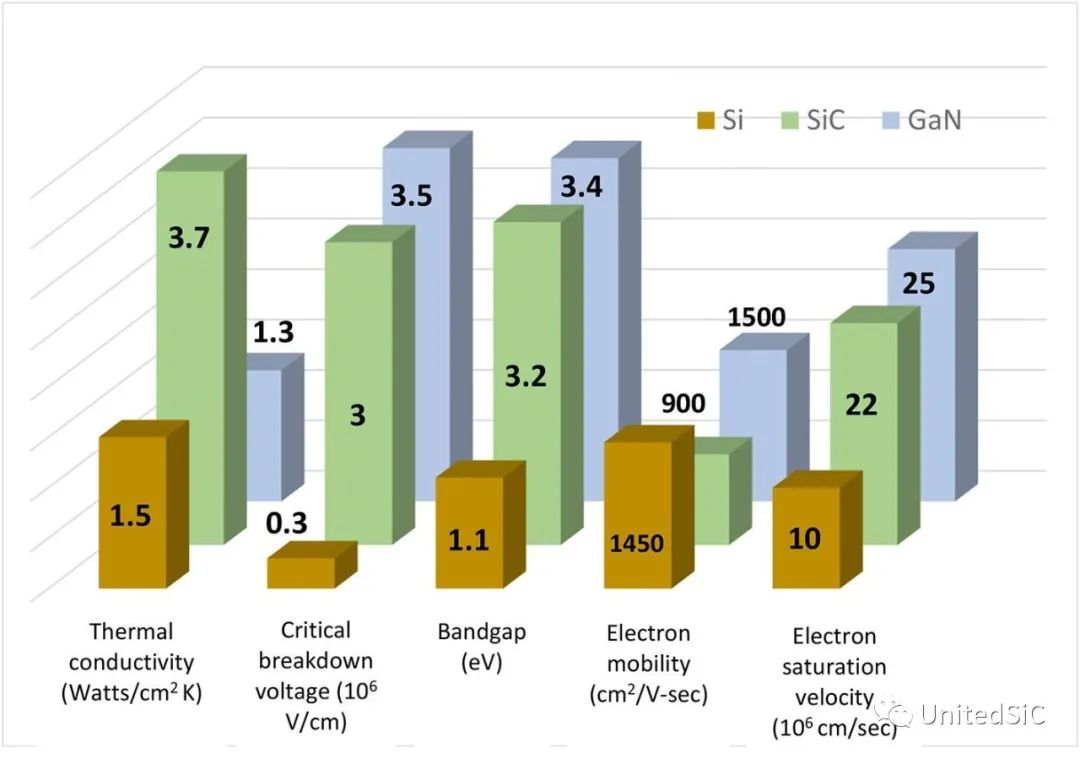

每隔一段时间便会偶尔出现全新的半导体开关技术;当这些技术进入市场时,便会产生巨大的影响。使用碳化硅(SiC)和氮化镓(GaN)等宽带隙材料的器件技术无疑已经做到了这一点。与传统硅基产品相比,这些宽带隙技术材料在提升功率转换效率和缩减尺寸方面都有了质的飞跃。

凭借SiC在缩减尺寸方面的全新能力,Qorvo的SiC FET技术用于采用TO-Leadless(TOLL)封装的750V器件开发,并扩大了其领先优势。那么,如此小巧的TOLL封装能带来什么?这正是我们下面要深入探讨的问题。

封装因素 与TO-247和D2PAK相比,TOLL封装的体积缩小了30%,高度降低了一半,仅为2.3毫米。因此,就尺寸而言,其显著优于TO-247和D2PAK标准封装。除了这些品质外,Qorvo的SiC-FET还为客户的整体最终设计提供了其它关键因素。下面我们将对此做简要介绍。 权衡考虑 与任何半导体技术一样,设计工程师在创建应用时必须对参数的权衡加以考虑。任何设计工程师所能期望的最好结果就是找到一个最佳的中间地带。事实上,Qorvo的SiC-FET具有业内最低的 RDS(ON)。更低的RDS(ON)允许使用较小的封装获得较高的额定电流。因此,通过减小尺寸,我们可以在TOLL封装内放置一个750V SiC-FET。 RDS(ON)与效率的关系:-

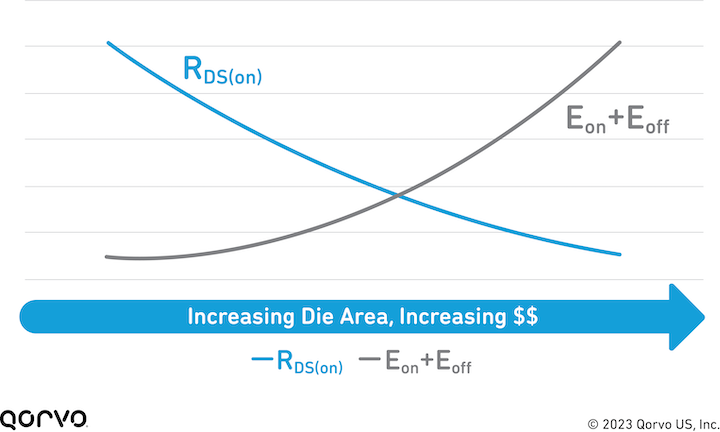

所有FET在传导过程中都会产生一定的功率损耗。传导中的功率损耗与额定RDS(ON)值成正比;这种损耗等效于系统效率的下降。通常情况下,要达到较低的RDS(ON),就需要增大FET的尺寸;然而,这就相当于在降低传导损耗的同时,增大了半导体尺寸(见下图1)。而增大FET尺寸便意味着增加了成本和开关损耗。显然,成本和RDS(ON)之间存在着折衷。就Qorvo的SiC-FET而言,由于元件的整体尺寸远远小于竞争对手SiC、硅或GaN功率技术产品,因而能够将这种折衷降至最低(见图3 左图)。

图1:RDS(ON)与Eon和Eoff间的权衡

图1:RDS(ON)与Eon和Eoff间的权衡

-

如上图所示,不仅在RDS(ON)和尺寸间存在权衡取舍,开关能量和RDS(ON)之间也是如此。随着器件RDS(ON)的增加,开关能量(Eon和Eoff)也会增加;也就是说,当RDS(ON)和传导损耗走向更低的方向,Eon和Eoff开关损耗也会增加。在电动车DC/DC转换器或功率因数校正(PFC)解决方案等硬开关应用中,这两个参数间的权衡带来更大的挑战。但最终,通过平衡这两个参数,可以实现优化的结果。将Qorvo的SiC-FET与其它电源技术进行比较,可以发现两者的竞争优势基本相当。

-

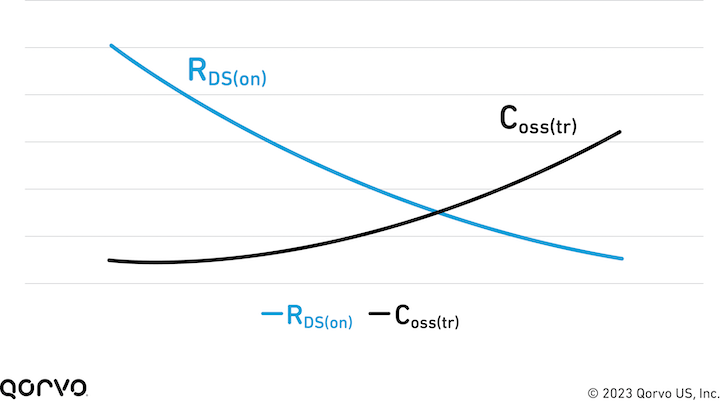

在电动车用DC/DC转换器等软开关应用中,RDS(ON)与Coss(tr)或FET输出电容(tr-表示与时间相关)间需进行权衡(参见下图);器件 RDS(ON)越低,Coss(tr)越大。在软开关应用中,Coss(tr)是决定FET工作频率的关键因素。输出电容越小,工作频率就越高。在软开关应用中,则要在这两个参数间做出选择,以确保系统达到最佳工作频率。也就是说,如图 3 右侧所示,Qorvo的SiC-FET技术在给定Coss(tr)的情况下具有更低的总RDS(ON),使得Qorvo的SiC-FET技术在许多软开关应用中更具优势。

图2:RDS(on)和Coss(tr)间的权衡

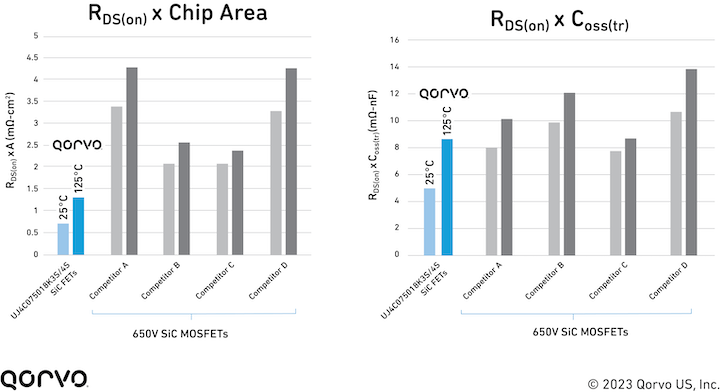

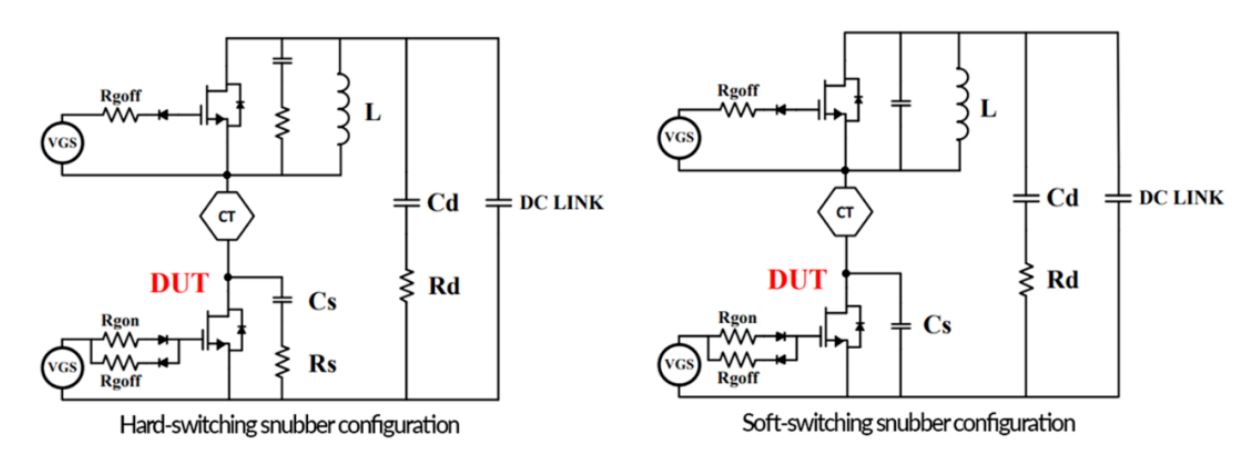

如下图所示,综合权衡这些取舍并考虑竞争因素后可以看到,较低的RDS(ON)在硬开关和软开关情况下均拥有巨大优势,而在软开关应用中优势更大。

图2:RDS(on)和Coss(tr)间的权衡

如下图所示,综合权衡这些取舍并考虑竞争因素后可以看到,较低的RDS(ON)在硬开关和软开关情况下均拥有巨大优势,而在软开关应用中优势更大。

图 3:比较25°C和125°C时650V与750V等级的SiC技术

与硅基MOSFET相比,Qorvo SiC-FET在软开关应用中具有更低的传导损耗和更高的工作频率,并且在硬开关应用中开关损耗也更低。同市场上其它SiC技术相比,Qorvo SiC-FET具有更高的工作频率和更低的传导损耗。

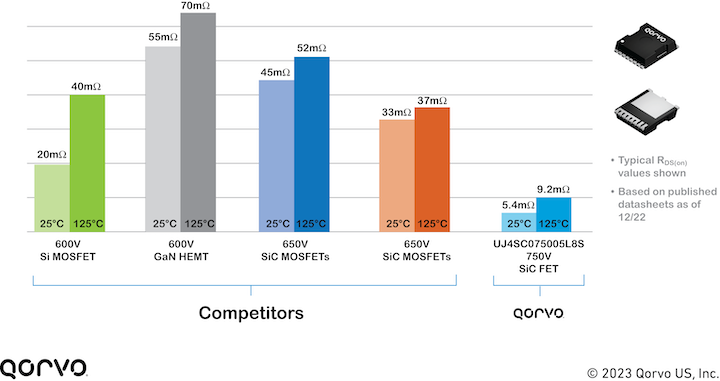

纵观市场上其它厂商的TOLL封装产品,我们可以发现它们在电压等级和RDS(ON)参数方面均落后于Qorvo。这是由于Qorvo的SiC-FET技术具有同类最佳的特定导通电阻;这意味着可以使用更小的封装类型,但仍能实现最低的总电阻。下图显示了Qorvo的SiC FET(UJ4SC075005L8S器件)与其它同类最佳TOLL封装器件、硅基MOSFET、GaN HEMT单元,和SiC MOSFET在25°C和125°C时的比较。

图 3:比较25°C和125°C时650V与750V等级的SiC技术

与硅基MOSFET相比,Qorvo SiC-FET在软开关应用中具有更低的传导损耗和更高的工作频率,并且在硬开关应用中开关损耗也更低。同市场上其它SiC技术相比,Qorvo SiC-FET具有更高的工作频率和更低的传导损耗。

纵观市场上其它厂商的TOLL封装产品,我们可以发现它们在电压等级和RDS(ON)参数方面均落后于Qorvo。这是由于Qorvo的SiC-FET技术具有同类最佳的特定导通电阻;这意味着可以使用更小的封装类型,但仍能实现最低的总电阻。下图显示了Qorvo的SiC FET(UJ4SC075005L8S器件)与其它同类最佳TOLL封装器件、硅基MOSFET、GaN HEMT单元,和SiC MOSFET在25°C和125°C时的比较。

图4:TOLL封装、600-750V等级、25°C和125°C时的开关导通电阻比较。

你没看错,这个对比尺度没有任何问题——SiC FET比最接近的供应商好4倍,比TOLL封装的GaN高约10倍!同样重要的是,SiC FET的额定电压为750V,具有强大的雪崩特性。其它器件的额定电压仅为600/650V,而GaN HEMT单元则没有雪崩额定电压。

如上所述的诸多优势,同时在较小的TOLL封装中采用额定电压更高的开关,则意味着更高的成本效益。

最佳应用切入点

采用TOLL封装的SiC-FET功率开关的重点应用场景为功率密度至关重要的的领域,功率范围在几百瓦到10千瓦以上;包括电视、电池充电器和便携式发电站中的开关模式功率转换,以及数据通信、太阳能,及储能逆变器中的电源。作为断路器,这些设备可用于建筑配电板和电动汽车充电器。

空间在许多此类应用中非常宝贵,与其它供应商相比,TOLL封装的SiC FET是一种具有成本效益的解决方案,适合在有限的空间内使用,所需的散热片成本也较低;此外还通过采用无引线布置和开尔文连接最大限度地减少了连接电感,从而实现了低动态损耗的快速开关。

图4:TOLL封装、600-750V等级、25°C和125°C时的开关导通电阻比较。

你没看错,这个对比尺度没有任何问题——SiC FET比最接近的供应商好4倍,比TOLL封装的GaN高约10倍!同样重要的是,SiC FET的额定电压为750V,具有强大的雪崩特性。其它器件的额定电压仅为600/650V,而GaN HEMT单元则没有雪崩额定电压。

如上所述的诸多优势,同时在较小的TOLL封装中采用额定电压更高的开关,则意味着更高的成本效益。

最佳应用切入点

采用TOLL封装的SiC-FET功率开关的重点应用场景为功率密度至关重要的的领域,功率范围在几百瓦到10千瓦以上;包括电视、电池充电器和便携式发电站中的开关模式功率转换,以及数据通信、太阳能,及储能逆变器中的电源。作为断路器,这些设备可用于建筑配电板和电动汽车充电器。

空间在许多此类应用中非常宝贵,与其它供应商相比,TOLL封装的SiC FET是一种具有成本效益的解决方案,适合在有限的空间内使用,所需的散热片成本也较低;此外还通过采用无引线布置和开尔文连接最大限度地减少了连接电感,从而实现了低动态损耗的快速开关。

原文标题:以更小封装实现更大开关功率,Qorvo SiC FET如何做到的?

文章出处:【微信公众号:Qorvo半导体】欢迎添加关注!文章转载请注明出处。

-

Qorvo

+关注

关注

17文章

632浏览量

77382

原文标题:以更小封装实现更大开关功率,Qorvo SiC FET如何做到的?

文章出处:【微信号:Qorvo_Inc,微信公众号:Qorvo半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

实现电流和控制信号分离,罗姆新型SiC封装模块助力实现更小型的xEV逆变器

小封装隔离电源驱动产品--LTP850x

谷景助力智能家电升级:更小体积,更大功率

一文解析SiC功率器件互连技术

Qorvo推出创新紧凑型E1B封装1200V SiC模块

Qorvo借助SiC FET独特优势,稳固行业领先地位

Qorvo推出D2PAK封装SiC FET

Qorvo® 推出D2PAK 封装 SiC FET,提升 750V 电动汽车设计性能

以更小封装实现更大开关功率,Qorvo SiC FET如何做到的?

以更小封装实现更大开关功率,Qorvo SiC FET如何做到的?

评论