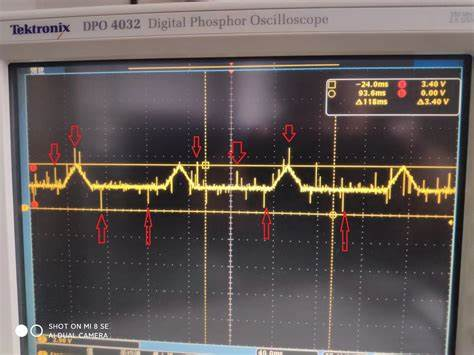

可编程逻辑系统通常部署在可能存在噪声的应用中。这种噪声会影响可编程逻辑设计接收的信号。例如,它可能会导致信号故障或跳动,如果处理不当,可能会导致设计和操作出现问题。

毛刺的持续时间是随机的,并且与时钟沿不同步。因此,它们可能会导致下游信息损坏。

处理此问题的最常见方法是使用毛刺滤波器来滤除毛刺和反弹。

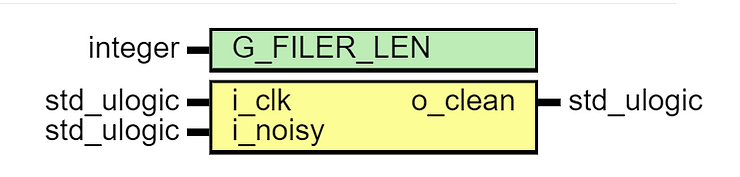

毛刺滤波器核心是使用长度可变的移位寄存器,噪声信号被放到寄存器中,直到移位寄存器的所有值都一致。此时,信号可以视为稳定。当然,我们必须确定潜在毛刺和反弹可能持续多长时间,以确保时钟周期的寄存器大小正确。这就是为什么我们的毛刺滤波器需要非常灵活,并且需要确保其大小能够适合每个应用程序的要求。

滤波器应该能够接收噪声输入并滤除持续时间为多个时钟脉冲的毛刺。

libraryieee; useieee.std_logic_1164.all; useieee.numeric_std.all; entityglitch_filteris generic( G_FILER_LEN:integer:=8 ); port( i_clk:instd_ulogic; i_noisy:instd_ulogic; o_clean:outstd_ulogic ); endglitch_filter; architecturebehaviourofglitch_filteris signals_delay_line:std_ulogic_vector(G_FILER_LEN-1downto0); signals_delay_and:std_ulogic; signals_delay_nor:std_ulogic; signals_output_clean:std_ulogic; begin o_clean<= s_output_clean; --Delay disctete using delay line synchroniser_process : process (i_clk) begin if rising_edge(i_clk) then s_delay_line <= s_delay_line(G_FILER_LEN - 2 downto 0) & i_noisy; end if; end process; --Generate AND and NOR of delay line bits s_delay_and <= '1' when to_01(s_delay_line) = (s_delay_line'range =>'1')else'0'; s_delay_nor<= '1' when to_01(s_delay_line) = (s_delay_line'range =>'0')else'0'; --Setdiscretebasedondelayline output_process:process(i_clk)begin ifrising_edge(i_clk)then ifs_delay_nor='1'then s_output_clean<= '0'; elsif s_delay_and = '1' then s_output_clean <= '1'; end if; end if; end process; end behaviour;

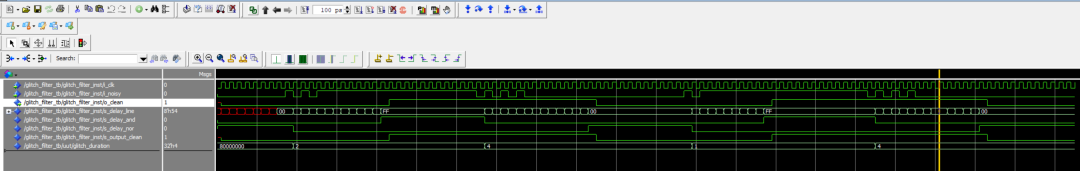

为了测试这个模块,创建一个简单的测试文件,它将随机数量的毛刺注入信号中。在信号改变状态后,许多随机毛刺被输入到信号中。如果滤波器运行正常,则这些毛刺将在毛刺滤波器输出干净的信号。

libraryieee; useieee.std_logic_1164.all; useieee.numeric_std.all; useieee.math_real.all; entityglitch_filter_tbis end; architecturebenchofglitch_filter_tbis componentglitch_filter generic( G_FILER_LEN:integer ); port( i_clk:instd_ulogic; i_noisy:instd_ulogic; o_clean:outstd_ulogic ); endcomponent; --Clockperiod constantclk_period:time:=10ns; --Generics constantG_FILER_LEN:integer:=8; --Ports signali_clk:std_ulogic:='0'; signali_noisy:std_ulogic; signalo_clean:std_ulogic; begin i_clk<= not i_clk after (clk_period/2); glitch_filter_inst : glitch_filter generic map ( G_FILER_LEN =>G_FILER_LEN ) portmap( i_clk=>i_clk, i_noisy=>i_noisy, o_clean=>o_clean ); uut:process variableglitch_duration:integer; variableseed1:positive:=1; variableseed2:positive:=283647823; impurefunctioninteger_random(min,max:integer)returnintegeris variablerandom:real; begin uniform(seed1,seed2,random); returninteger(round(random*real(max-min)+real(min))); endfunction; begin i_noisy<= '0'; wait until rising_edge(i_clk); wait for G_FILER_LEN * clk_period; test: for i in 0 to 1 loop i_noisy <= '1'; wait until rising_edge(i_clk); glitch_duration := integer_random(1,5); for x in 0 to glitch_duration loop i_noisy <= not i_noisy; wait until rising_edge(i_clk); end loop; i_noisy <= '1'; wait for 20 * clk_period; report "loop high completed" severity note; i_noisy <= '0'; wait until rising_edge(i_clk); glitch_duration := integer_random(1,5); for x in 0 to glitch_duration loop i_noisy <= not i_noisy; wait until rising_edge(i_clk); end loop; i_noisy <= '0'; wait for 20 * clk_period; report "loop low completed" severity note; end loop; report "Simulation complete" severity failure; end process; end;

运行仿真后显示在信号状态改变后随机数量的脉冲便增加。检查输出信号表明滤波器已正确滤除输入信号中可能存在的毛刺。

正如在一开始所说的,这样的滤波器对于部署在可能存在电噪声的环境中非常有用。与 BRAM 上的 EDAC 等其他缓解策略相结合,这是可用于实现设计弹性的关键方法之一。

审核编辑:刘清

-

滤波器

+关注

关注

160文章

7725浏览量

177630 -

寄存器

+关注

关注

31文章

5308浏览量

119977 -

状态机

+关注

关注

2文章

492浏览量

27469 -

BRAM

+关注

关注

0文章

41浏览量

10942 -

时钟脉冲

+关注

关注

0文章

19浏览量

12667

原文标题:【数字实验室】消除毛刺

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

TPA3110D2无信号输入时,输出336kHZ的正弦波信号有明显的毛刺,如何滤除毛刺?

引入输入滤波器来滤除噪声设计

毛刺的滤波方法

怎样去设计一个使用时序逻辑对单bit信号进行毛刺滤除操作的电路

FPGA | 竞争冒险和毛刺问题

电路从SDA和SCL线路中滤除毛刺的解决方法及过程

FPGA中的冒险现象和如何处理毛刺

怎样使用毛刺滤波器来滤除毛刺和反弹?

怎样使用毛刺滤波器来滤除毛刺和反弹?

评论