三 电路参数

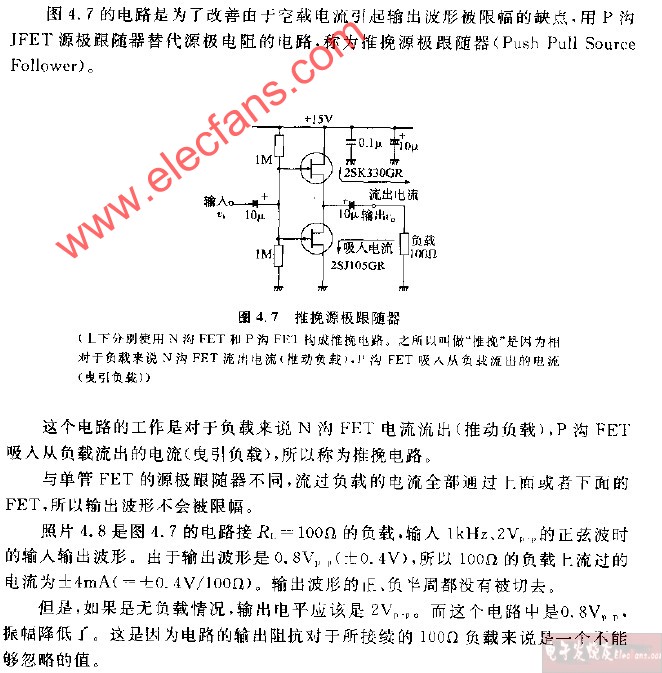

3.1 输入阻抗Zi

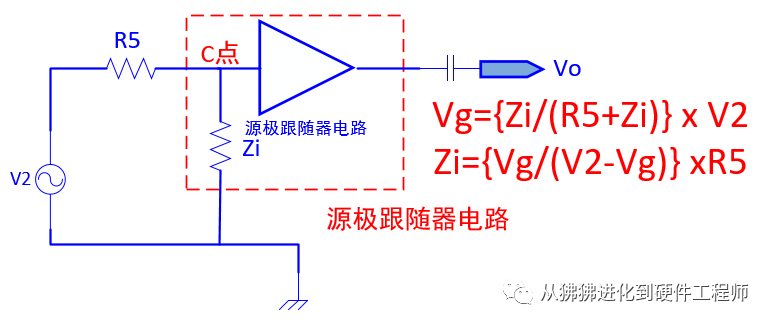

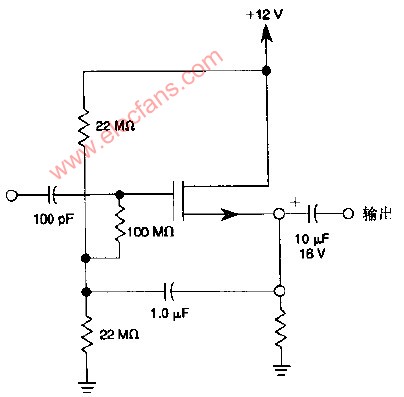

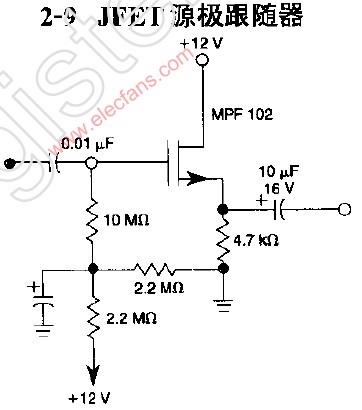

源极跟随器电路输入阻抗的确定方法,与之前源极接地放大电路输入阻抗确定方法类似。

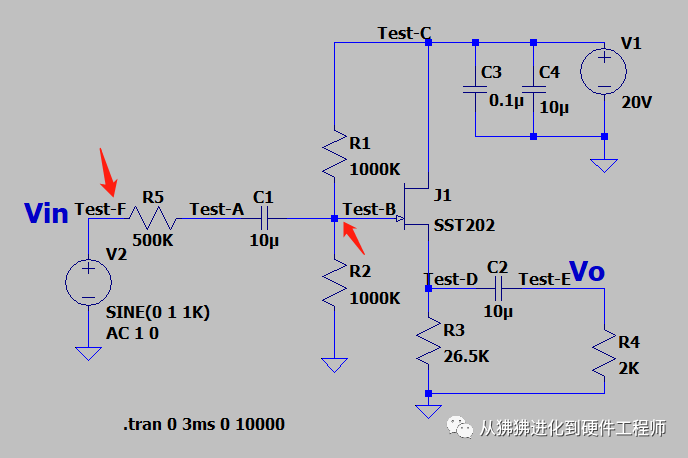

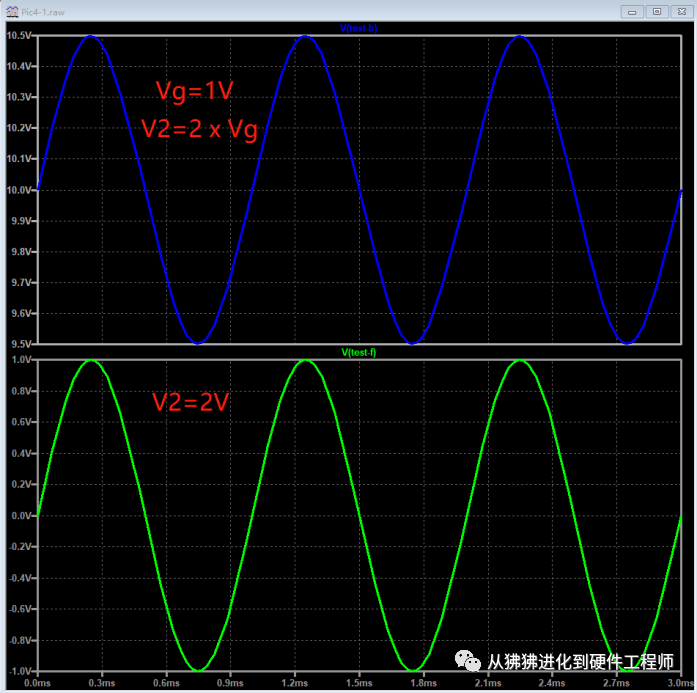

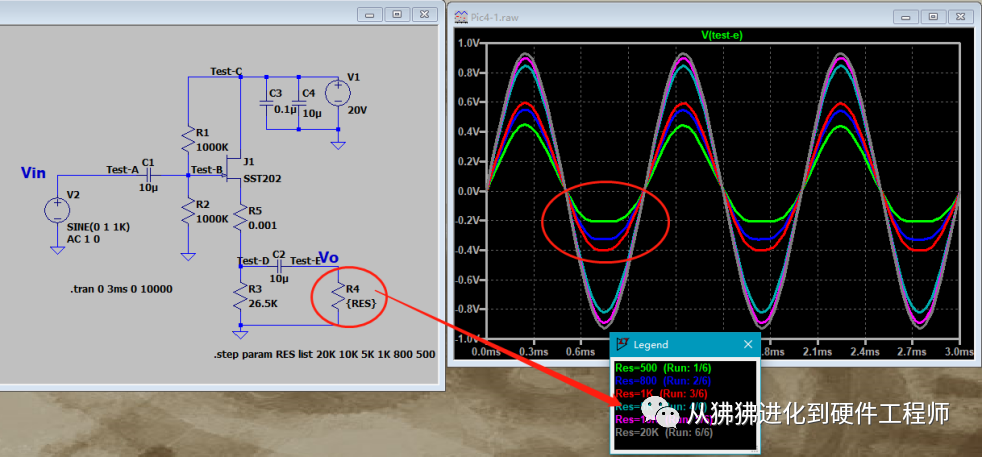

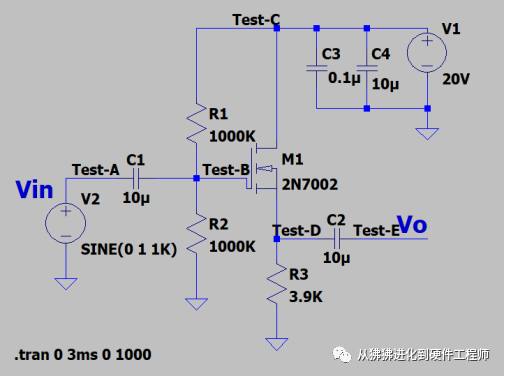

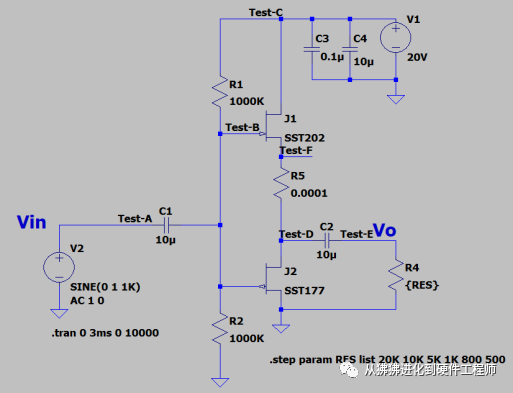

仿真或者测量电路输入阻抗,需要在信号输入端串联一个电阻,如下图R5。对交流信号而言,栅极电压Vg(c点)就是R5和源极跟随器电路的输入阻抗Zi分压得到的。

当Vg电压是V2电压的一半时,R5=Zi。

如上图,当R5=500KΩ时,V2=2 x Vg。因此此电路的输入阻抗Zi=500KΩ。此值等于R1和R2并联时的阻值。

3.2 输出阻抗Ro

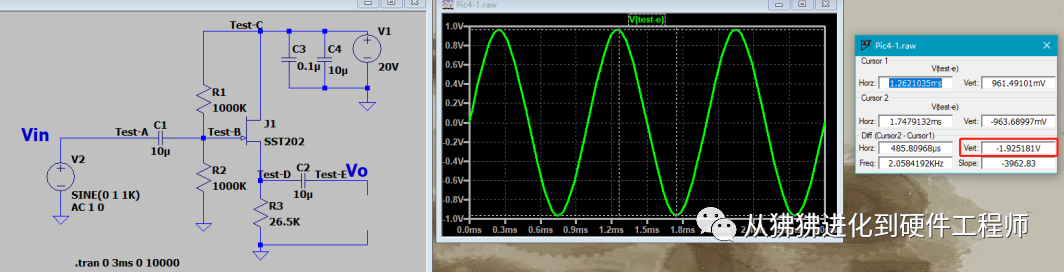

测量此电路输出阻抗

第一步:测量输出端开路时的输出电压Voo。如下仿真结果Voo=1.925V

第二步:在输出端添加负载电阻RL=2KΩ。仿真得到输出电压Vo=1.348V

第三步:按照如下公式计算此电路输出电阻Ro

Ro=856Ω

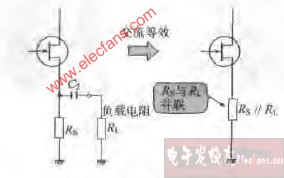

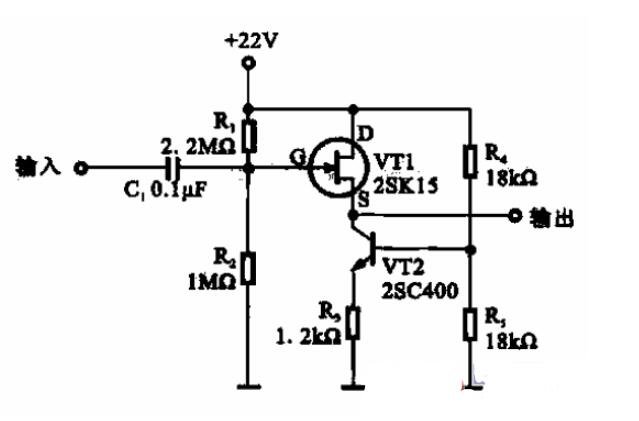

源极跟随器电路的输出阻抗比负载阻抗要低。如果将JFET换成MOSFET,它带来的输出阻抗更低。例如用MOSFET 2N7002替换SST202。按照上述步骤,得到电路输出阻抗是188Ω。

3.3 负载值对输出波形的影响

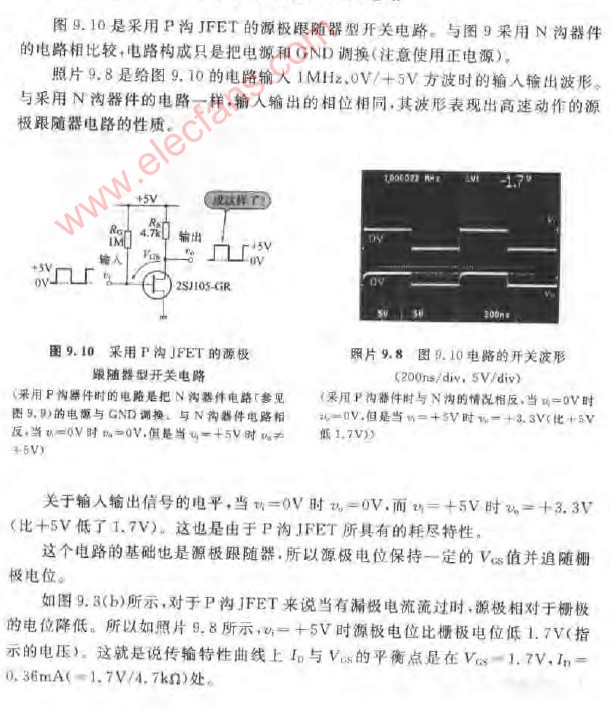

源极跟随器电路,随着负载不同,输出波形也会变化。当负载太小(电阻负载值小,负载电流大时),输出波形有可能会失真。

如下图,当负载R4取不同值时(500Ω、800Ω、1KΩ、5KΩ、10KΩ、20KΩ)的输出波形。可以看到当RL值减小时,输出波形的下半周期会失真(幅度被钳制)。

我个人理解会出现这样的现象,是因为JFET的Vgs压差限制了Is导致。如下是SST202的spec。随着Vgs压差的增大,Id电流会越来越小,直到关断(0mA)。注:Id=Is

如下是对上述想法的仿真结果,以绿色波形为例,它是RL=500Ω是的波形。

上方波形是Vgs值(即JFET的栅极与源极压差)。压差从-0.6V增大到-1.9V。

中间是Is电流,随着Vgs增大,Is慢慢变为0mA。

下方是Vo波形。因为Is已经是0mA了,导致输出波形被钳位。

上述粉色波形是RL=5KΩ时的状态。因为它的负载阻值大,对JFET输出电流要求小,因此波形没有失真。我想如果想在小负载条件下仍旧得到好的输出波形,可以考虑更换Is更大的JFET或者MOSFET。

-

跟随器

+关注

关注

1文章

86浏览量

29662 -

源极

+关注

关注

1文章

52浏览量

8212 -

输入阻抗

+关注

关注

0文章

124浏览量

15665 -

电路参数

+关注

关注

0文章

10浏览量

7254 -

输出阻抗

+关注

关注

1文章

103浏览量

12321

发布评论请先 登录

相关推荐

源极跟随器电路参数讲解(1)

源极跟随器电路参数讲解(1)

评论