一 A53使用经典的big-LITTLE架构

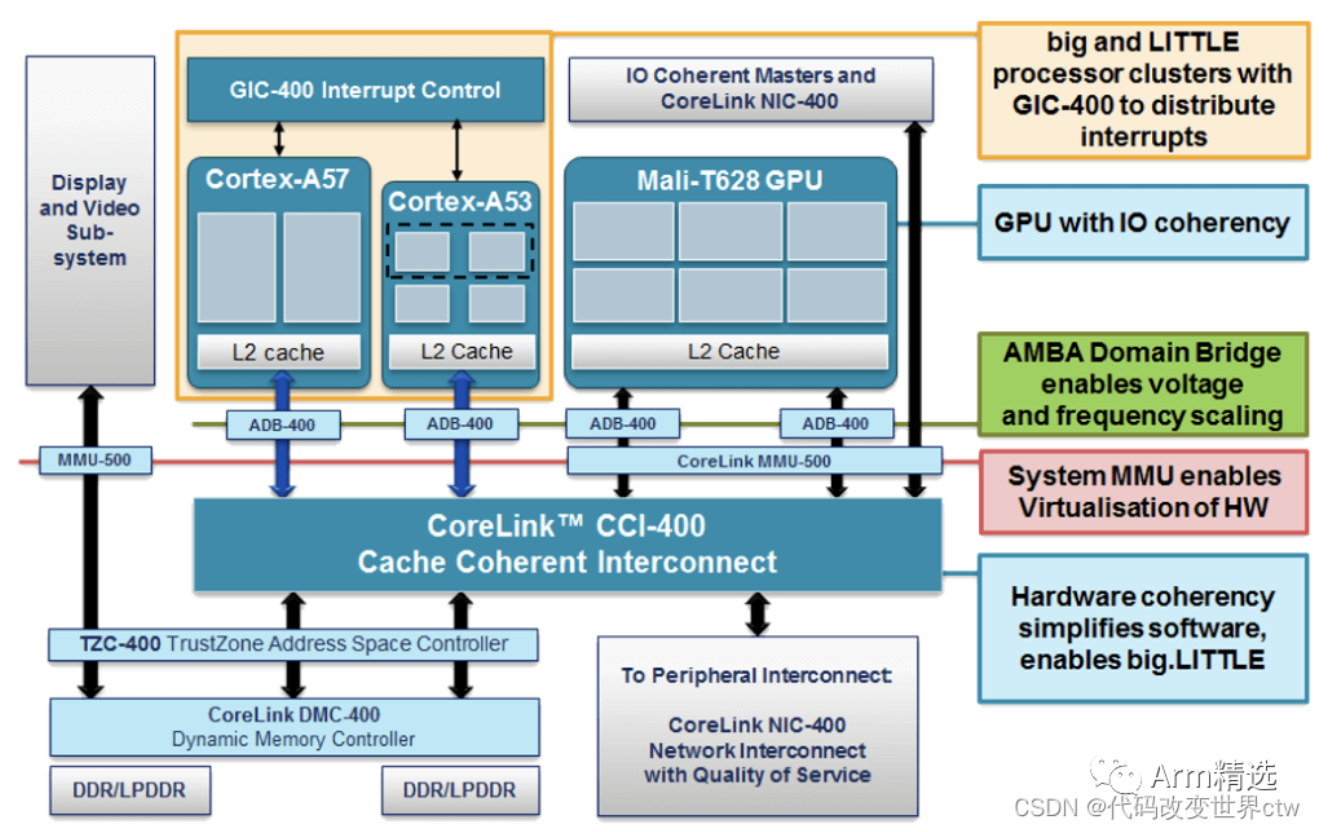

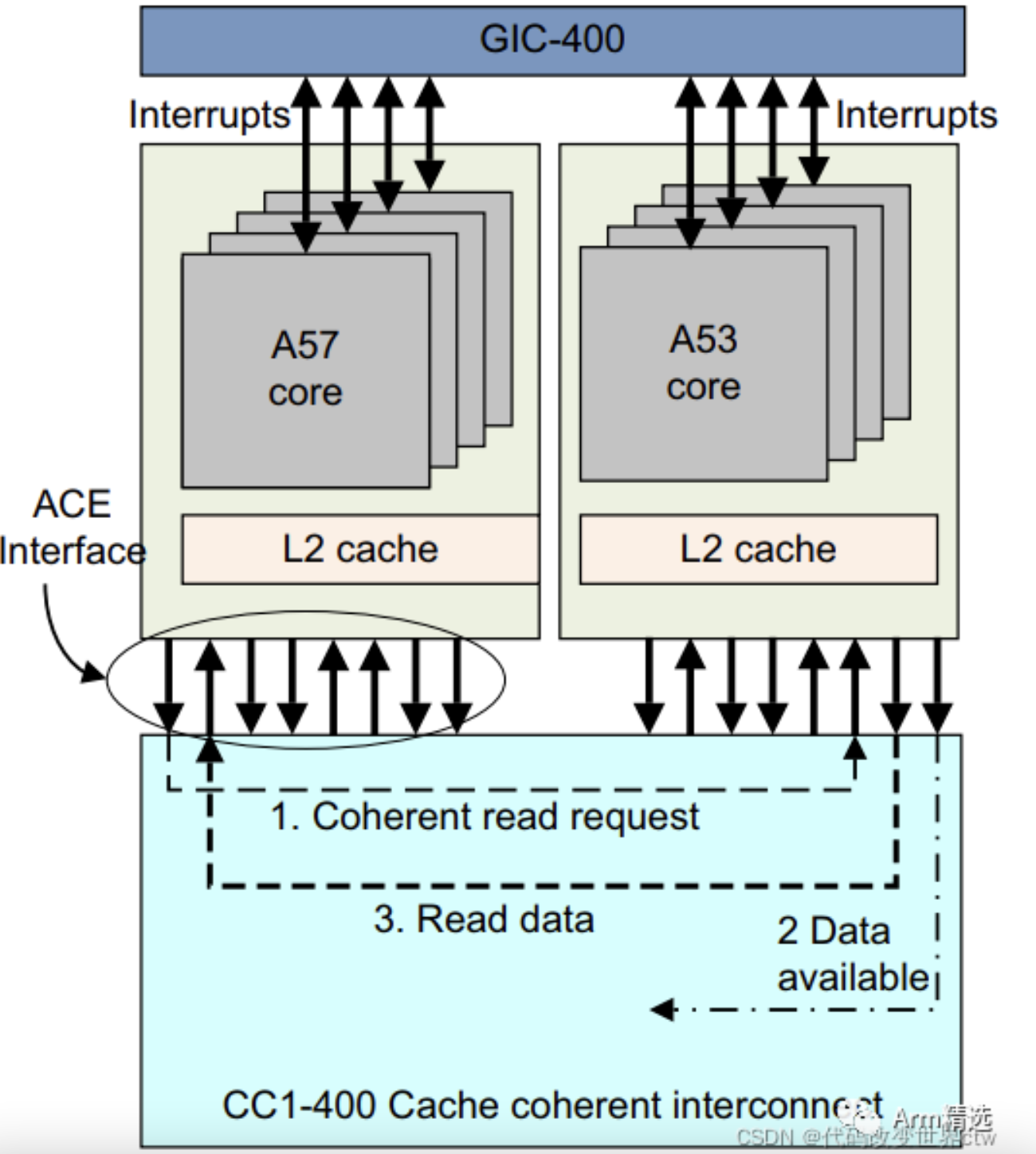

以下是一张比较早期的经典的big-LITTLE的架构图。

图1

图2

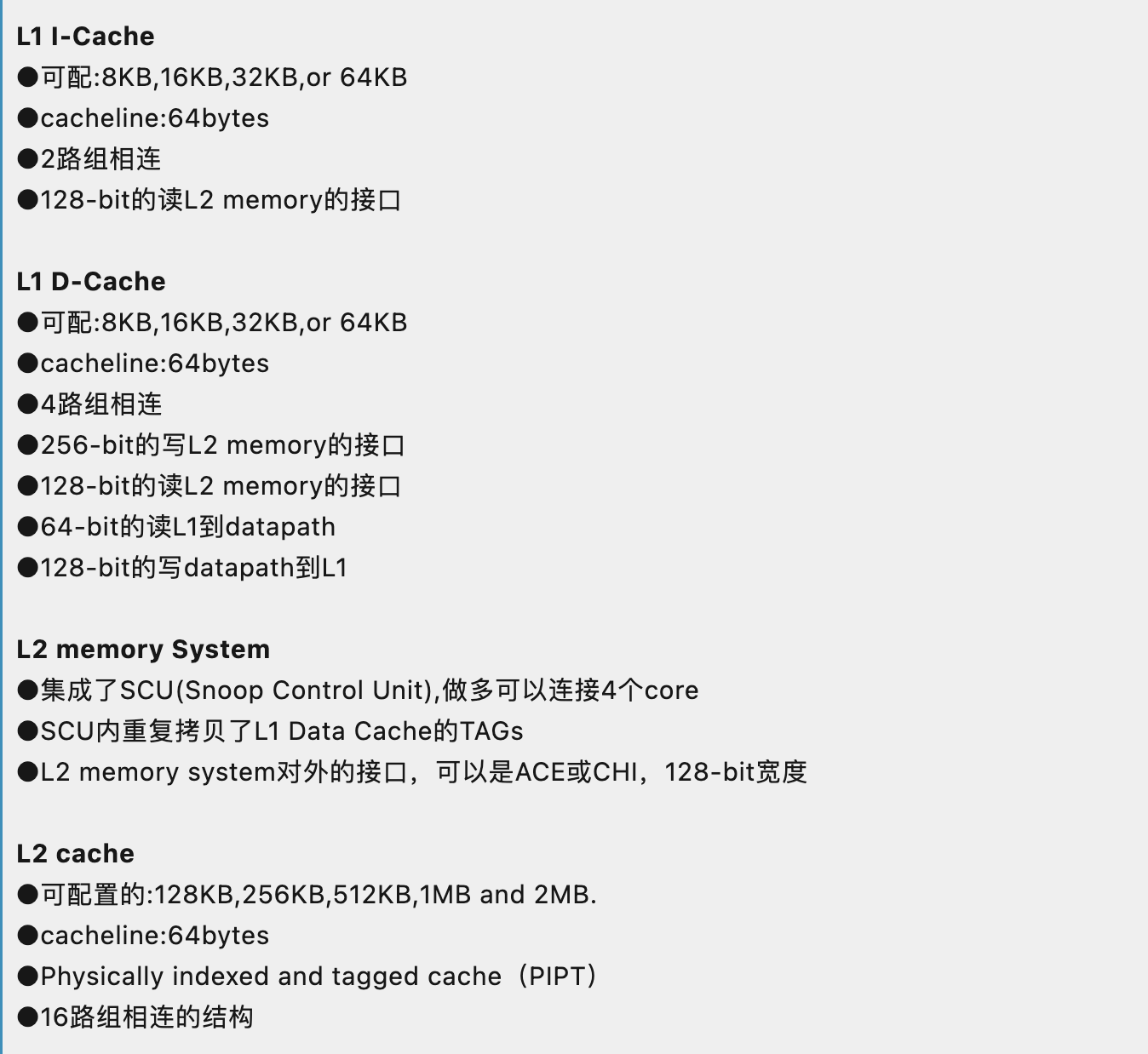

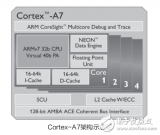

二 A53的cache配置

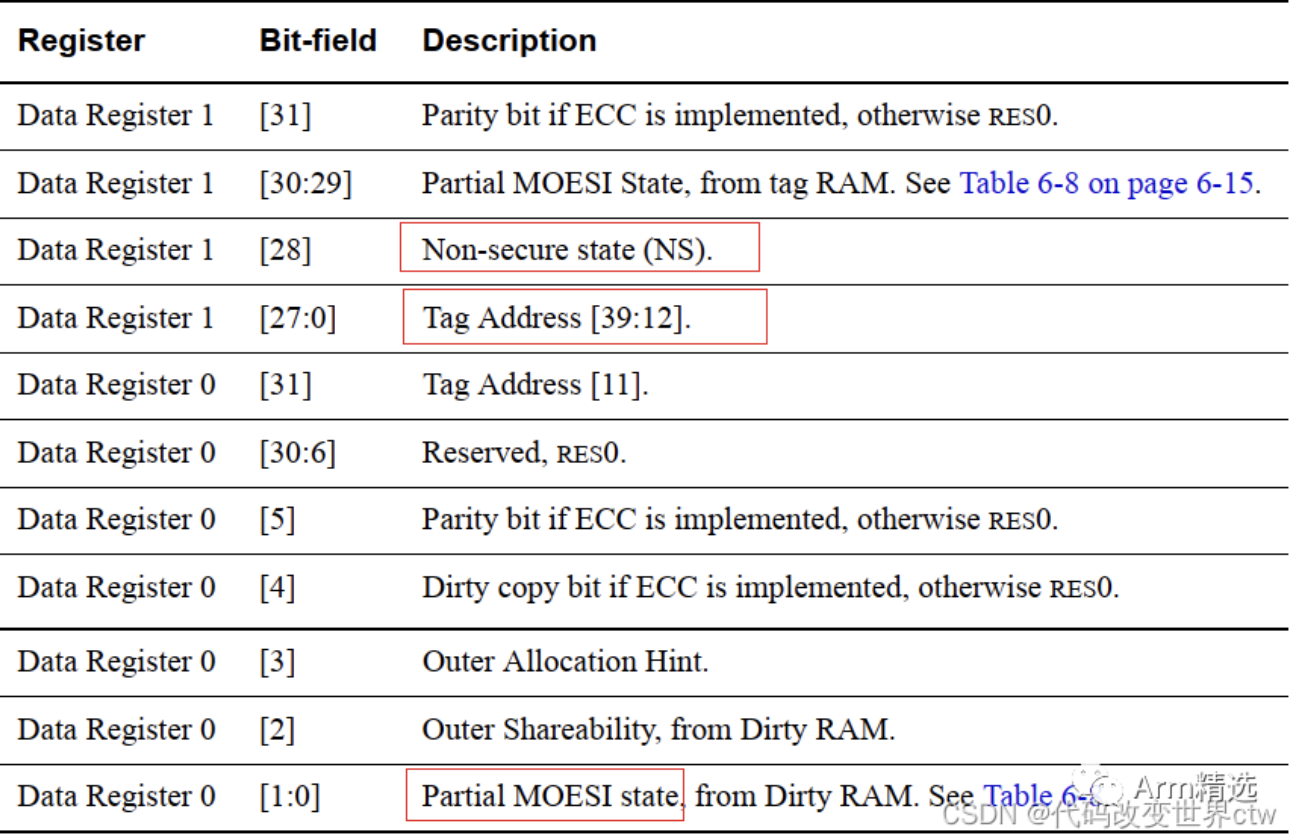

L1 data cache TAG

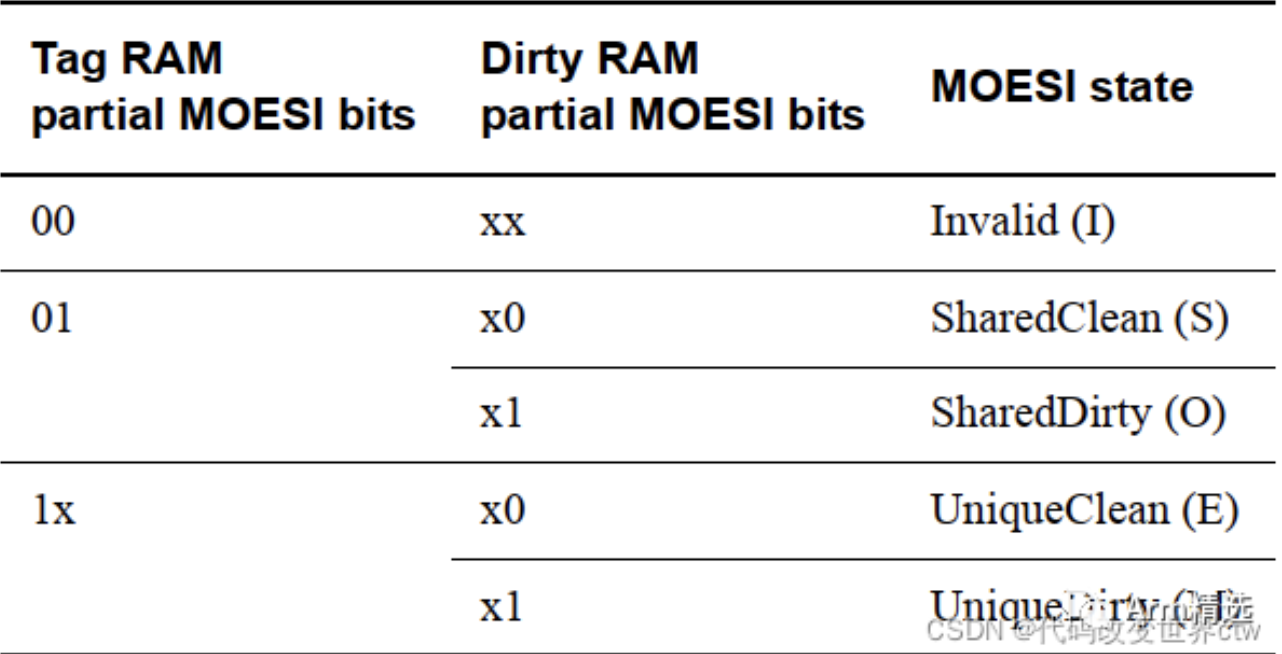

A53的L1 Data cache遵从的是MOESI协议,如下所示在L1 data cache的tag中存有MOESI的标记位。

图3

MOESI state

图4

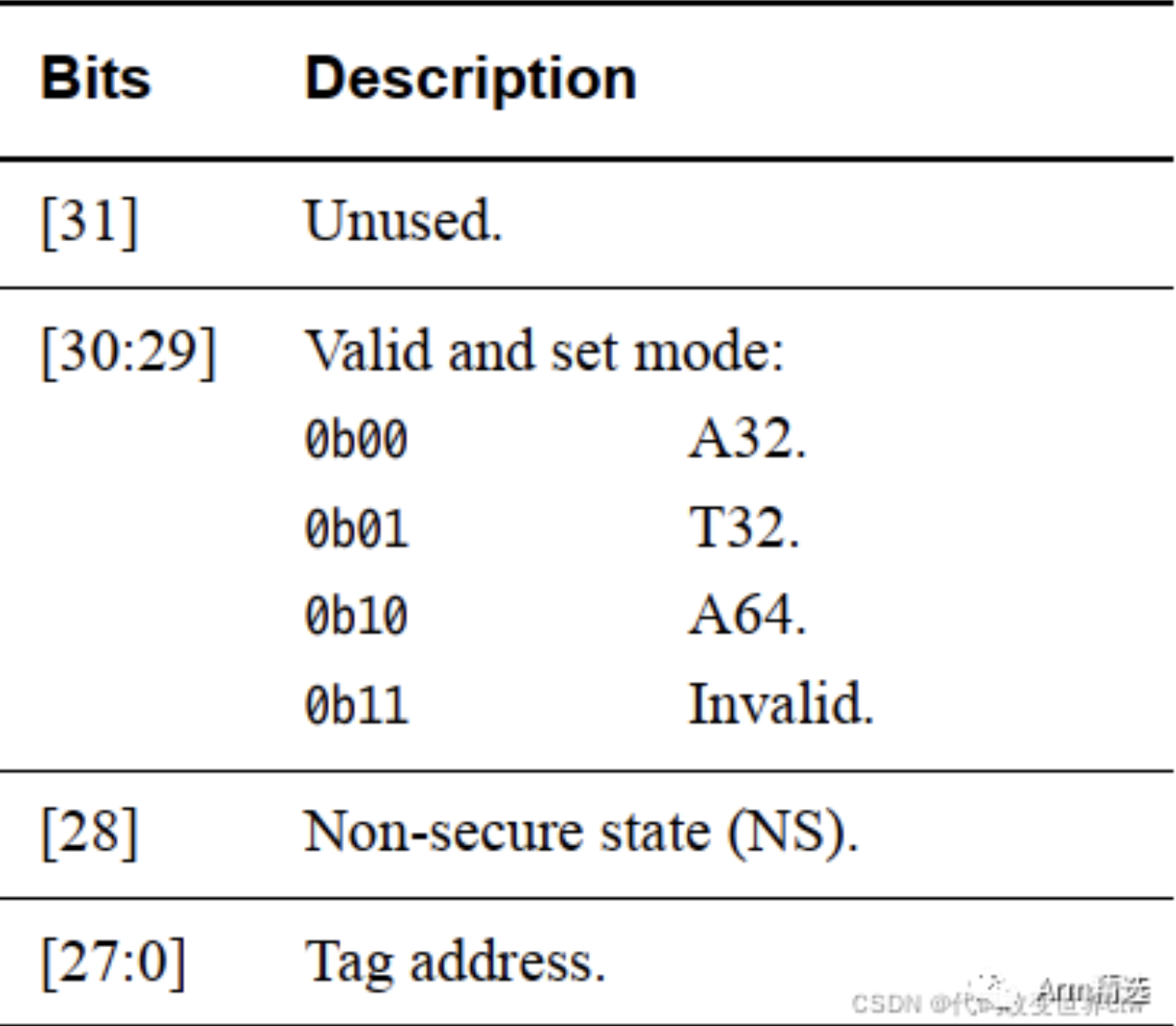

L1 Instruction cache TAG

L1 instruction cache是只读的,所以也就无需硬件维护的多core之间instruction cache的一致性,所以也就无需组从MOESI协议,以下展示了 * L1 Instruction cache的TAG,其中标记为很少,无MESI标记位。

图5

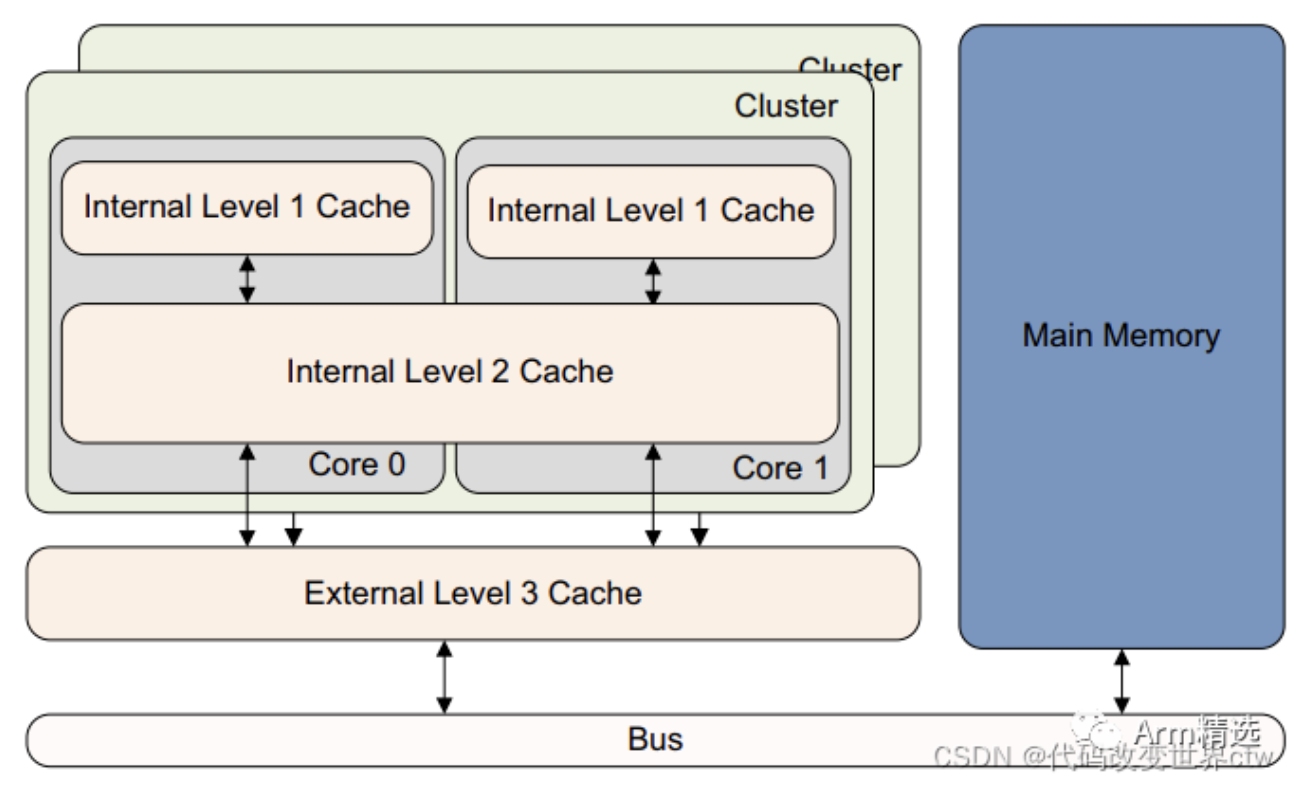

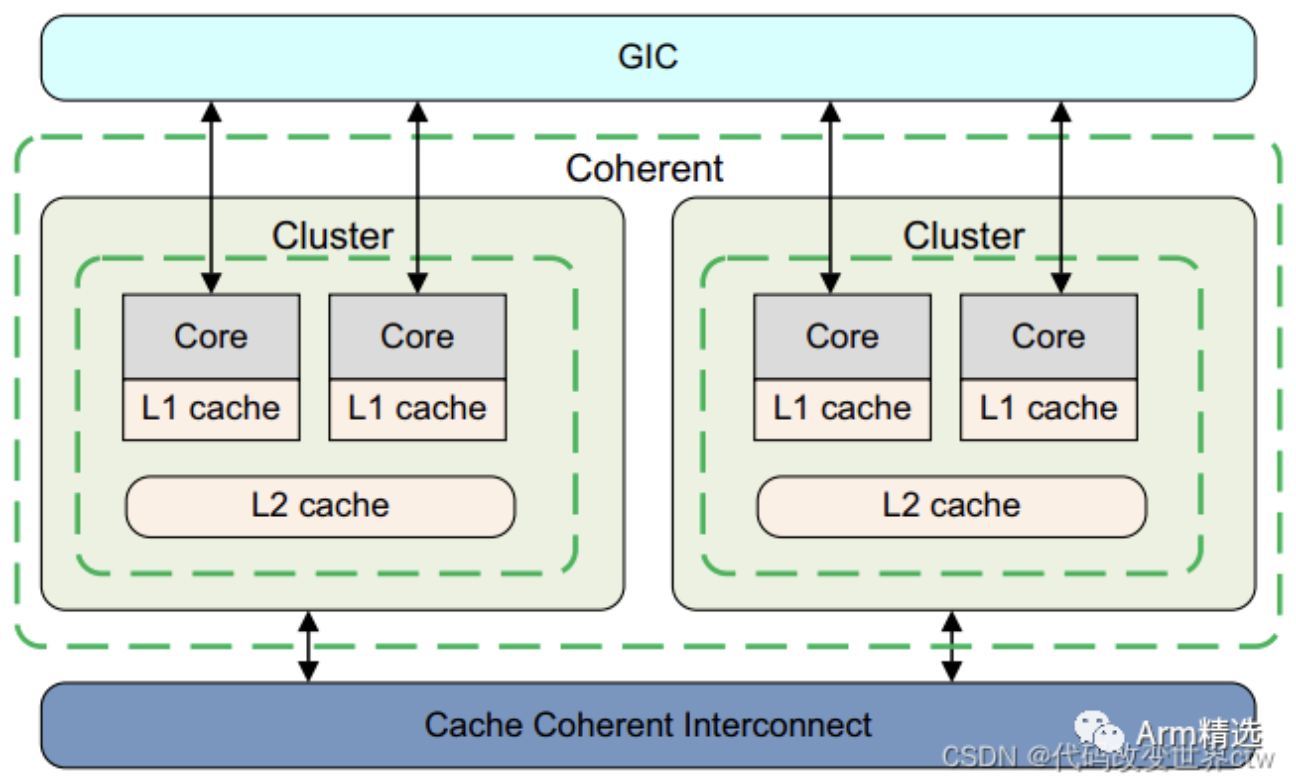

三 cache的层级结构:

- L1 cache是private的在core中。

- L2 cache是share的在cluster中。

图6

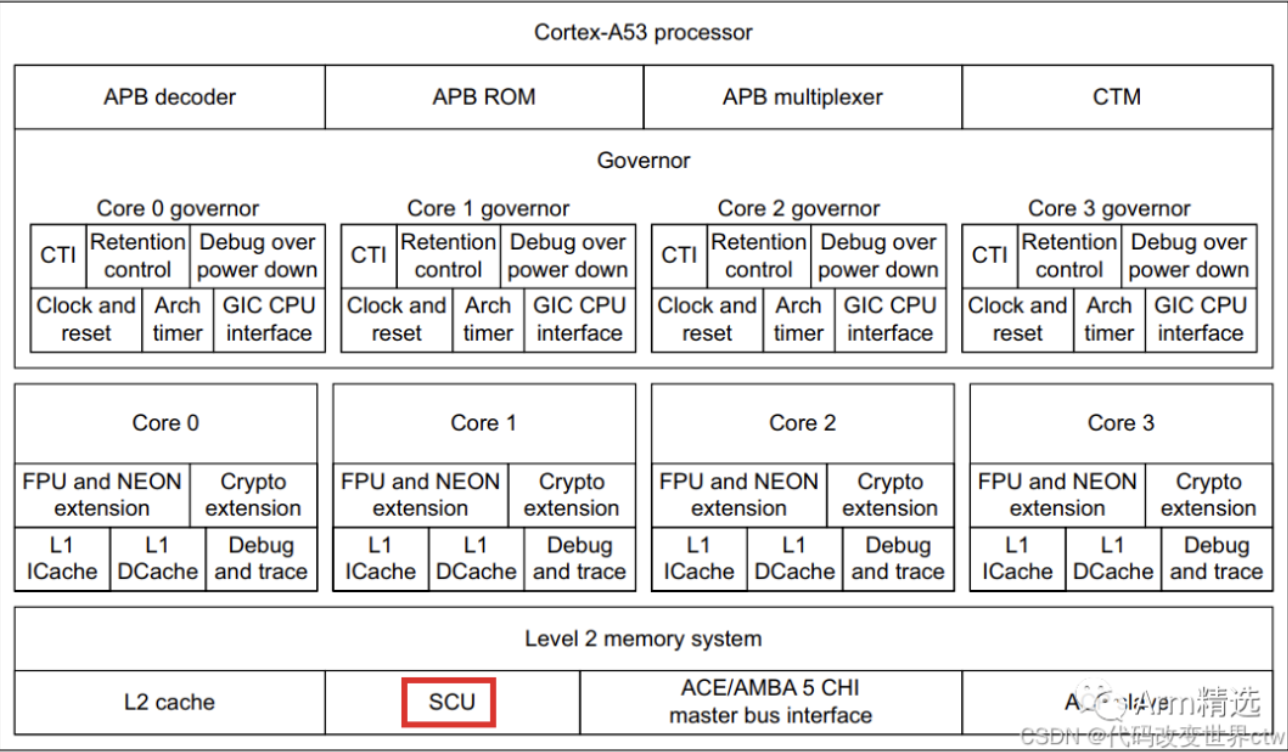

四 L2 memory System系统介绍

在bit.LITTLE架构中,在Cluster中,有一个SCU单元,SCU单元主要是执行和维护L1 cache的一致性(MESI协议或其变体如MOESI协议)。

图7

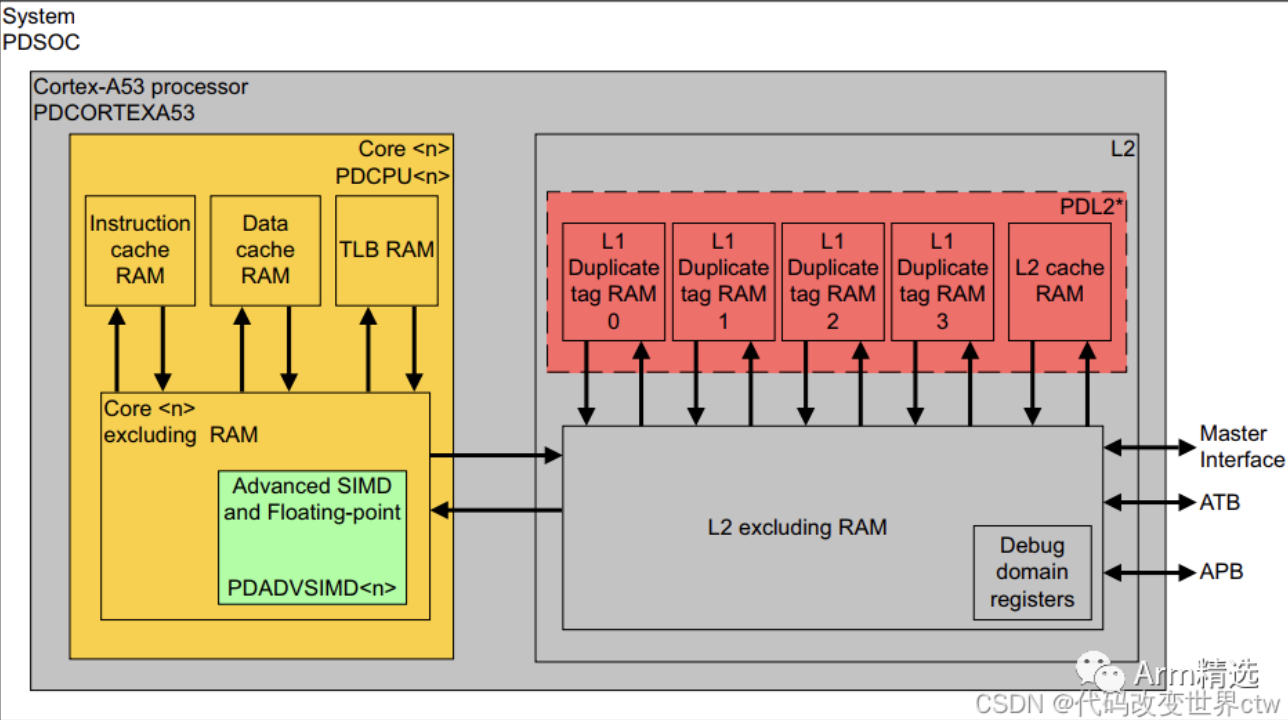

在L2 Memory System的中,除了包含L2 cache,也会包含L1 Duplicate tag RAM(这里指的其实是L1 Data Cache Tags)。

图8

五 多cluster之间的缓存一致性

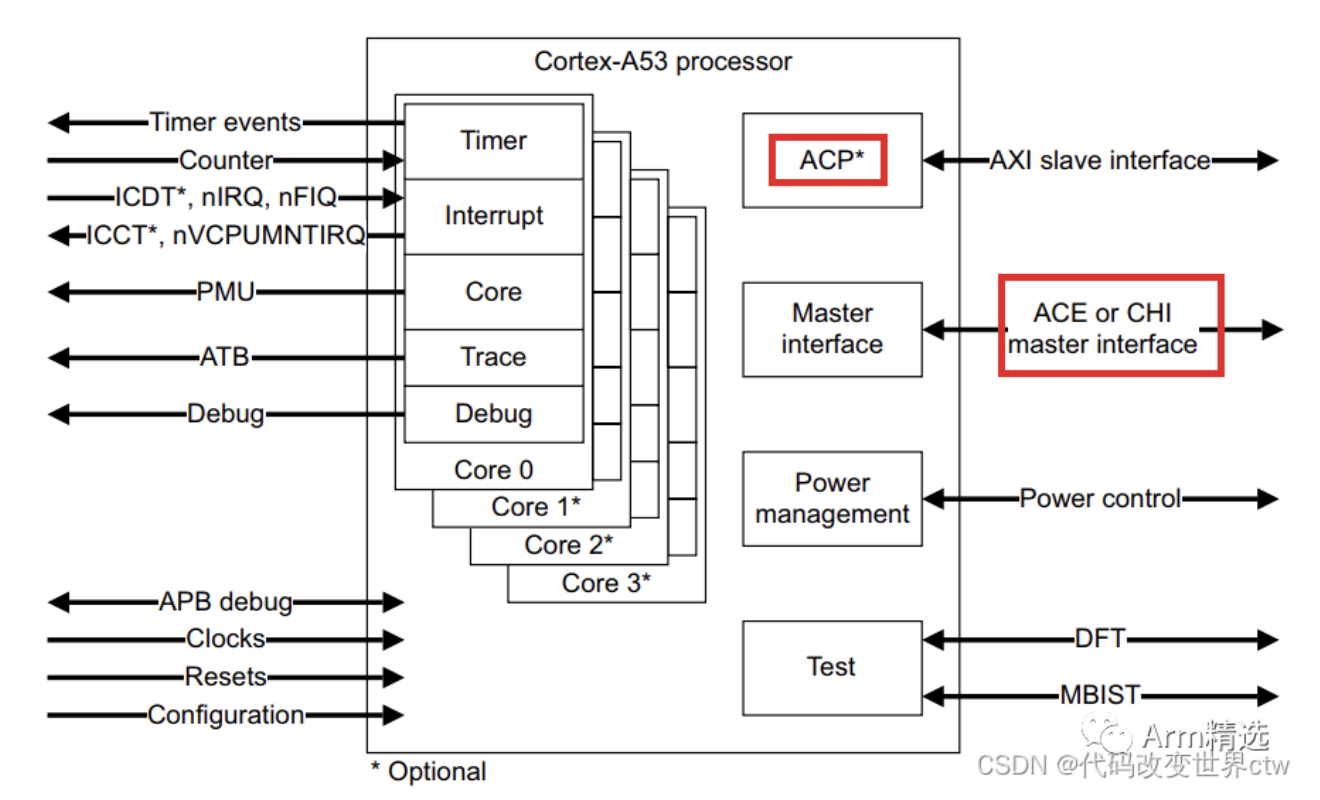

cluster和外界的接口,可以是ACE或CHI(目前常用的是ACE,后面的趋势可能是CHI)。

图9

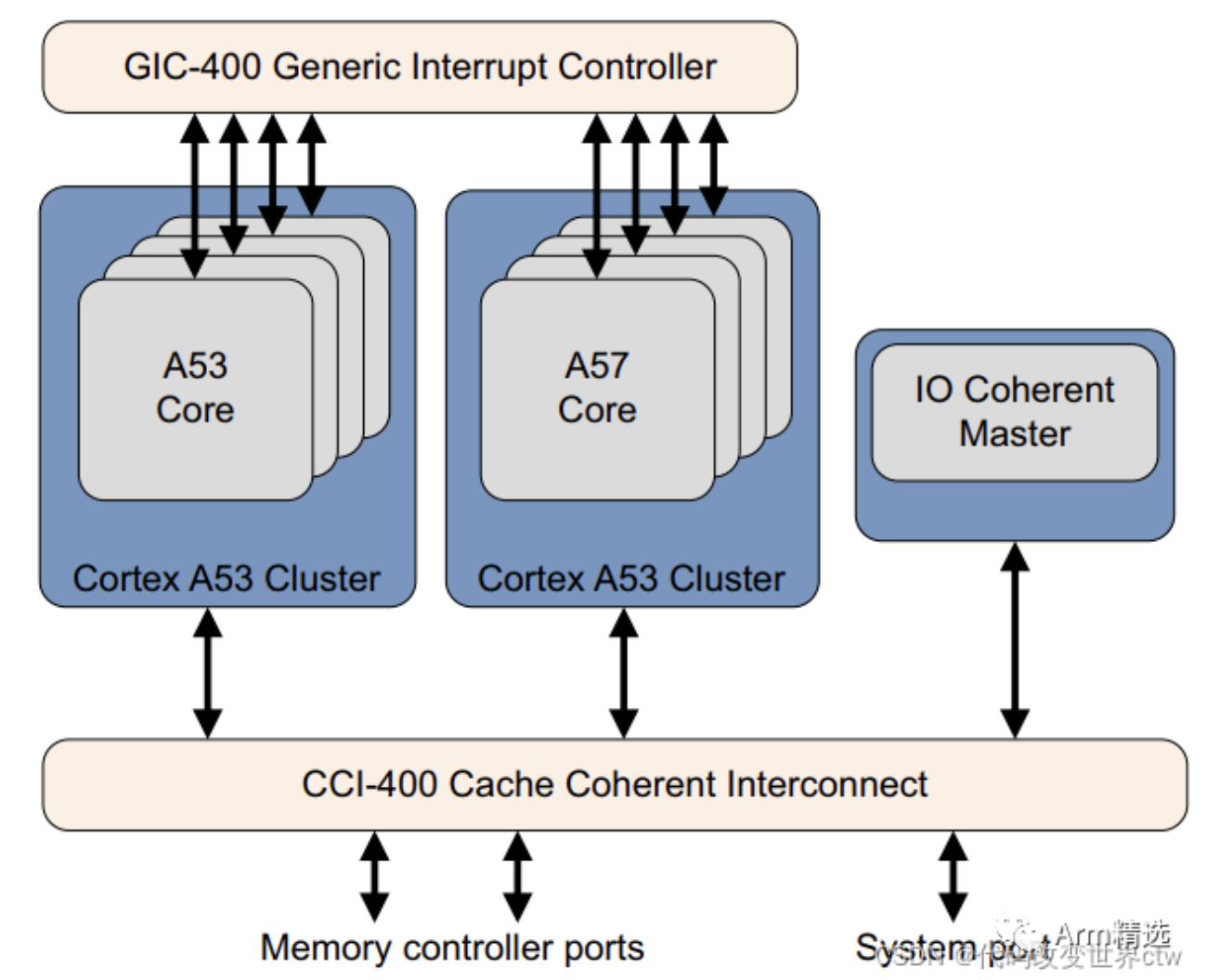

- 如果使用的是ACE,那么多cluster之间的一致性,依靠CCI+ACE来维护。

- 如果使用的是CHI,那么多cluster之间的一致性,依靠CMN+CHI来维护。

图10

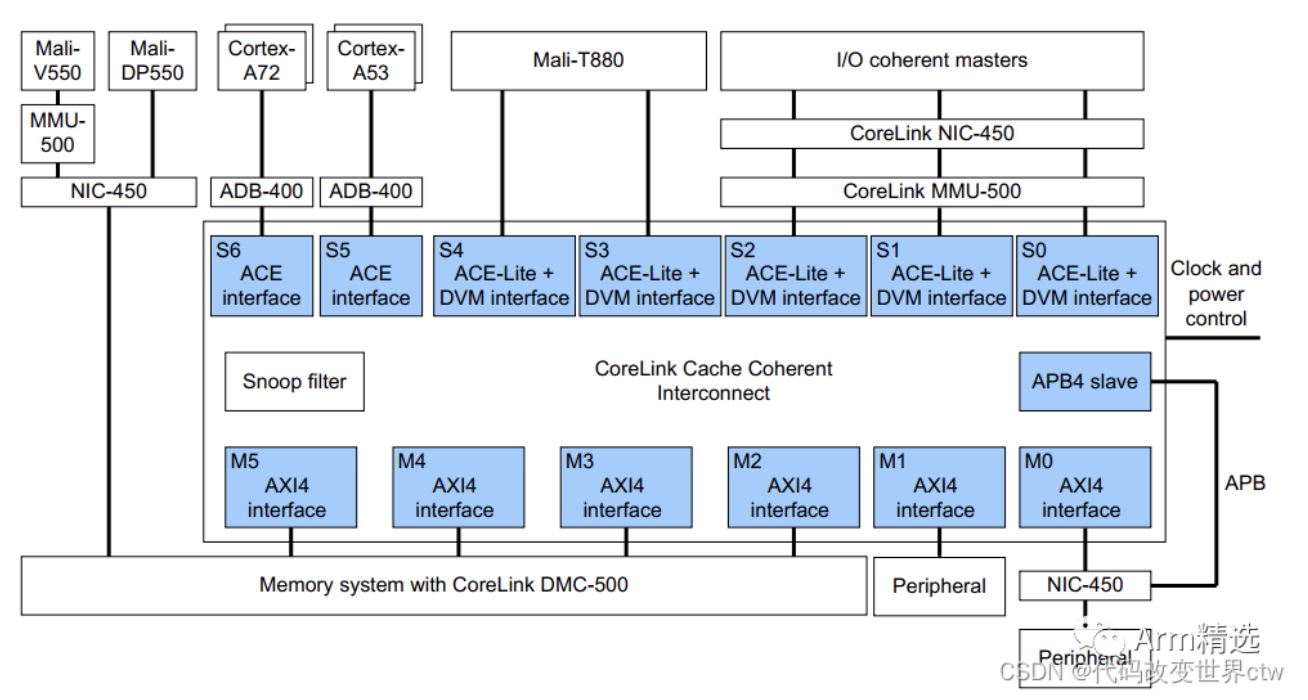

六 CCI的介绍(以CCI-550为例)

CCI-550包含一个包容性监听过滤器(snoop filter),用于记录存储在ACE主缓存。

侦听过滤器可以在未命中的情况下响应侦听事务,并侦听适当的主控只有在命中的情况下。Snoop过滤器条目通过观察来自ACE主节点的事务来维护以确定何时必须分配和取消分配条目。

侦听过滤器可以响应多个一致性请求,而无需向所有人广播ACE接口。例如,如果地址不在任何缓存中,则监听过滤器会以未命中和将请求定向到内存。如果地址在处理器缓存中,则请求被视为命中,并且指向在其缓存中包含该地址的ACE端口。

图11

图12

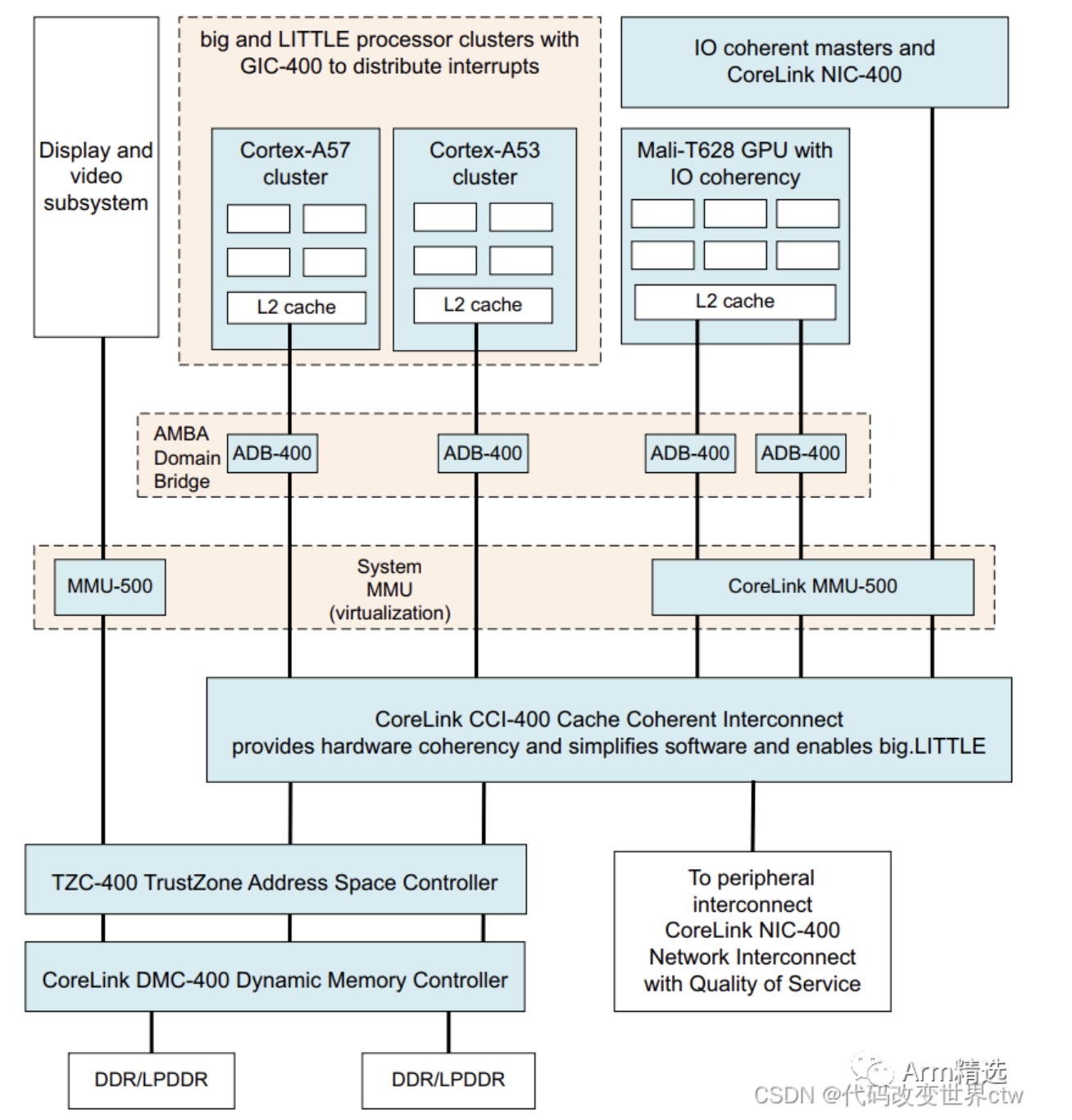

七 经典示例框图

图13

-

处理器

+关注

关注

68文章

19485浏览量

231516 -

ARM

+关注

关注

134文章

9190浏览量

370106 -

RAM

+关注

关注

8文章

1369浏览量

115157 -

ARM架构

+关注

关注

15文章

177浏览量

36522 -

Cortex-A53

+关注

关注

0文章

33浏览量

21431 -

cache技术

+关注

关注

0文章

41浏览量

1105

发布评论请先 登录

相关推荐

ARM cortex-A53是否支持硬件预取、整型流水线的个数等相关参数

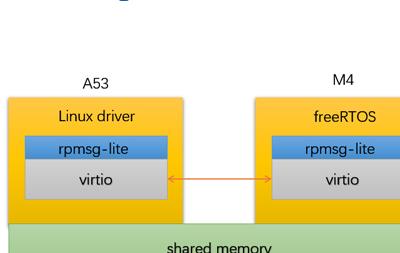

案例分享!IMX8 Cortex-A53与Cortex-M4多核通信开发详解【含源码】

请问可不可以在使用qemu模拟出Cortex-A53的架构来运行rt-thread?

请教大神qemu模拟cortex-A53运行rt-thread出错怎么解决呢?

Cortex-A53循环模型9.6.0版用户指南

ARM Cortex-A53 MPCore技术参考手册

对Cortex-A53处理器的性能分析及特点概述

Cortex-M4F + Cortex-A53异构多核给工业控制带来何种意义?

Arm Cortex-A53 cache的架构解析

Arm Cortex-A53 cache的架构解析

评论