探索背面供电,解决芯片线路设计两难

随着半导体技术的飞速发展,先进制程的角逐已经围绕着5nm以下的工艺展开。随着制程节点由5nm向3nm、2nm发展和演进,芯片制造的难度逐步逼近摩尔定律的物理极限,从制程进步中获得芯片性能提升的难度和成本越来越高。

在越来越小的晶体管中,堆栈层数越来越多,信号线和电源线在多层布线中混合在一起用于连接晶体管与金属层。在越来越有限的芯片面积内,电源线进一步缩小会带来IR Drop问题,晶体管得不到充足的电力供应。

但是如果选择保证电源线厚度避免电压降,又会占用更多片内信号线的布线空间。在以前的制程节点中,这一问题并没有充分暴露出来,而线路层的信号线和电源线设计在3nm、2nm以及更小制程节点的演进下陷入两难的境地。

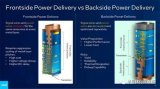

传统的供电线路是在正面进行布线,这种供电技术会影响到金属层的资源的分配,在电路设计越来越复杂的情况下如何处理信号网络跟供电网络之间的资源排挤问题,是芯片进一步微缩的关键,也是芯片制造面临的主要挑战之一。

为了解决这一两难的困境,业界不断探索着新的芯片供电网络方案。背面供电网络BSPDN技术正是解决芯片线路设计两难境地的革命性技术。

背面供电技术BSPDN该技术最早于2019年IMEC研讨会上被提出,是在晶体管三维结构上进行创新,挖掘晶圆背面空间的潜力,将原先和晶体管一同排布的供电网络直接转移到晶体管的背面重新排布。

供电问题在晶圆背面解决,IR Drop效应明显下降,芯片性能得以改善,芯片的正面只需要专注于信号互连。

背面供电技术能带来的优势远远不止解决供电问题IR Drop这么单一,物理设计上的改善,能够大幅提高芯片利用率,减少时序拥堵等问题;背面供电同时缩减了金属线长,这意味着时钟功耗能够降低、缓冲器数量减少和主动功耗降低。

综合这些所有的优势点,采用背面供电技术和采用传统供电技术相比,芯片的性能、能效等系统级指标均能够大幅提升,功耗、面积得以进一步降低。

巨头竞争,抢攻背面供电技术高地

从目前布局开发背面供电技术几家巨头的进度来看,英特尔是在这条赛道上最激进也有望最先落地背面供电技术应用的一方。根据英特尔目前已经公布的信息,其独家的背面供电技术PowerVia将用于18A、20A工艺节点,并且英特尔已经率先在产品级测试芯片上实现了背面供电。

英特尔官方宣布该技术将在2024年20A制程节点上正式落地应用,这比三星和台积电暂定的背面供电技术推出时间都要早。

根据英特尔的测试,PowerVia将平台电压降低了30%,并带来了6%的频率增益。同时测试中芯片大部分区域的标准单元利用率都超过了90%,同时晶体管体积缩小,单元密度大幅增加。为此,英特尔还开发了新的散热技术保证散热。

当前背面供电技术还面临着良率和可靠性等方面的挑战,不过从英特尔目前已经公布的测试来看,PowerVia的良率和可靠性已经较为成熟。所以英特尔在明年正式使用PowerVia背面供电技术配合20A制程节点上线把握性还是很大的。

在先进制程的竞争中,三星同样不甘示弱,其背面供电技术已经在紧锣密鼓地开发中。根据相关消息,三星目前正在针对背面供电技术做市场需求调查,在确保需求充分后,背面供电技术可能会应用到计划于2025年量产的2nm中以解决使用2nm工艺造成的布线拥塞问题,计划于2027年量产的1.4nm工艺使用背面供电技术是可以确定的。

根据三星披露的其研发的背面供电技术测试数据,两个基于ARM架构的处理器,采用背面供电技术后,相比采用传统供电方式,芯片面积分别缩小了10.6%和19%。这意味着内部的集成度和性能都能有不小的提升。同时,背面技术的应用使布线长度减少了接近10%,这也能带来额外的性能优势。

作为另一家巨头,台积电也在背部供电上进行着布局,但在技术推进上稍显保守。根据台积电此前公布的规划,台积电会在2026年推出一个N2P制程节点,同时在这个工艺上,背面供电技术将被引入进来。

根据台积电透露的相关技术数据,N2P制程技术将通过背后供电技术能够有效减少IR Drop和改善信号,芯片性能提高了10%—12%,并将逻辑面积减少10%—15%。虽然推出时间有些落后,但在背面供电技术的前期准备上,台积电已经做了不少相关的技术储备。

三家巨头中目前在背面供电技术最领先的无疑是英特尔,不论是从披露的相关技术进度、成熟度,还是从量产落地时间来看,英特尔目前都还是很有优势的,相比其他厂商有着两年左右的领先。尤其是在良率和可靠性上,英特尔目前是最具把握性的。

先进制程的角逐,将在2025年之后,各家2nm以及更先进节点芯片量产后进入白热化。而背面供电技术的成熟度无疑会影响各个巨头在先进制程角逐中的话语权。

小结

虽然它的实现涉及调试、散热等诸多难度很高的挑战,但背面供电技术能够带来的优势同样非常明显,使用背面供电技术的芯片在性能和能效上获得极大的提升,继续逼近着摩尔定律的极限。

用更少的能量实现多的扩展性能,该技术成熟后能给半导体工艺带来的改变,或许不止这些现在已经被发掘出来的优势。背面供电技术也被视为继续开发更精细工艺节点技术的基本技术,成为现在芯片晶圆厂正在全力竞争又一个技术高地。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

英特尔

+关注

关注

60文章

9879浏览量

171413 -

台积电

+关注

关注

43文章

5608浏览量

166080

发布评论请先 登录

相关推荐

消息称英特尔提议与三星建立“晶圆代工联盟”,挑战台积电

英特尔已与三星电子高层接洽,提议组建“代工联盟”,对抗市场霸主台积电。英特尔和三星的代工业务都已

英特尔计划与三星组建代工联盟,意在制衡台积电

近期,韩国媒体Maeil Business Newspaper透露了一则重磅消息:英特尔主动接触三星电子,意在携手打造“代工联盟”,共同挑战当前代工市场的霸主台积

今日看点丨ASML今年将向台积电、三星和英特尔交付High-NA EUV;理想 L9 出事故司机质疑 LCC,产品经理回应

)。根据ASML发言人透露,该公司财务长Roger Dassen 在最近一次的电话会议上向分析师说,公司最大的三个客户──台积

发表于 06-06 11:09

•866次阅读

Rapidus对首代工艺中0.33NA EUV解决方案表示满意,未采用高NA EUV光刻机

在全球四大先进制程代工巨头(包括台积电、三星电子、英特尔以及Rapidus)中,只有

台积电、英特尔引领半导体行业先进封装技术创新

这一联盟目前有超过120家企业加盟,包括台积电、三星、ASE、AMD、ARM、高通、谷歌、Meta(Facebook)、微软等业界翘楚,由

台积电营收超越英特尔和三星,首次成为全球最大半导体制造商

报告指出,台积电 2023 年营收达到 693 亿美元(当前约 4989.6 亿元人民币),超过了英特尔的 542.3 亿美元(当前约 3904.56 亿元人民币)和

芯片先进制程之争:2nm战况激烈,1.8/1.4nm苗头显露

随着GPU、CPU等高性能芯片不断对芯片制程提出了更高的要求,突破先进制程技术壁垒已是业界的共同目标。目前放眼全球,掌握先进制程技术的企业主

英特尔20A、18A工艺流片,台积电面临挑战

英特尔的Intel 20A和Intel 18A工艺已经开始流片,意味着量产阶段已经不远。而2nm工艺和1.8nm工艺的先进程度无疑已经超过了三星和台

背面供电成先进制程竞争又一技术高地,英特尔先发制人,台积电、三星加码跟进

背面供电成先进制程竞争又一技术高地,英特尔先发制人,台积电、三星加码跟进

评论