本文介绍一个FPGA 开源项目:Micro Blaze最小系统。MicroBlaze是Xilinx提供的一个软核IP,该软核是由FPGA片内逻辑资源组成,其功能相当于一个CPU。利用Micro Blaze,设计师可以轻松实现一些FPGA难以实现的复杂算法。

下面围绕各IP核参数配置、Block Design的创建、以及Xilinx SDK应用工程的创建进行简要介绍。

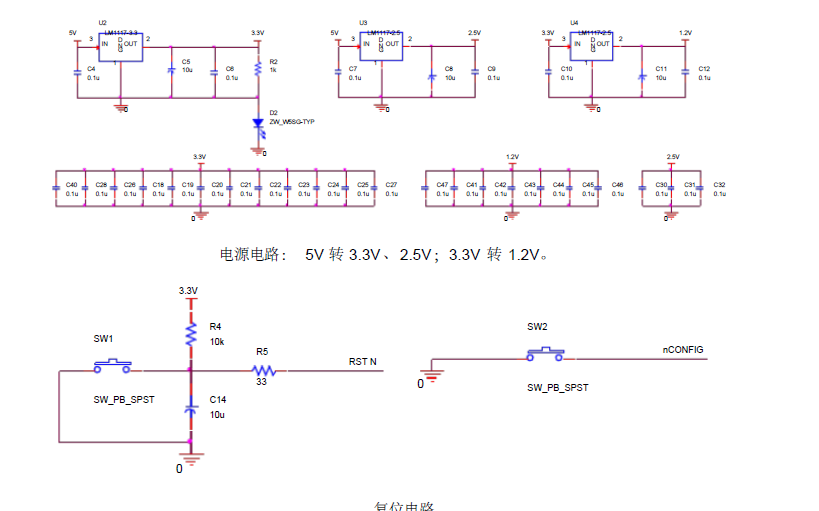

01软硬件平台

02Block Design

搭建MicroBlaze最小系统主要用到以下几个IP核:Clocking Wizard、 MIG 7 Series、 MicroBlaze、AXI Uartlite。

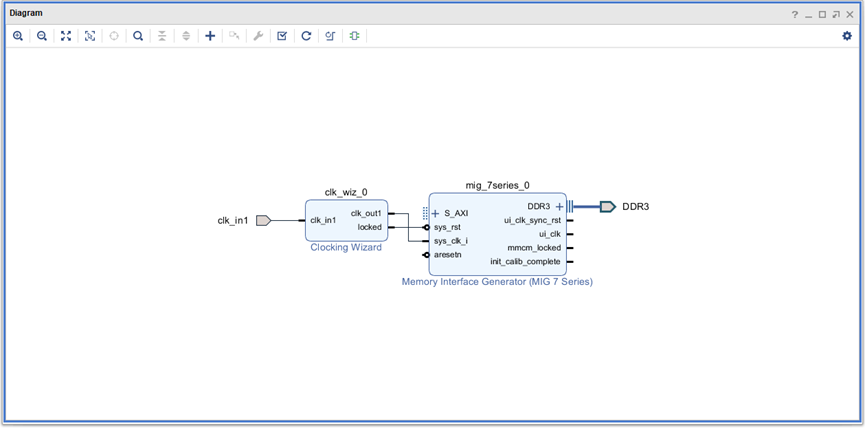

2.1 时钟和MIG

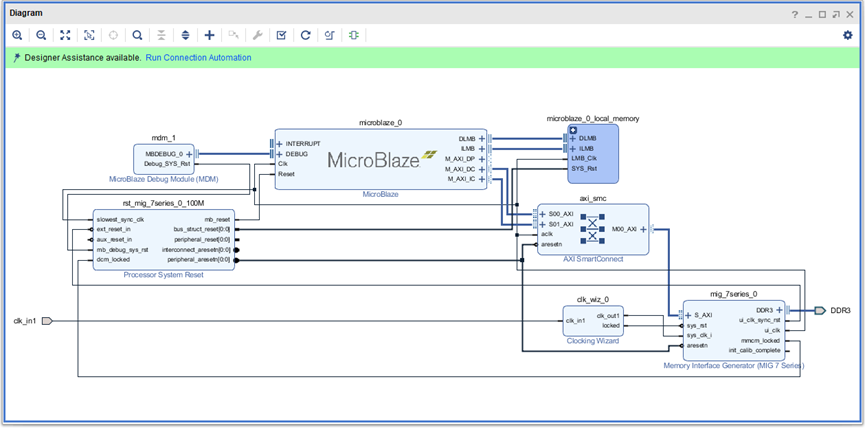

首先,在BD工程中添加Clocking Wizard以及MIG IP核,对于IP核参数的具体配置在前面的文章中有详细介绍。然后将时钟模块的输出时钟信号以及复位信号与MIG IP进行连接,如下图所示:

2.2 MicroBlaze

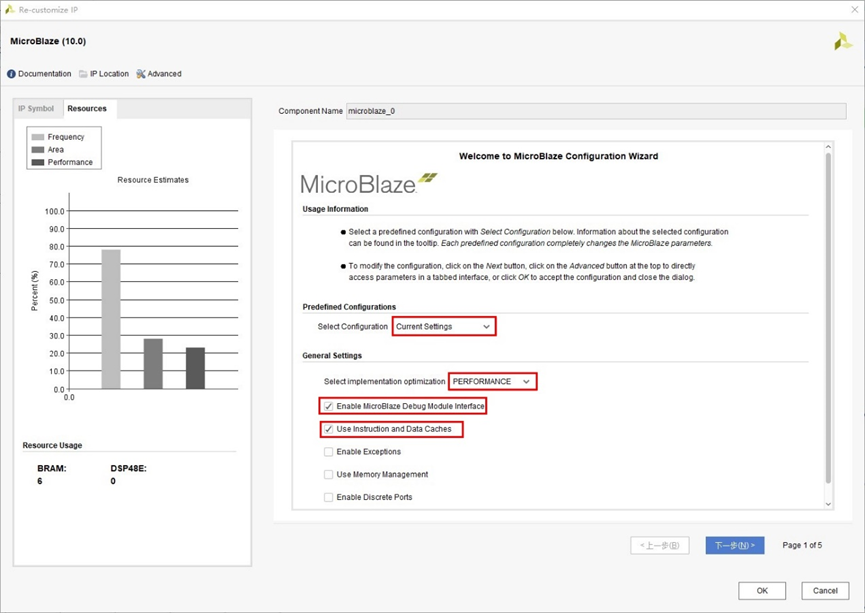

在Block Design中添加MicroBlaze IP核,并进行如下参数配置:

- Predefined Configurations :选择 Current Settings ;

- 优化方式 :选择默认的 PERFORMANCE 即可;

- 启用调试接口 :Enabla MicroBlaze Debug Module Interface;

- 启用指令和数据缓存;

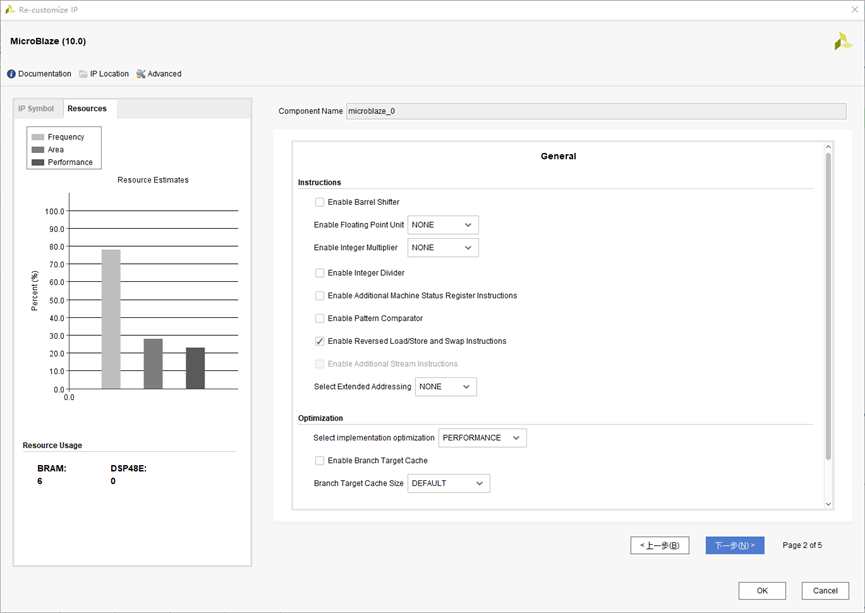

- General 参数配置:如上图所示,保持默认配置即可;

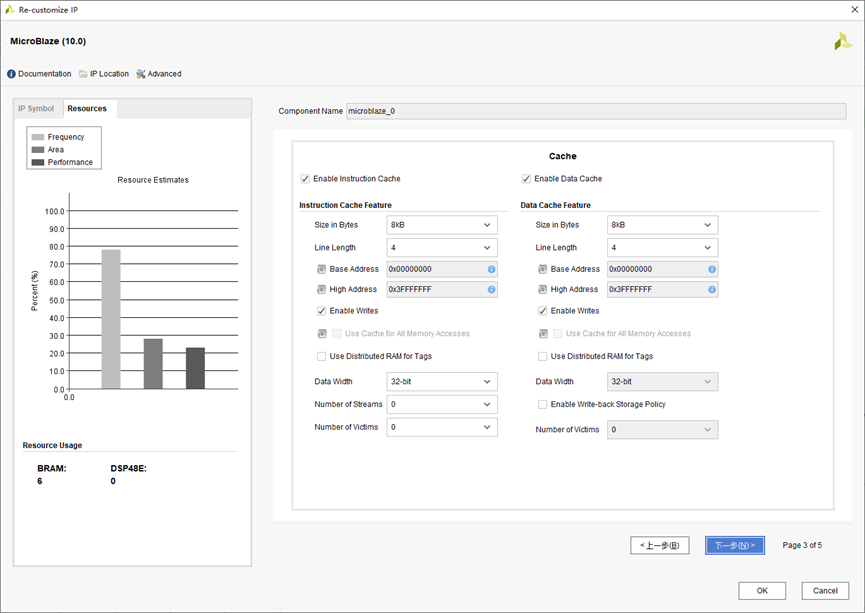

- 对于 指令和数据缓存 的配置 : 同样保持默认的参数配置;

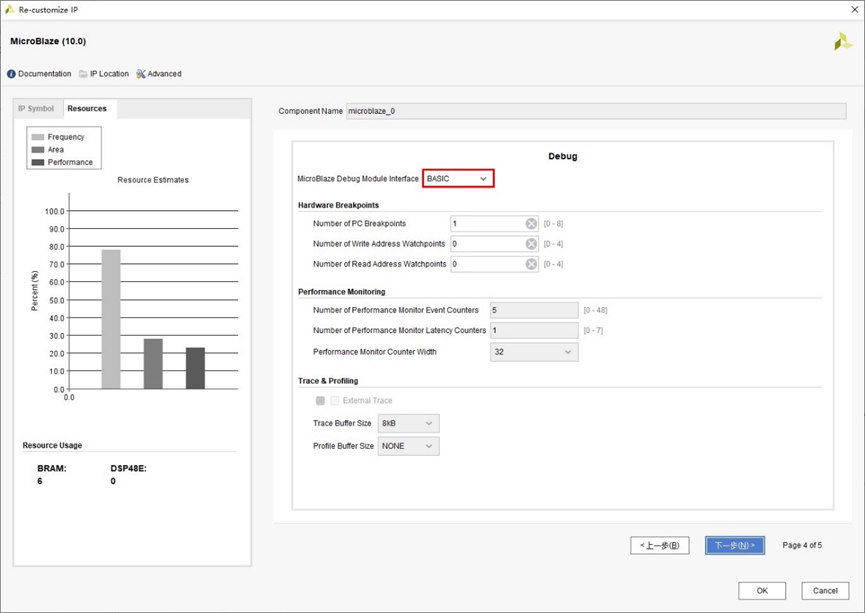

- Debug :调试接口参数配置,选择 BASIC ,其余参数采用默认配置;

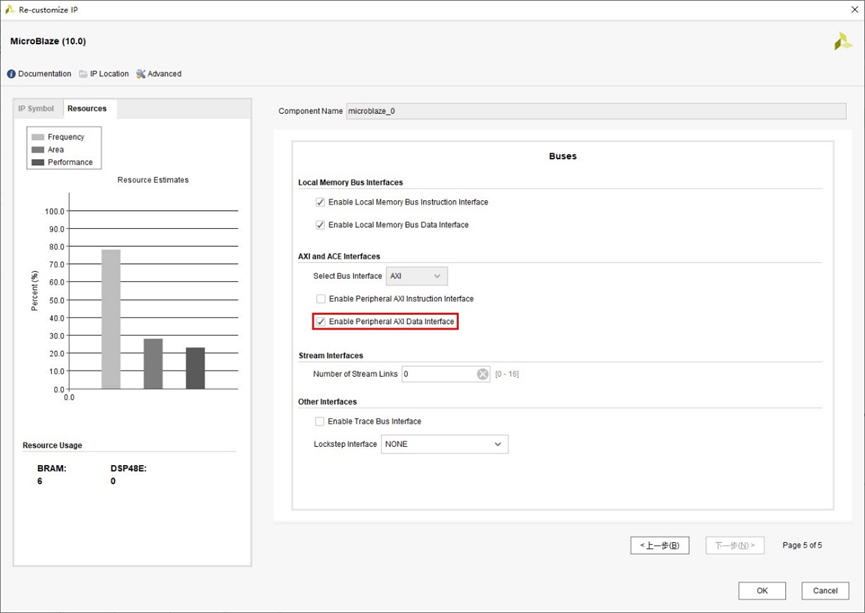

- Buses :启用AXI数据流接口,通过该接口,MicroBlaze访问AXI-Lite总线数据;

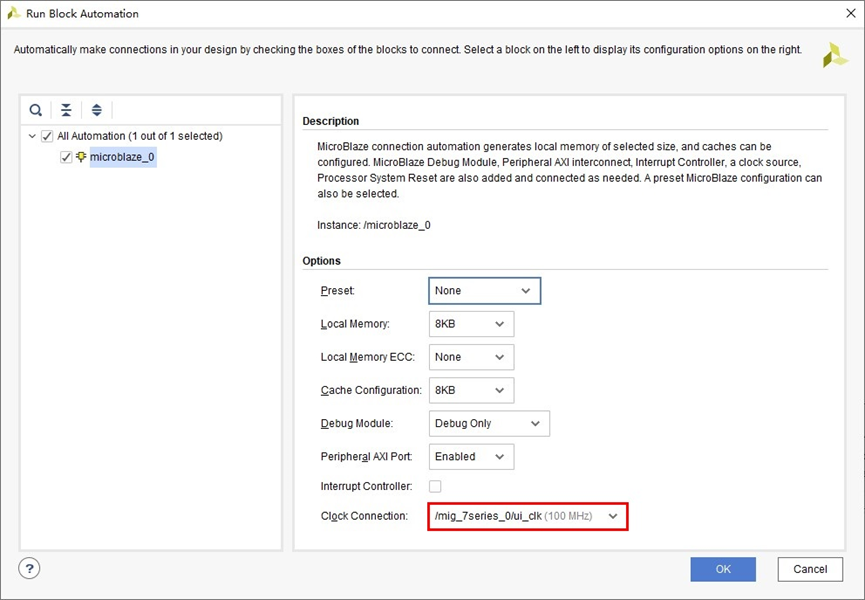

然后,点击 Run Block Automation ,MicroBlaze的输入时钟选择MIG IP核提供的100MHz用户时钟。

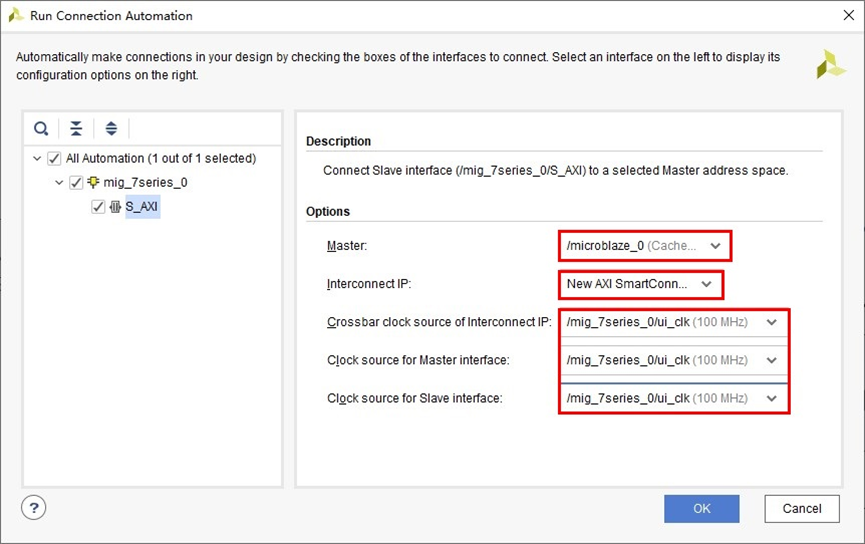

点击 Run Connection Automation ,参数按照上图所示进行配置。自动连线完成后,得到下图所示的BD工程:

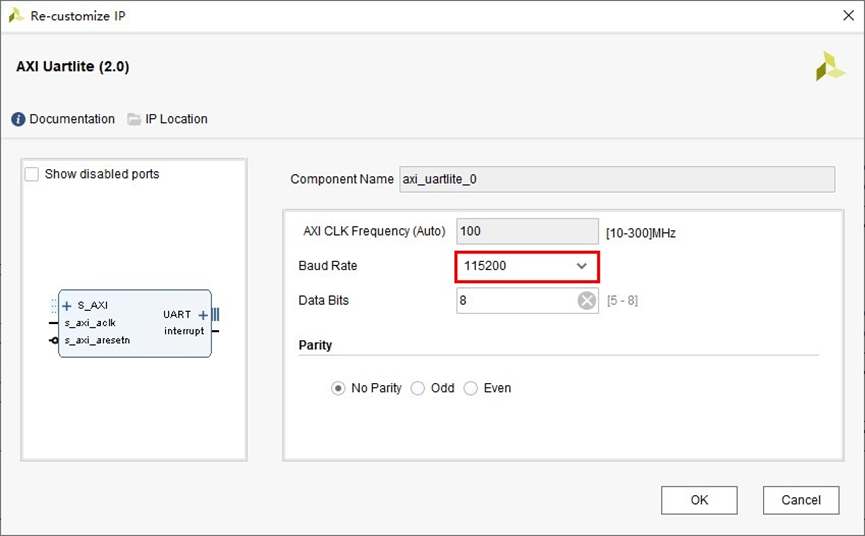

2.3 AXI Uartlite

在该最小系统中,额外添加一个串口外设:AXI Uartlite,通过串口输出验证MicroBlaze最小系统是否正常工作,如果有需要还可以添加其它外设,如GPIO、INTIC等。

需要对串口波特率进行配置,这里选择115200,其余参数默认即可:

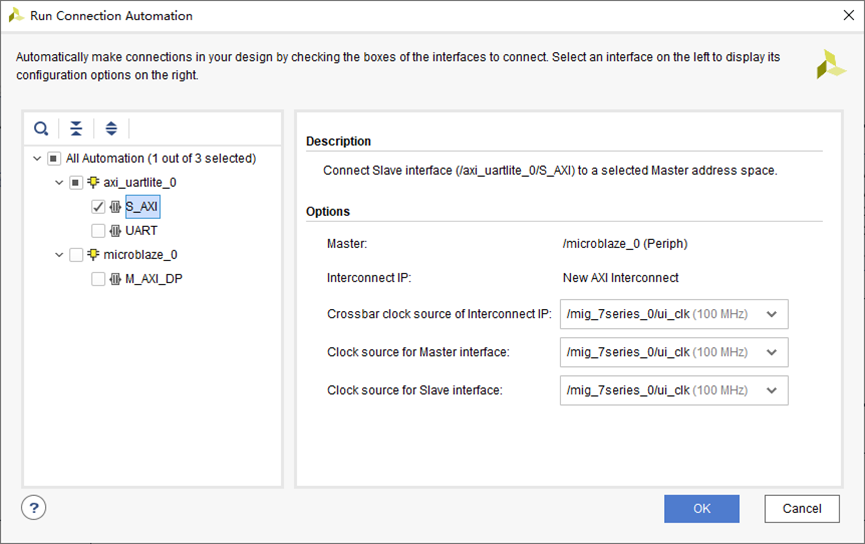

然后点击 Run Connection Automation ,将串口模块AXI时钟选择为MIG输出的100M时钟:

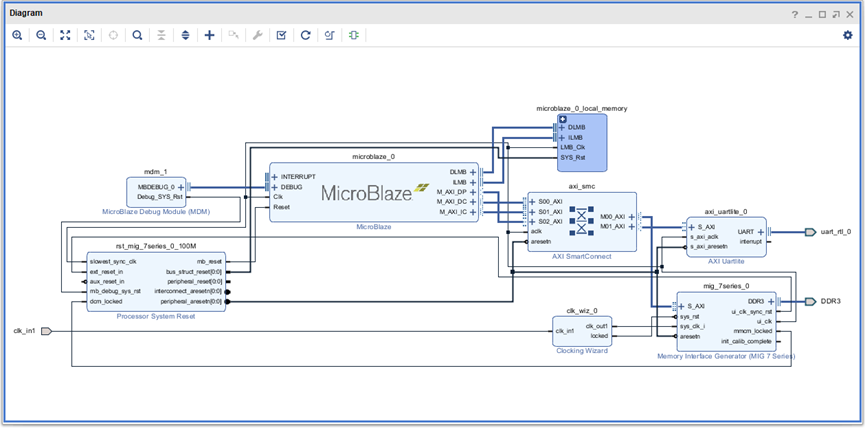

2.4 Block Design

自动连线完成后,最终得到的BD工程如下图所示:

然后依次执行 Reset Output Products , Generate Output Products, Create HDL Wrapper 。对输入时钟以及串口的管脚进行配置后,最后点击生成bit流文件。

03创建Xilinx SDK工程

生成bit流文件后,点击File->Export->Export Hardware,并勾选 Include bitstream ,然后单击 Launch SDK,打开SDK软件。

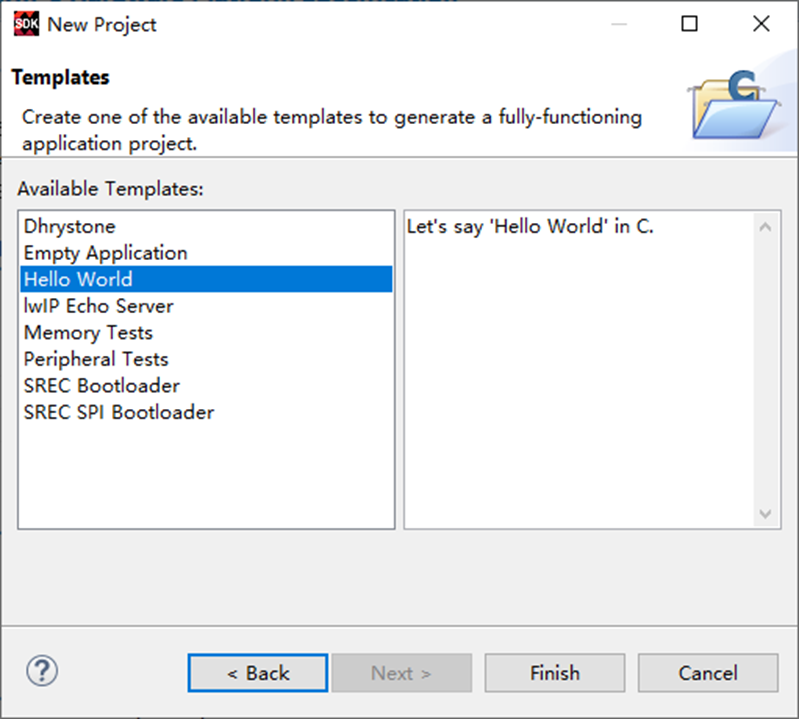

在SDK软件中,点击File->New->Application Project,创建应用程序。输入工程名字,然后点击 Next 。在提供的例程里,选择 Hello World ,验证串口输出功能。

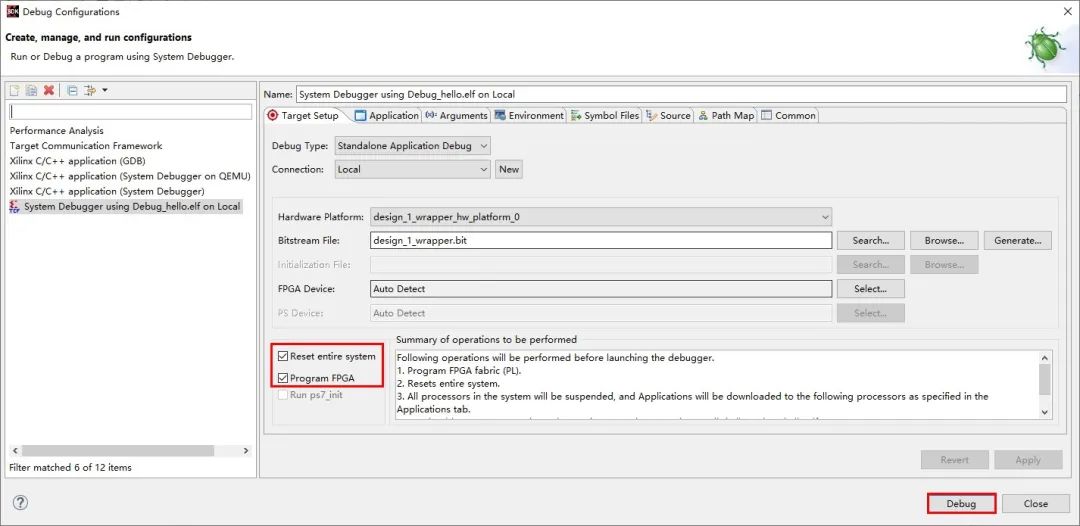

工程创建好后,选择 Debug As -> Run Configurations,勾选 Reset entire system,以及Program FPGA。然后点击 Debug。

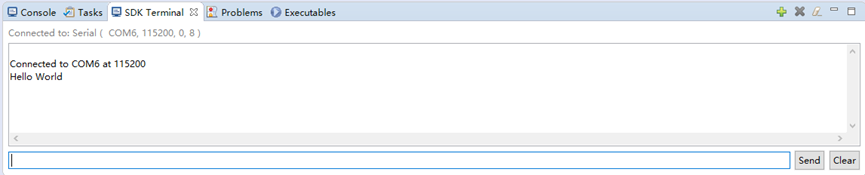

在SDK Terminal中添加好串口并配置波特率115200,运行代码后,串口打印输出“Hello World“。

04实现功能

该Vivado工程主要是搭建了一个MicroBlaze最小系统并添加了AXI串口模块,在Xilinx SDK软件中利用C语言实现了串口打印功能。后续在此工程基础上,可以利用MicroBlaze软核实现更加复杂的功能。

-

FPGA

+关注

关注

1629文章

21748浏览量

603969 -

Xilinx

+关注

关注

71文章

2167浏览量

121601 -

MicroBlaze

+关注

关注

3文章

68浏览量

21570 -

IP核

+关注

关注

4文章

329浏览量

49520 -

最小系统

+关注

关注

9文章

252浏览量

29105

发布评论请先 登录

相关推荐

FPGA最小系统板设计资料下载

STM32最小系统搭建(原理图)

Nios ii最小系统搭建教程

基于FPGA搭建Micro Blaze最小系统

基于FPGA搭建Micro Blaze最小系统

评论