本文开源一个FPGA项目:基于AXI总线的DDR3读写。之前的一篇文章介绍了DDR3简单用户接口的读写方式:《DDR3读写测试》,如果在某些项目中,我们需要把DDR挂载到AXI总线上,那就要通过MIG IP核提供的AXI接口来读写DDR。

下面围绕Vivado BD工程的搭建以及各个IP的使用简单介绍一下该项目。

01软硬件平台

- 软件平台:Vivado 2017.4;

- 硬件平台:XC7A35TFTG256-1;

02创建Vivado BD工程

2.1 Clocking Wizard

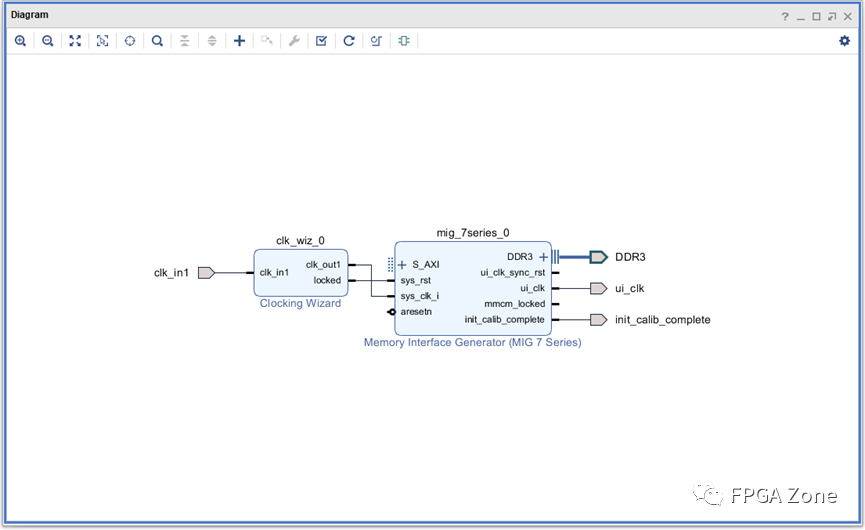

首先在BD工程中添加Clocking Wizard IP核,用于给MIG IP核提供200M时钟以及复位信号。

2.2 MIG IP

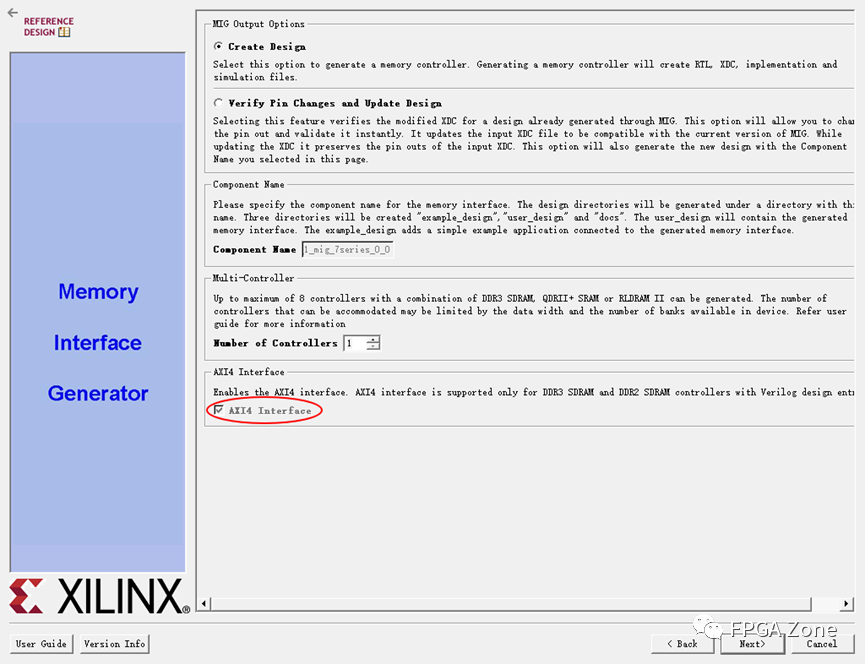

添加MIG IP核,接口已经默认配置成AXI接口。

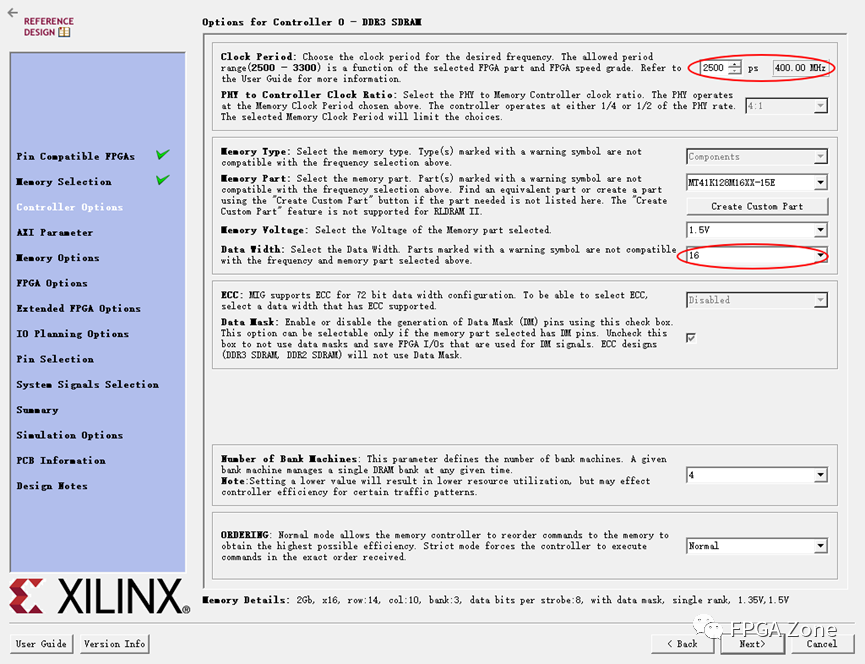

- Clock Period:这里配置成400Mhz;

- Data Width:采用16bits;

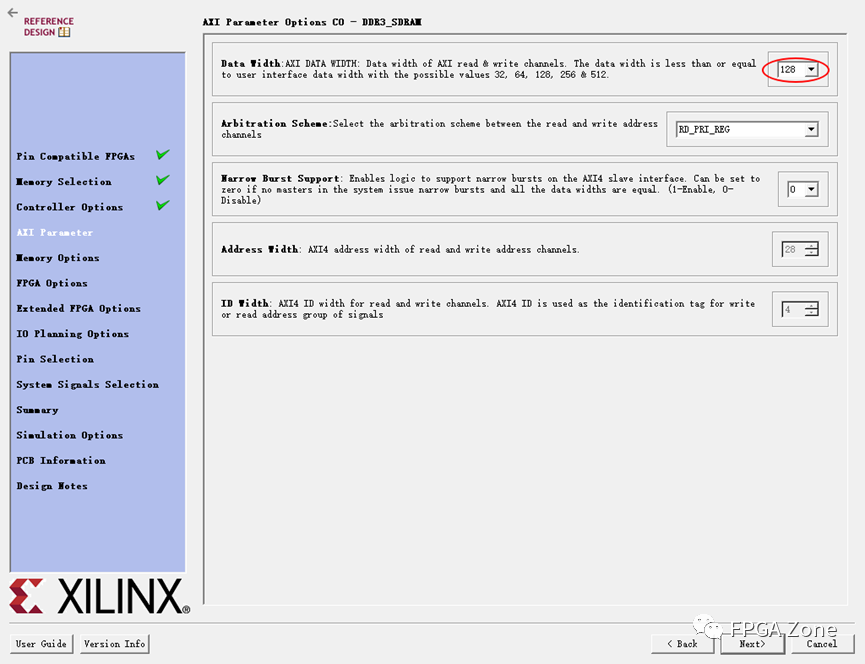

- AXI参数配置:Data Width 配置成128 bits。DDR3是双沿工作,并且工作频率和用户时钟频率为4:1,因此这里AXI总线位宽最大可配置为16bits42=128bits;

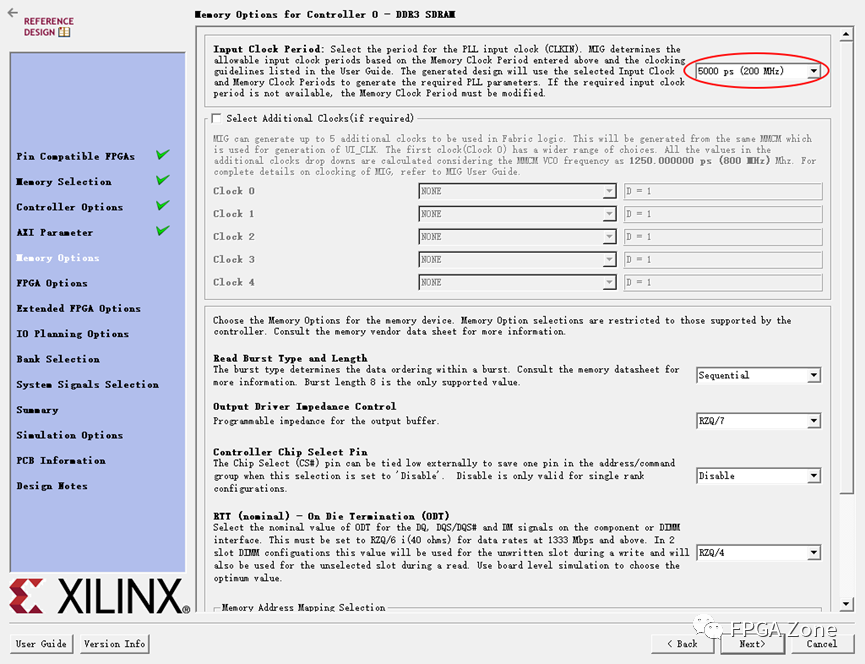

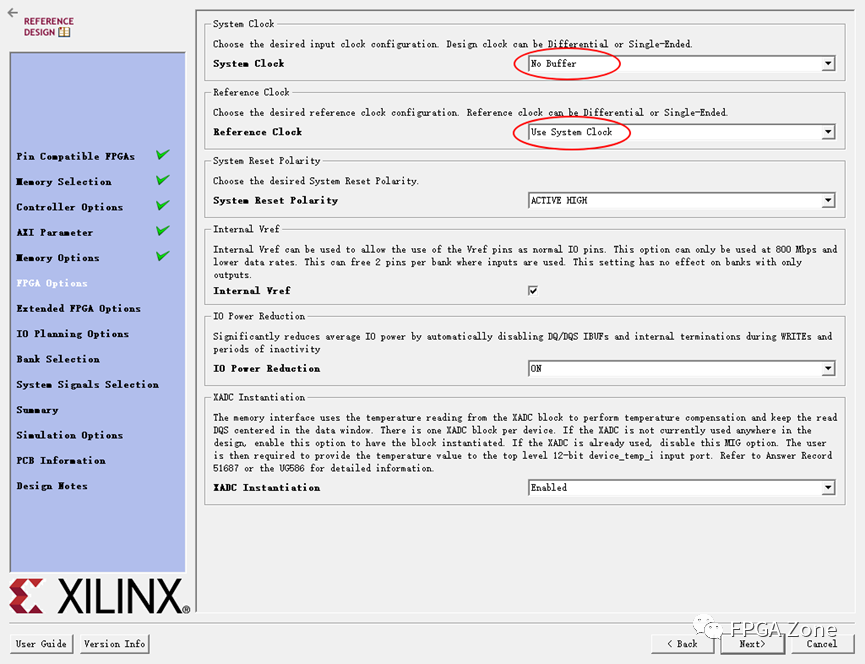

- MIG IP核输入时钟:200MHz;

- 系统时钟:No Buffer;

- 参考时钟:选择Use System Clock;

配置好MIG IP后,将其与时钟模块(Clocking Wizard)进行连接。

2.3 FDMA

FDMA 是米联客基于AXI4总线协议设计的一个DMA控制器,将其挂载到AXI4总线上,可以方便地对PL或者PS端DDR进行读写。

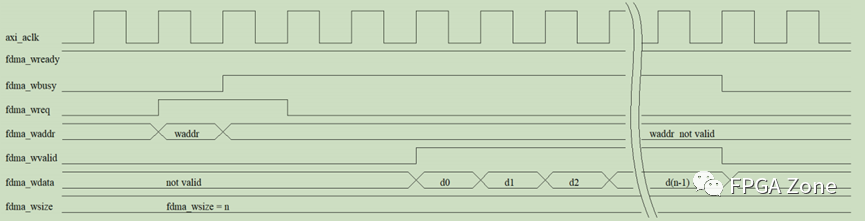

- FDMA写时序

FDMA写时序如下图所示。将fdma_wready拉高,当fdma_wbusy为低的时候表示总线空闲,此时可以拉高fdma_wreq,同时设置起始地址和数据长度。当fdma_wvalid为高时,写入有效数据。最后一个数据写完,fdma_wvalid和fdma_wbusy会拉低。

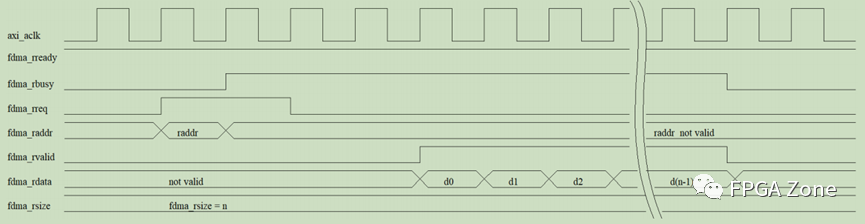

- FDMA读时序

FDMA读时序如下图所示。将fdma_rready拉高,当fdma_rbusy为低的时候表示总线空闲,此时可以拉高fdma_rreq,同时设置起始地址和数据长度。当fdma_rvalid为高时,输出有效数据。最后一个数据读完,fdma_rvalid和fdma_rbusy会拉低。

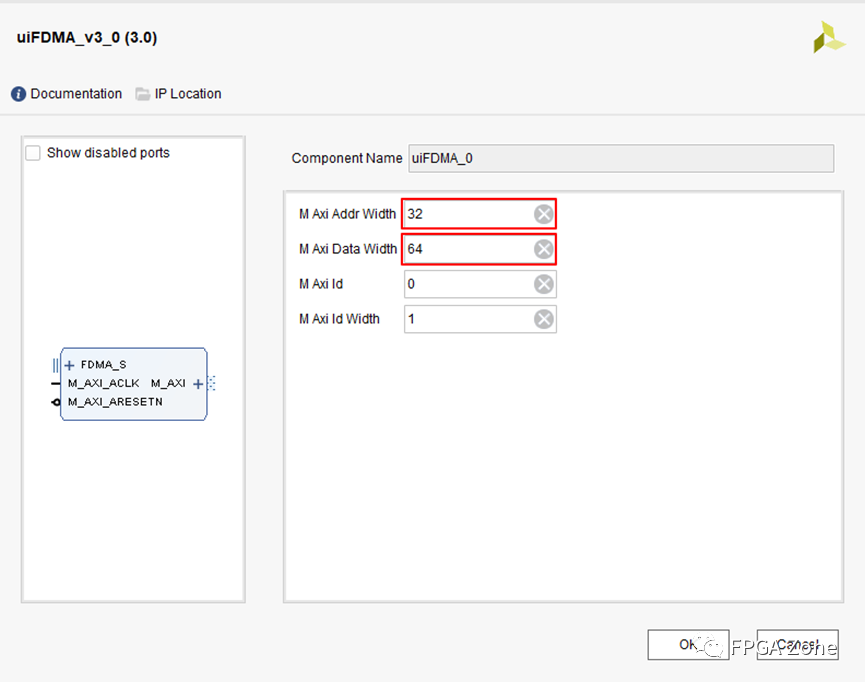

对FDMA IP参数进行配置:这里采用32位宽地址线以及64位宽数据线进行测试。

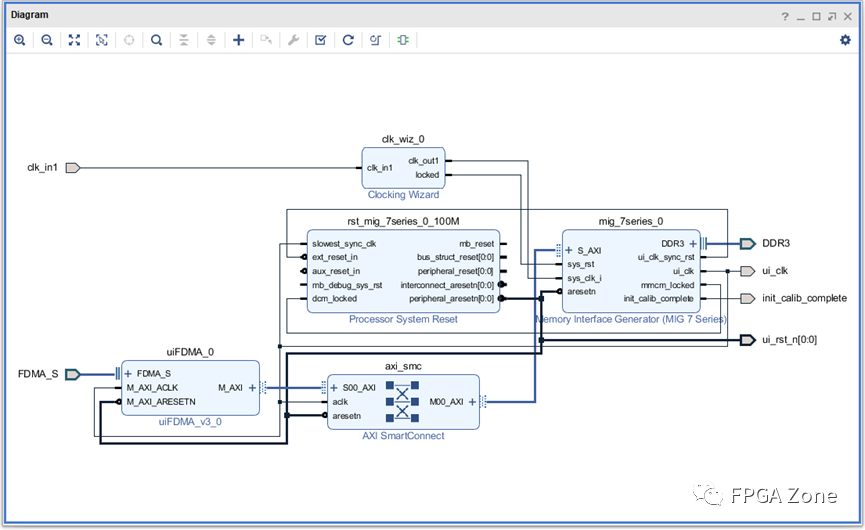

然后,将FDMA连接到AXI总线上,并通过axi_smc IP进行数据位宽转换。将需要调用的接口接出来,得到以下BD工程。

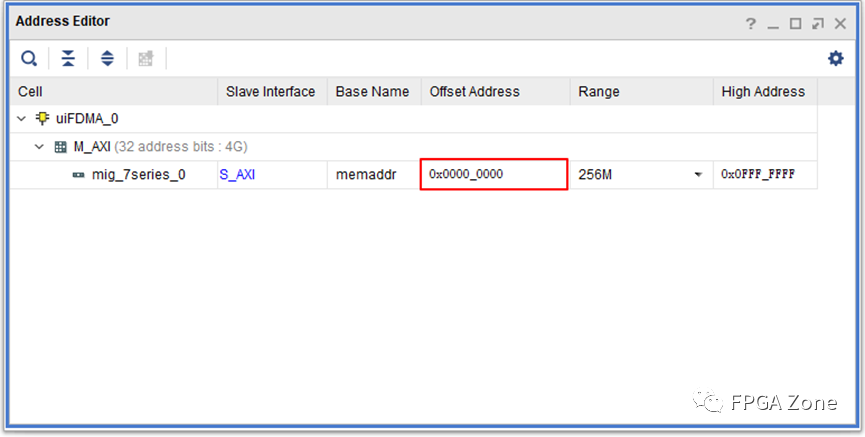

配置起始地址为0x0000_0000,令DDR的读写地址从0开始。

最后在顶层文件中添加用户逻辑,并生成bit文件。

03功能测试

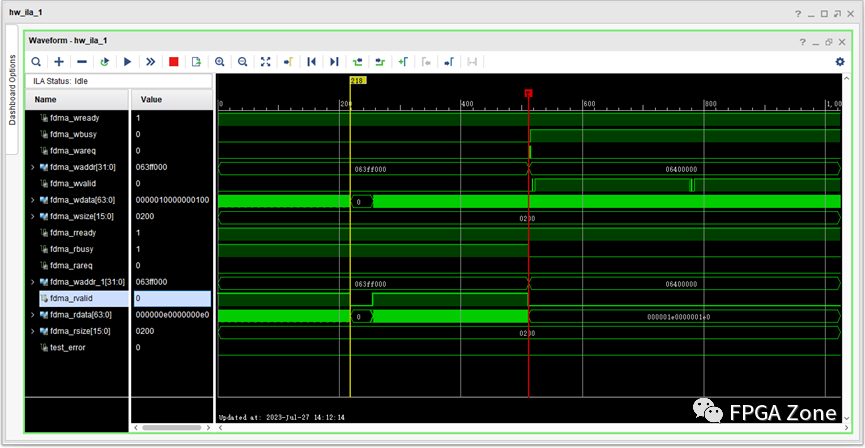

该Vivado工程实现的功能是基于AXI总线对DDR3进行连续读写测试,每次突发读写长度为512*64bits,地址范围为0~100M。FPGA板上测试结果如下图所示。

-

FPGA

+关注

关注

1630文章

21796浏览量

605872 -

DDR3

+关注

关注

2文章

276浏览量

42380 -

接口

+关注

关注

33文章

8691浏览量

151868 -

IP核

+关注

关注

4文章

331浏览量

49621 -

AXI总线

+关注

关注

0文章

66浏览量

14308

发布评论请先 登录

相关推荐

基于FPGA的DDR3多端口读写存储管理系统设计

【紫光同创国产FPGA教程】【第十章】DDR3读写测试实验

cyclone V控制DDR3的读写,quartusII配置DDR3 ip核后,如何调用实现DDR3的读写呢,谢谢

玩转Zynq连载37——[ex56] 基于Zynq的AXI HP总线读写实例

【FPGA DEMO】Lab2:DDR3读写实验

紫光同创FPGA入门指导:DDR3 读写——紫光盘古系列50K开发板实验教程

基于FPGA的DDR3多端口读写存储管理的设计与实现

关于期货行情数据加速处理中基于FPGA的DDR3六通道读写防冲突设计详解

基于AXI总线的DDR3读写测试

基于AXI总线的DDR3读写测试

评论