帧率(FrameRate)是图像领域中的定义,通俗来讲就是指动画或视频每秒显示的画面数(帧数Frames),即FPS( Frame perSecond)。帧率越高,则每秒钟显示的帧数越多,所显示的动作就会越流畅。

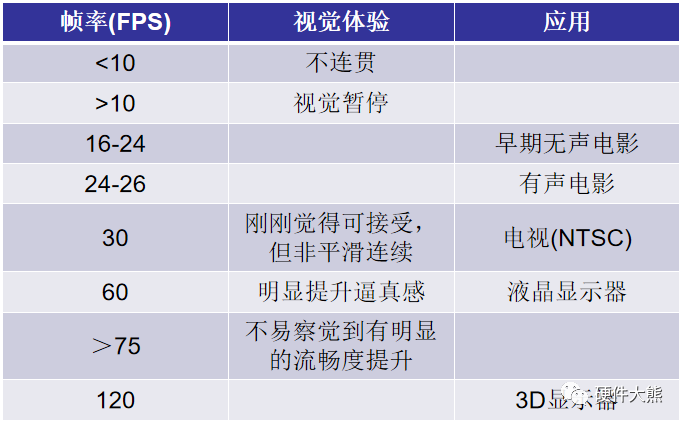

不同帧率层级对照表

帧率高低的视觉差异 如下一个动图,不同帧数的图片播放效果不同,低帧率的图片看起来会有卡顿感。

帧缓冲区大小计算

所谓帧缓冲区就是用来存储像素数据的地方,像素经过渲染后传输到显示屏。当我们在选型芯片做显示驱动时,为了确保显示效果更佳,务必确保帧缓冲区的容量充足,因为更高的像素数量和更高的色深需要更高的RAM和显示接口的数据吞吐率。

帧缓冲区大小 =显示宽度 x显示高度 x (每像素位数/8) B

以一款四寸屏面板开关为例,一个分辨率为480x480具有16bpp色深的单帧显示缓冲区大小为:

480x480x(16/8)=460800 b=460800/1024 =450KB

主控影响帧数的因素 处理能力:CPU或GPU的性能决定了它们能够处理多少图形和计算任务。更强大的处理能力通常意味着更高的帧率。

渲染负担:应用程序的复杂性会影响CPU和GPU的负担,因此如果智慧屏面板达到要更好的渲染效果,则需要考虑是否需要选择多核CPU来进行多线程处理。

驱动程序优化:合适的图形驱动程序可以显著提高性能。更新和优化的驱动程序通常可以提供更好的帧率。

内存:足够的系统内存(RAM)对于处理大型纹理和复杂场景非常重要。不足的内存可能导致性能下降。

散热和温度:CPU和GPU的温度和散热情况会影响它们的性能。过热可能导致性能下降,因此适当的散热解决方案非常重要。

后台任务:在后台运行的任务(如音乐解码、无线透传等)可以占用系统资源,降低显示的性能。

审核编辑:刘清

-

解码器

+关注

关注

9文章

1129浏览量

40670 -

缓冲器

+关注

关注

6文章

1914浏览量

45445 -

RAM

+关注

关注

8文章

1367浏览量

114517 -

FPS

+关注

关注

0文章

35浏览量

11961 -

智慧屏

+关注

关注

2文章

356浏览量

19674

原文标题:智慧屏面板显示技术1:帧率

文章出处:【微信号:A100702108,微信公众号:A100702108】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

abview中VISA的读、写缓冲区是同一个缓冲区吗?

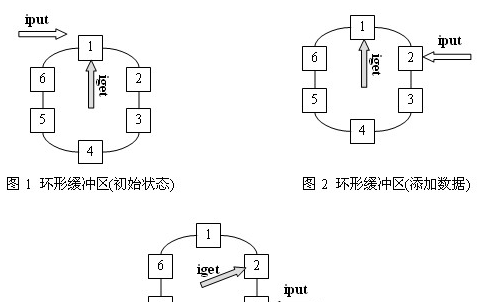

基于ARM和FPGA的环形缓冲区接口设计方案

请问控制DMA来转换缓冲区的因素有哪些?

可变大小缓冲区的内存分配技术

CH565W DVP这一帧数据是如何能被接收完全的?

STM32H735IG Discovery可以使用OctoSPI作为帧缓冲区吗?

为什么无法将帧缓冲区放在靠近每个的外部RAM中?

imx8不支持双帧缓冲区和IPU吗?

一文读懂路由器缓冲区大小的重要性

缓冲区是啥意思 STM32串口数据接收之环形缓冲区

C++环形缓冲区设计与实现

帧缓冲区大小计算 主控影响帧数的因素有哪些?

帧缓冲区大小计算 主控影响帧数的因素有哪些?

评论