本文介绍一个FPGA开源项目:PCIE通信。该工程围绕Vivado软件中提供的PCIE通信IP核XDMA IP建立。Xilinx提供了XDMA的开源驱动程序,可在Windows系统或者Linux系统下使用,因此采用XDMA IP进行PCIE通信是比较简单直接的。

本文主要介绍一下XDMA IP核的使用和Vivado工程的源代码结构。

01软硬件平台

- 软件平台:Vivado 2017.4;

- 硬件平台:XC7Z035FFG676-2;

02IP核参数配置

2.1 XDMA

XDMA (DMA Subsystem for PCI Express) 是Xilinx提供的可用于PCIE2.0,PCIE3.0的SG模式DMA IP核。该IP核可配置AXI4接口或者AXI4-Stream接口,如果配置成AXI4接口,可方便接入AXI总线互联,与DDR进行数据传输。

另外XDMA还提供可选择的AXI4-Lite Master和AXI4-Lite Slave接口。其中AXI4-Lite Master接口可用于实现 PCIE BAR 地址到 AXI4-Lite 寄存器地址的映射,可以用于读写用户逻辑寄存器,AXI4-Lite Slave接口用来将 XDMA 内部寄存器开放给用户逻辑,用户逻辑可以通过此接口访问 XDMA 内部寄存器。

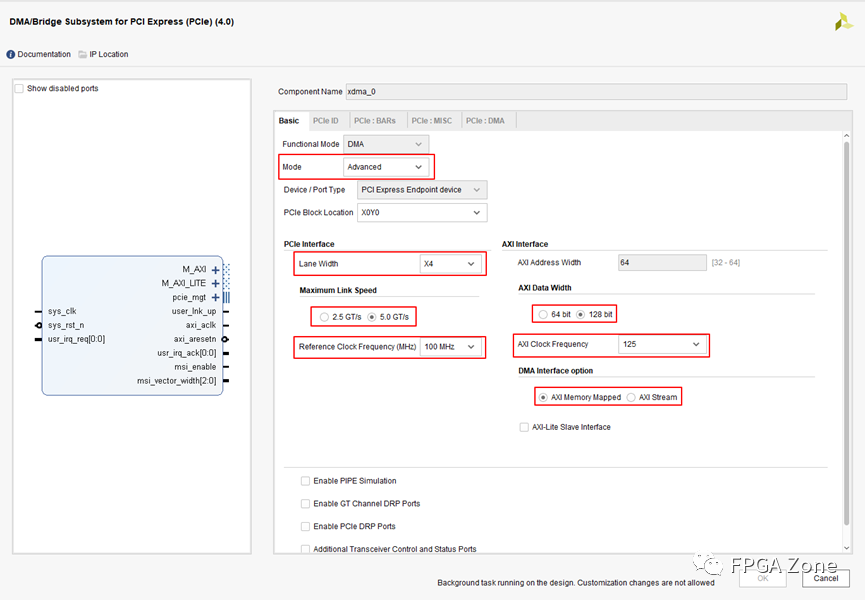

- Mode:选择Advanced;

- Lane Width:根据FPGA硬件型号选择;

- Max Link Speed:选择5.0GT/s;

- Reference Clock:100MHZ;

- DMA Interface Option:选择AXI4接口;

- AXI Data Width:AXI4总线位宽选择128bits;

- AXI Clock:125MHZ;

PCIE ID配置保持默认选项。

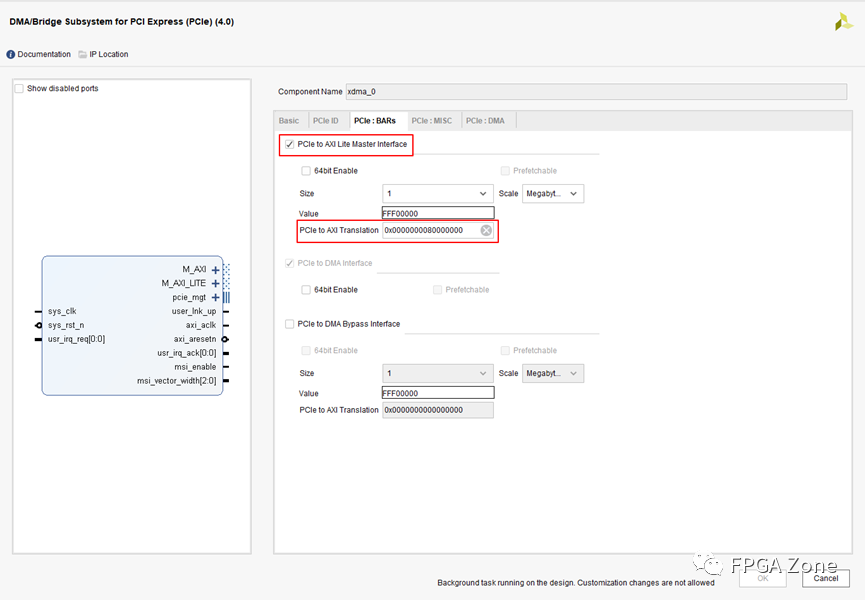

- 选择PCIE to AXI Lite Master Interface;

- 空间大小根据实际需要进行选择;

- PCIE to AXI Translation:BAR地址到AXI地址转换,这里设置为0x8000_0000;

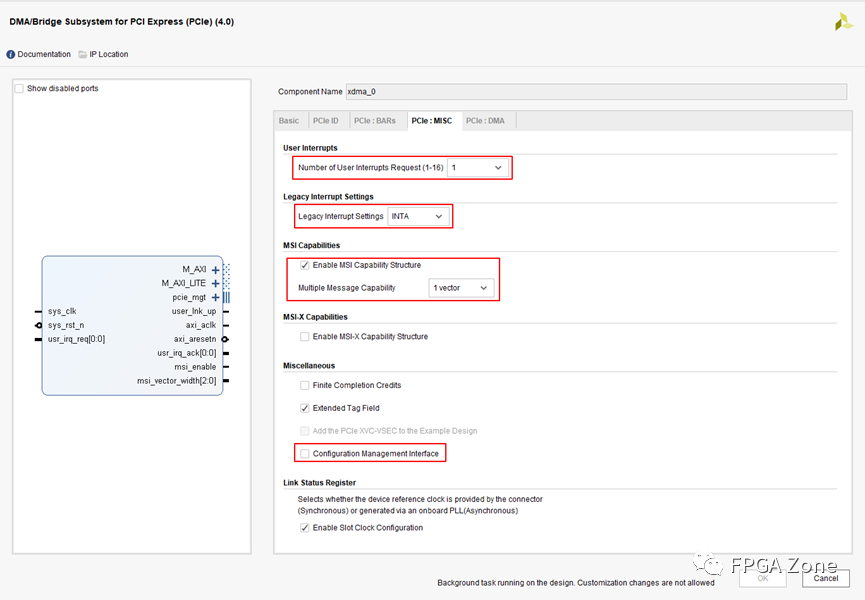

- User Interrupts:用户中断配置,根据实际需求选择;

- Legacy Interrupt:XDMA支持Legacy中断;

- 使能MSI中断;

- Configuration Management Interface不选;

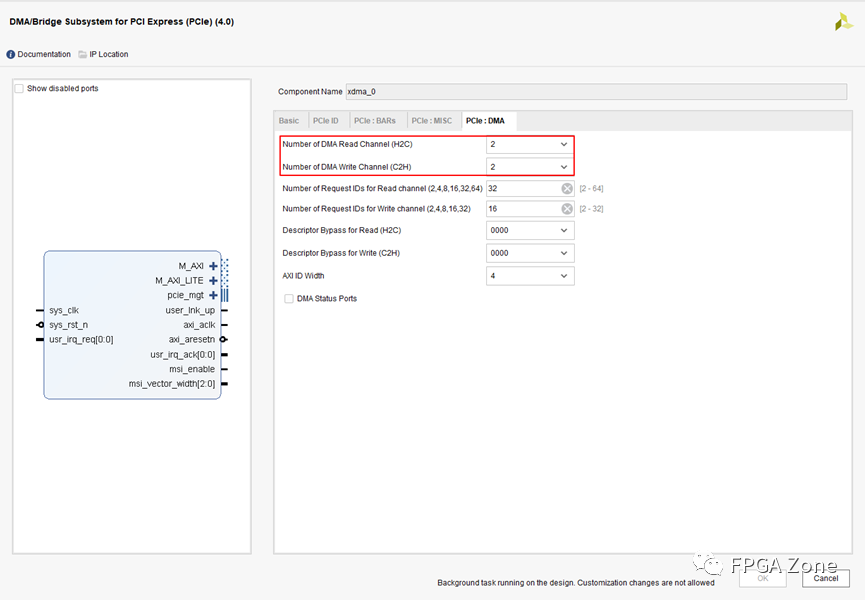

- Number of DMA Read Channel (H2C) 和Number of DMA Write Channel (C2H) :这里选择2,即XDMA 可以提供最多两个独立的写通道和两个独立的读通道;

- 其它选项保持默认;

2.2 MIG 7 Series & AXI BRAM Controller

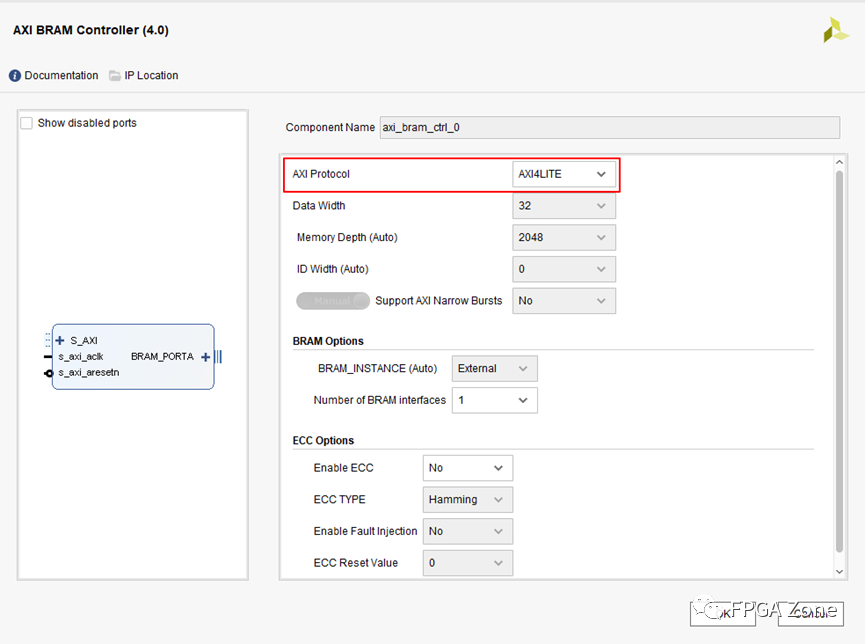

为了测试XDMA IP对AXI4总线以及AXI4-Lite总线读写功能,在本工程中添加了BRAM和MIG IP核。其中AXI BRAM Controller IP配置如下,AXI协议选择AXI4LITE;MIG选择AXI4接口挂载到AXI4总线,实现对DDR的读写。

03工程源码结构

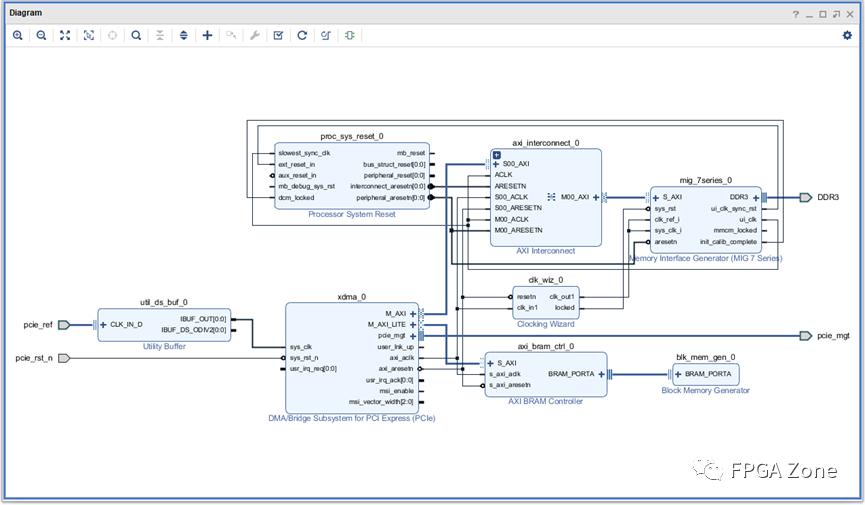

下图为最终搭建好的系统的Block Design。本工程是基于Zynq平台建立,但实际只用到PL端资源,因此也可方便移植到其它FPGA平台使用。

地址配置:DDR地址配置从0开始,BRAM配置从0x8000_0000开始,与XDMA中地址映射保持一致。

04实现功能

该Vivado工程主要用于FPGA PCIE 通信基础功能测试,具体为:上位机端通过PCIE接口实现对FPGA端BAR地址空间以及DMA内存地址空间读写操作。在此工程基础上,可在FPGA端访问DDR等模块缓存的PCIE数据,并进行后续一系列处理。

-

FPGA

+关注

关注

1638文章

21859浏览量

609831 -

Linux

+关注

关注

87文章

11388浏览量

211737 -

WINDOWS

+关注

关注

4文章

3589浏览量

90307 -

通信测试

+关注

关注

0文章

59浏览量

49631 -

PCIe

+关注

关注

16文章

1292浏览量

84011

发布评论请先 登录

相关推荐

FPGA的PCIE接口应用需要注意哪些问题

开发FPGA Kintex-7板子的PCIe与DDR模块高速通信,应该准备些什么?

pc如何通过pcie与FPGA通信

基于AM57x平台的PCIe通信案例(一)

基于AM57x平台的PCIe通信案例(二)

基于C66x平台DSP与FPGA通信测试

寻求fpga大牛开发一个简单的fpga pcie设备

AC701能否通过Artix 7的PCIe链路与PC通信?

如何通过PCIe进行FPGA到PC的通信?

2个PCIE PHY在FPGA中连接可能实现吗?

关于xilinx FPGA pcie测试问题

米尔ARM+FPGA架构开发板PCIE2SCREEN示例分析与测试

基于FPGA的PCIE通信测试

基于FPGA的PCIE通信测试

评论