本文介绍一个FPGA常用模块:SRIO(Serial RapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单介绍一下SRIO IP核的使用和本工程的源代码结构。

由于Vivado中RapidIO IP核需要付费才能使用,因此本文提供完整工程源码。

01软硬件平台

- 软件平台:Vivado 2017.4;

- 硬件平台:XC7K410T...;

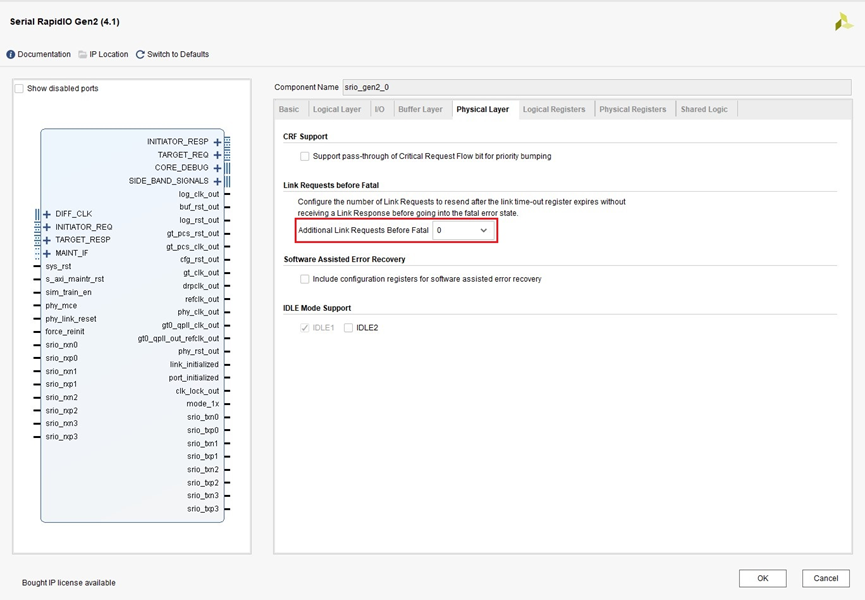

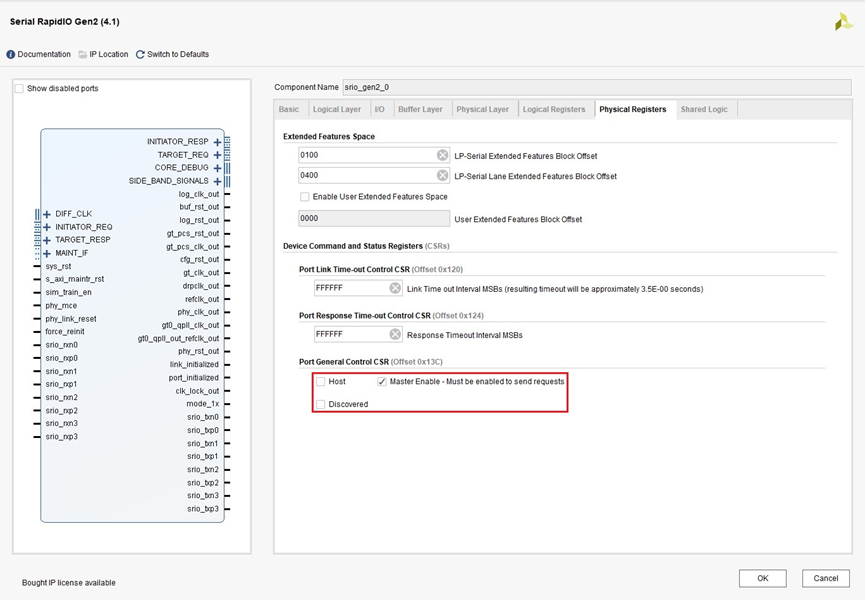

02IP核参数配置

本工程SRIO IP核参数配置如下图所示,仅供参考:

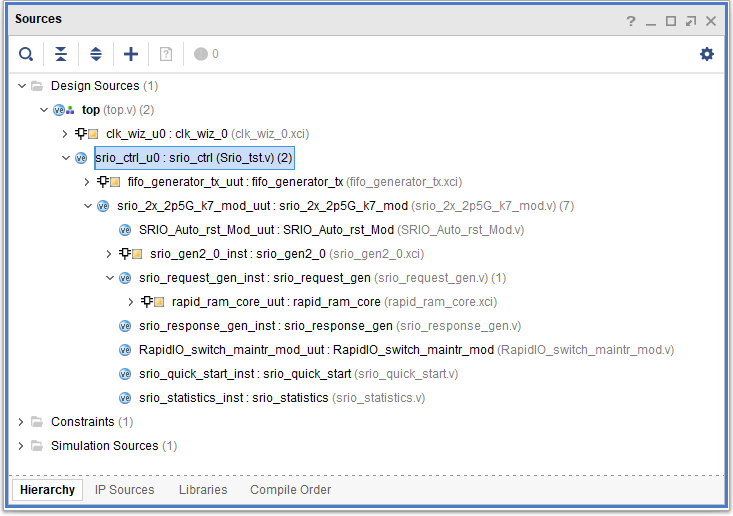

03工程源码结构

下图是SRIO工程源码结构:

其中,

- SRIO_Auto_rst_Mod:SRIO自动复位模块;

- srio_request_gen:SRIO请求事务生成模块;

- srio_response_gen:SRIO响应事务生成模块;

- RapidIO_switch_maintr_mod & srio_quick_start:SRIO维护事务生成模块。

04实现功能

该FPGA SRIO模块采用NWRITE类型事务往DSP目的地址传输数据,每包数据大小为256字节。数据写入完毕后,通过DOORBELL事务给DSP发送数据接收中断。另外FPGA端通过RapidIO IP核m_axis_treq接口接收来自DSP的数据。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1629文章

21748浏览量

603978 -

通信协议

+关注

关注

28文章

887浏览量

40324 -

sRIO

+关注

关注

1文章

31浏览量

21023 -

串行通信

+关注

关注

4文章

576浏览量

35429 -

Vivado

+关注

关注

19文章

812浏览量

66623

发布评论请先 登录

相关推荐

FPGA的SRIO接口使用应注意的事项

,并使用正确的连接线将它们连接起来。

按照规格书的要求进行连接,确保连接的稳固性和可靠性。

在FPGA和通信设备上配置SRIO接口的软件驱动程序和相关设置,确保两端的通信协议和参数设置一致

发表于 06-27 08:33

C6672与FPGA的SRIO通信问题

请教SRIO通信问题,6672和FPGA的SRIO通信,2个lane连接,现象如下:

(1)两端都配置成2x,3.125G,FPGA显示port initial成功,link ini

发表于 06-21 13:52

用SRIO实现DSP与FPGA通信

我在做fpga与dsp的SRIO通信,我用的是论坛上提供的SRIO test程序,目前dsp端能够实现端口0的外部回环测试。fpga端的协议

发表于 06-21 10:45

6678 SRIO链路信号完整性测试方法

; FPGA

1、STK中的external line loopback工作方式好像满足我的需求,但似乎前提是连接双方必须在SRIO协议基础上建立物理层的连接才可以进行测试。由于

发表于 06-21 06:25

srio协议将数据从我的模块发送到其他模块怎么实现?

嗨, 我想通过srio协议将数据从我的模块(fpga)发送到其他模块(tc6678texas处理器)。我想知道是否有任何中断来启动转移?感谢致敬M LOKESWARA REDDYBEL

发表于 04-30 09:31

基于SRIO协议的板级芯片互联技术

本文介绍了这种基于SRIO互联技术的高速实时数据处理硬件平台,并在该平台上研究了多DSP之间、DSP与FPGA之间的SRIO通信技术。

发表于 01-10 15:07

•3901次阅读

基于C66x+FPGA的SRIO开发视频教程

本文为您分享基于C66x+FPGA的SRIO开发视频教程,适用于创龙TMS320C6678、TMS320C665x、Kintex-7、Artix-7平台。

发表于 07-01 10:47

•1990次阅读

SRIO IP核的三层协议的作用?

数据从远程设备(假设为DSP的SRIO端)传输过来,FPGA端(假设我们这端为FPGA的SRIO端口)通过RX接收到串行数据,先到达物理层进行时钟恢复,串并转换,之后进行8b/10b解

在FPGA和DSP两种处理器之间实现SRIO协议的方法

摘要: 现代 信号 处理系统通常需要在不同处理器之间实现高速数据 通信 ,SRIO协议由于高效率、低延时的特性被广泛使用。本文研究了在 FPGA 和 DSP 两种处理器之间实现SRIO

srio交换芯片是什么?srio交换芯片的原理和作用

SRIO(Serial RapidIO)交换芯片是一种高性能的通信芯片,专门设计用于实现基于SRIO协议的数据交换和传输。SRIO是一种点对点串行通信

SRIO介绍及xilinx的vivado 2017.4中生成srio例程代码解释

介绍 本处将从SRIO的数据流,数据协议,常用FPGA支持模式,以及IP例程中的时钟大小计算等部分介绍SRIO的情况。 3.1 SRIO的数

基于FPGA的SRIO协议设计

基于FPGA的SRIO协议设计

评论