1 后摩尔时代,先进封装成为提升芯片性能重要解法

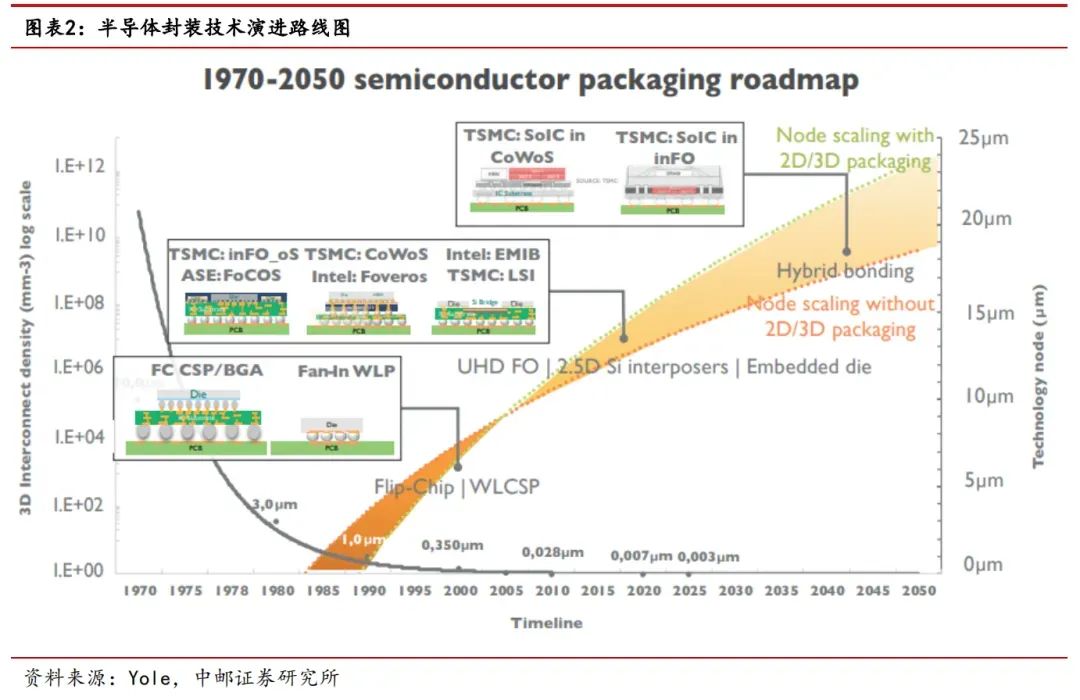

1.1 摩尔定律放缓,先进封装日益成为提升芯片性能重要手段随着摩尔定律放缓,芯片特征尺寸接近物理极限,先进封装成为提升芯片性能,延续摩尔定律的重要手段。先进封装是指处于前沿的封装形式和技术,通过优化连接、在同一个封装内集成不同材料、线宽的半导体集成电路和器件等方式,提升集成电路的连接密度和集成度。当前全球芯片制程工艺已进入3-5nm区间,接近物理极限,先进制程工艺芯片的设计难度、工艺复杂度和开发成本大幅增加,摩尔定律逐渐失效,半导体行业进入“后摩尔时代”。前道制程工艺发展受限,但随着AI等新兴应用场景快速发展,芯片性能要求日益提高,越来越多集成电路企业转向后道封装工艺寻求先进技术方案,以确保产品性能的持续提升。先进封装技术应运而生,在“后摩尔时代”逐步发展为推动芯片性能提升的主要研发方向。

先进封装有多种分类标准,是否有焊线或光刻工序是其中一种区分方式。传统封装不涉及光刻工序,切割后的晶圆通过焊线工艺实现芯片与引线框架的电性连接,从而完成芯片内外部的连通。先进封装主要利用光刻工序实现线路重排(RDL)、凸块制作(Bumping)及三维硅通孔(TSV)等工艺技术,涉及涂胶、曝光、显影、电镀、去胶、蚀刻等工序。

1.2 先进封装份额占比提升,2.5D/3D封装增速领先先进封装

1.2 先进封装份额占比提升,2.5D/3D封装增速领先先进封装

AI带动先进封装需求。TrendForce报告指出,聊天机器人等生成式AI应用爆发式增长,带动2023年AI服务器开发大幅扩张。这种对高端AI服务器的依赖,需要使用高端AI芯片,这不仅将拉动2023~2024年HBM的需求,而且预计还将在2024年带动先进封装产能增长30~40%。先进封装增速高于整体封装,2.5D/3D封装增速居先进封装之首。根据Yole,2021年,先进封装市场规模约375亿美元,占整体封装市场规模的44%,预计到2027年将提升至占比53%,约650亿美元,CAGR21-27为9.6%,高于整体封装市场规模CAGR21-27 6.3%。先进封装中的2.5D/3D封装多应用于(x)PU, ASIC, FPGA, 3D NAND, HBM, CIS等,受数据中心、高性能计算、自动驾驶等应用的驱动,2.5D/3D封装市场收入规模CAGR21-27高达14%,在先进封装多个细分领域中位列第一。

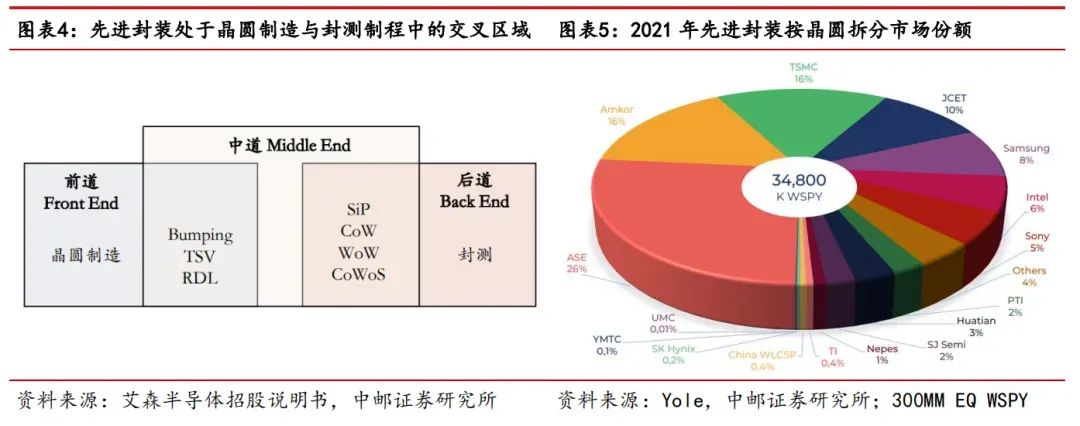

1.3 先进封装处于晶圆制造与封测的交叉区域先进封装处于晶圆制造与封测制程中的交叉区域,涉及IDM、晶圆代工、封测厂商。先进封装要求在晶圆划片前融入封装工艺步骤,具体包括应用晶圆研磨薄化、重布线(RDL)、凸块制作(Bumping)及硅通孔(TSV)等工艺技术,涉及与晶圆制造相似的光刻、显影、刻蚀、剥离等工序步骤,从而使得晶圆制造与封测前后道制程中出现中道交叉区域,如图表4所示。前后道大厂争先布局先进封装,竞争格局较为集中。后摩尔时代,先进制程成本快速提升,一些晶圆代工大厂发展重心正在从过去追求更先进纳米制程,转向封装技术的创新。诸如台积电、英特尔、三星、联电等芯片制造厂商纷纷跨足封装领域。先进封装竞争格局较为集中,全球主要的6家厂商,包括2家IDM厂商(英特尔、三星),一家代工厂商(台积电),以及全球排名前三的封测厂商(日月光、Amkor、JCET),共处理了超过80%的先进封装晶圆。

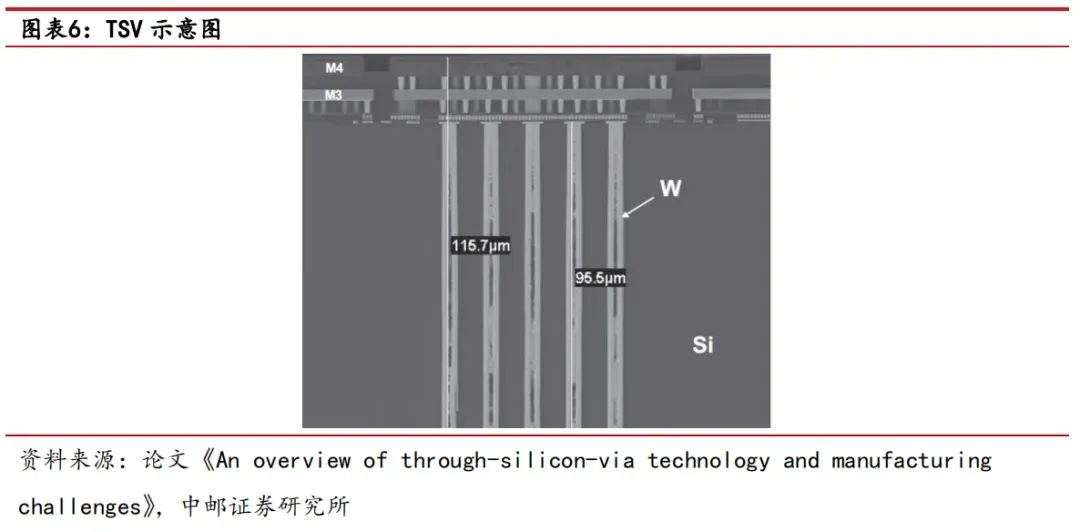

2 TSV:硅通孔,先进封装关键技术2.1 TSV:硅通孔技术,芯片垂直堆叠互连的关键技术TSV(Through Silicon Via),硅通孔技术,是通过硅通道垂直穿过组成堆栈的不同芯片或不同层实现不同功能芯片集成的先进封装技术。TSV主要通过铜等导电物质的填充完成硅通孔的垂直电气互连,减小信号延迟,降低电容、电感,实现芯片的低功耗、高速通信,增加带宽和实现器件集成的小型化需求。此前,芯片之间的大多数连接都是水平的,TSV的诞生让垂直堆叠多个芯片成为可能。Wire bonding(引线键合)和Flip-Chip(倒装焊)的Bumping(凸点)提供了芯片对外部的电互连,RDL(再布线)提供了芯片内部水平方向的电互连,TSV则提供了硅片内部垂直方向的电互连。

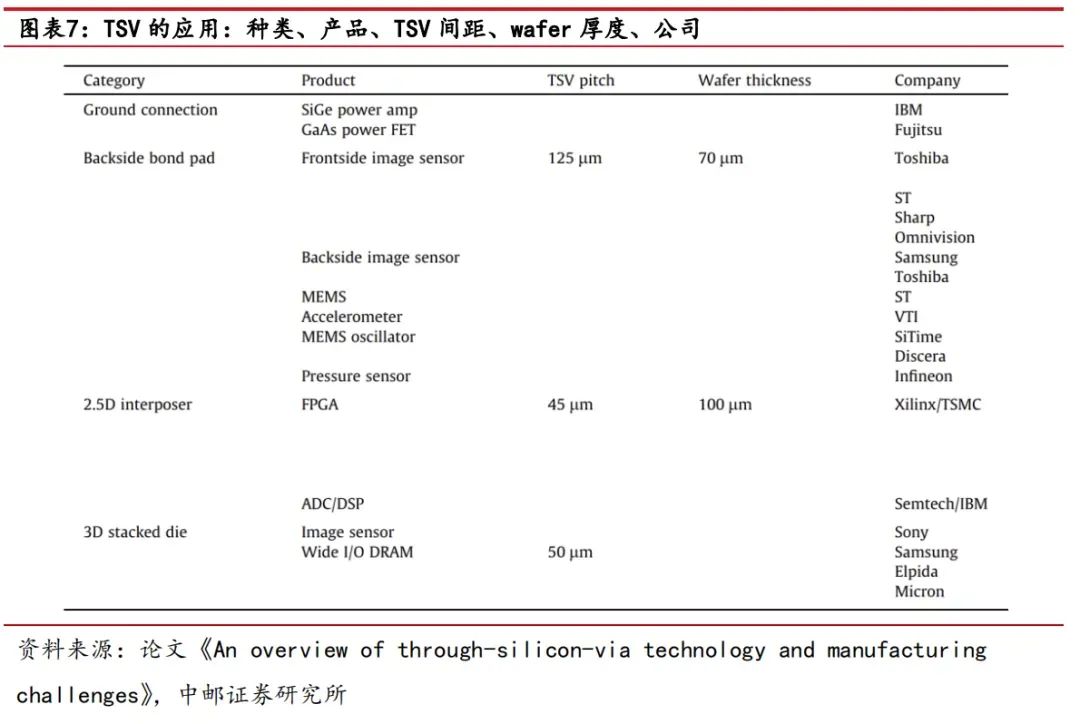

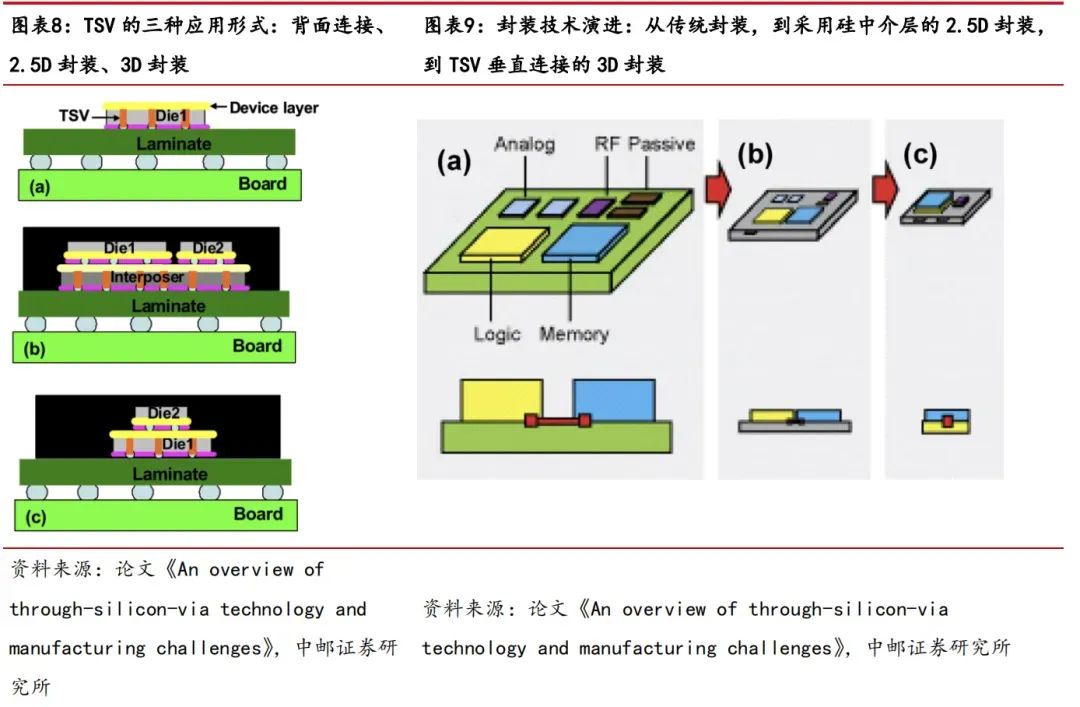

2.2 TSV三种主要应用方向:背面连接、2.5D封装、3D封装TSV有多种用途(如图表7),可大致分为3种(如图表8):(a) 垂直的背面连接,无芯片堆叠,如“简单的背面连接”。TSV位于有源晶粒(active die)中,用于连接至晶圆背面的焊盘(bond pad);(b) 2.5D封装。晶粒(die)连接至硅中介层(interposer),TSV在中介层中;(c) 3D封装。TSV位于有源晶粒中,用于实现芯片堆叠。

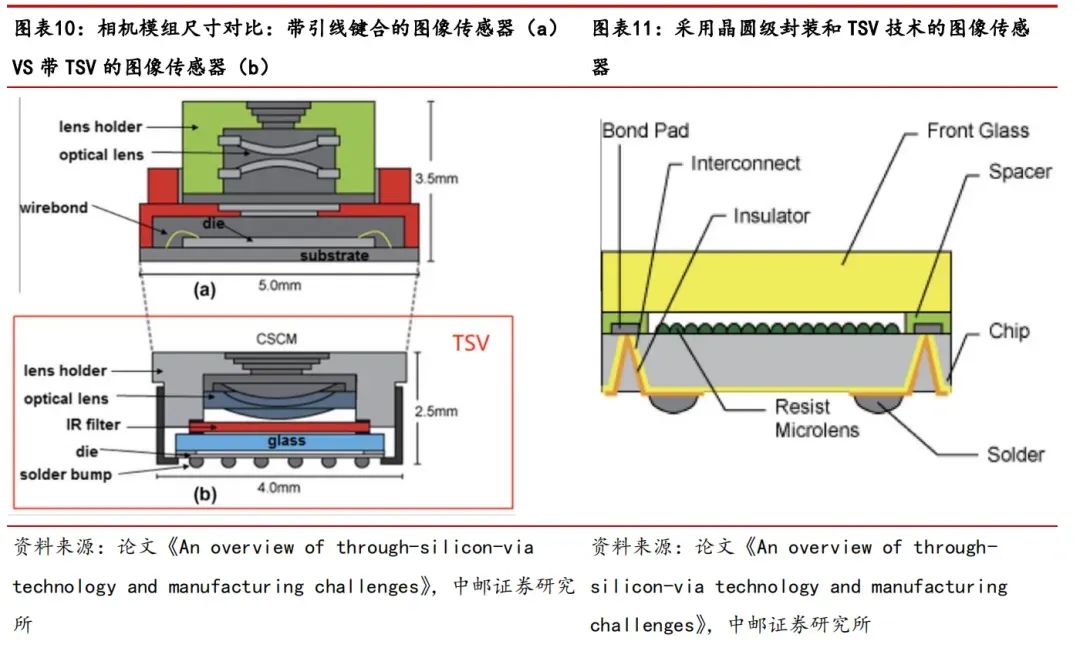

(a)TSV作为简单背面连接:用于CIS和锗化硅(SiGe)功率放大器TSV三种主要应用方式中,简单的背面连接结构是技术难度最低的,也是TSV技术首次大规模投入生产时的应用方向,如CMOS图像传感器(CIS)、SiGe功率放大器两个产品就应用了TSV技术。将TSV用于CMOS图像传感器有许多优点:1)使用TSV代替引线键合可以减小相机模组的尺寸(如图表10)。2)简化了图像传感器的晶圆级封装(WLP)(如图表11)。WLP工艺的第一步是将玻璃晶圆附着到图像传感器的正面,防止光刻胶(抗蚀剂)微透镜在组装过程中受到损坏和污染,然而安装好玻璃晶圆后会使从晶圆正面到焊盘的连接途径受阻,TSV通过简化晶圆级封装,对此问题提供了简易的解决方法。

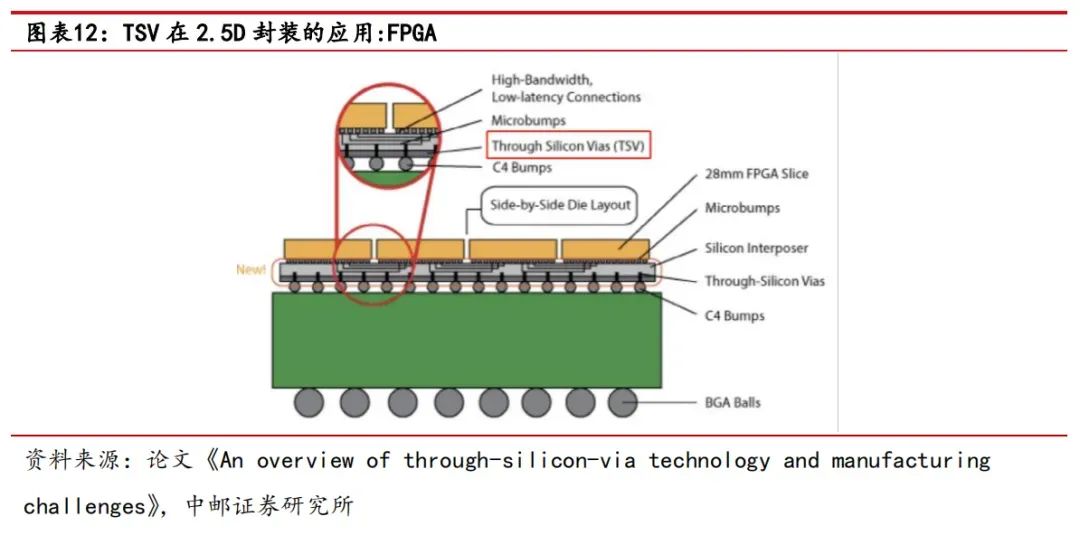

(b)TSV应用于2.5D封装:FPGA

与简单的背面连接相比,2.5D先进封装的硅中介层需要更小的TSV间距(≤50 μm),因此需要更先进的TSV工艺。现场可编程门阵列(Field Programmable Gate Array,FPGA)器件是最早使用硅中介层的产品之一:硅中介层可以使芯片间密切连接,整合后的结构看起来像单个大尺寸的FPGA芯片,解决了早期直接构建单个大尺寸FPGA芯片的技术难题。

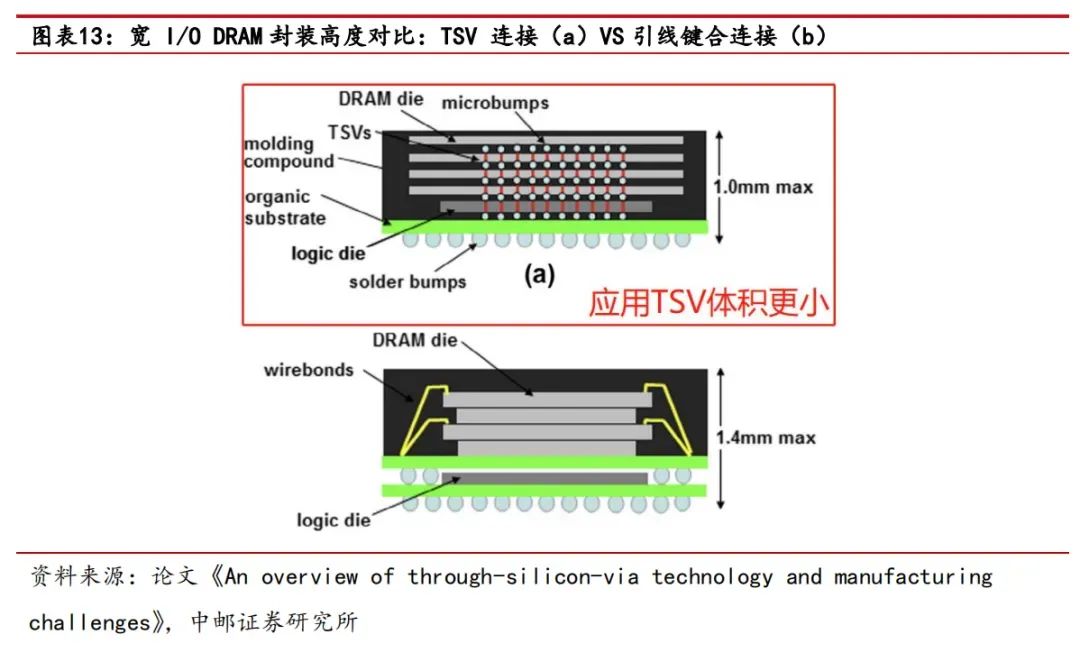

(c)TSV应用于3D封装:存储器堆叠存储器堆叠是首批应用3D堆叠TSV结构的产品之一,和2.5D封装中硅中介层对TSV间距的需求相似,但实际应用中难度更高,例如宽I/O DRAM设备。使用宽 I/O DRAM 和芯片堆叠的优势包括封装高度降低40%,功耗降低50%,带宽增加6倍。

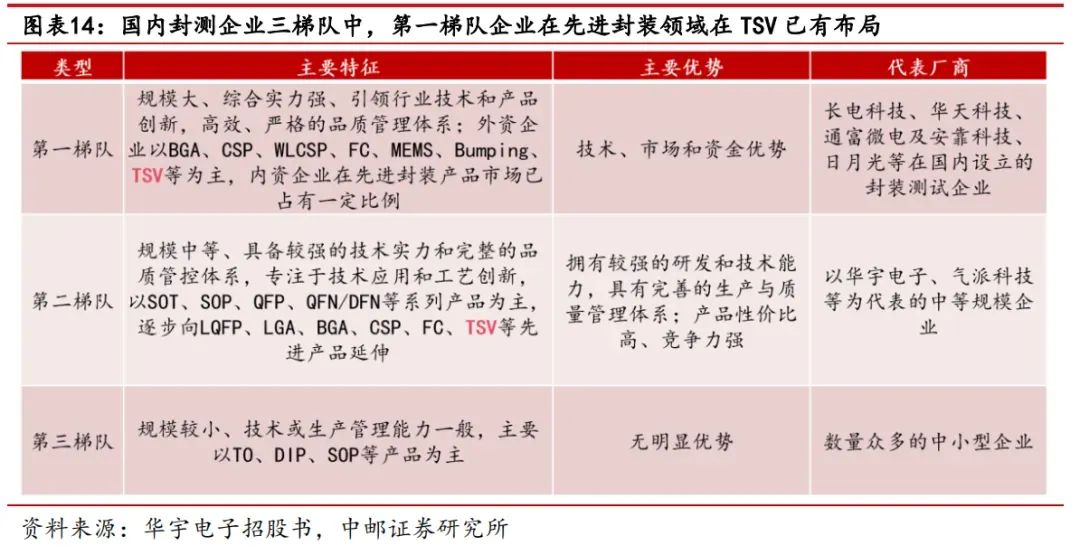

2.3 国内封测厂TSV布局情况:多家头部厂商已有布局内资封测厂商向TSV等先进封装领域突破。全球半导体产业经历二次产业转移,目前处于第三次产业转移的进程之中,作为半导体领域壁垒相对较低的领域,封测产业目前主要转移至亚洲区域,主要包括中国大陆、中国台湾、东南亚等。封测是中国大陆集成电路发展最为完善的板块,技术能力与国际先进水平比较接近,我国封测市场已形成内资企业为主的竞争格局。中国大陆封测市场目前主要以传统封装业务为主,经过多年的技术创新和市场积累,内资企业产品已由DIP、SOP、SOT、QFP等产品向QFN/DFN、BGA、CSP、FC、TSV、LGA、WLP等技术更先进的产品发展,并且在WLCSP、FC、BGA和TSV等技术上取得较为明显的突破,产量与规模不断提升,逐步缩小与外资厂商之间的技术差距,极大地带动我国封装测试行业的发展。 我国头部封测企业,如长电科技、通富微电、华天科技、晶方科技已有采用TSV技术封装的产品批量出货。2.5D/3D封装所需的晶圆内部的加工如TSV加工,硅转接板加工等工序属于晶圆厂擅长制程,而晶圆,裸芯片(Die)之间的高密度互联和堆叠,以及和基板,接点的互联技术属于芯片后道成品制造环节的优势。应用于CoWoS等2.5D/3D先进封装中的TSV技术对深宽比等有更高要求,需要用到诸多前道设备,仍多由晶圆厂来完成。国内封测厂则在先进封装平台、CIS封装等领域对TSV技术有所布局。长电科技的XDFOI技术平台有TSV less和TSV方案。通富微电2021年在高性能计算领域建成了2.5D/3D封装平台(VISionS)及超大尺寸FCBGA研发平台,并完成高层数再布线技术开发,可为客户提供晶圆级和基板级Chiplet封测解决方案;在存储器领域,多层堆叠NAND Flash及LPDDR封装实现稳定量产,并在国内首家完成基于TSV技术的3DS DRAM封装开发。华天科技工业级12吋TSV-CIS产品已实现量产。晶方科技应用晶圆级硅通孔(TSV)封装技术,聚焦以影像传感芯片为代表的智能传感器市场,封装的产品主要包括CIS芯片、TOF芯片、生物身份识别芯片、MEMS芯片等,应用于智能手机、安防监控数码、汽车电子等市场领域。

我国头部封测企业,如长电科技、通富微电、华天科技、晶方科技已有采用TSV技术封装的产品批量出货。2.5D/3D封装所需的晶圆内部的加工如TSV加工,硅转接板加工等工序属于晶圆厂擅长制程,而晶圆,裸芯片(Die)之间的高密度互联和堆叠,以及和基板,接点的互联技术属于芯片后道成品制造环节的优势。应用于CoWoS等2.5D/3D先进封装中的TSV技术对深宽比等有更高要求,需要用到诸多前道设备,仍多由晶圆厂来完成。国内封测厂则在先进封装平台、CIS封装等领域对TSV技术有所布局。长电科技的XDFOI技术平台有TSV less和TSV方案。通富微电2021年在高性能计算领域建成了2.5D/3D封装平台(VISionS)及超大尺寸FCBGA研发平台,并完成高层数再布线技术开发,可为客户提供晶圆级和基板级Chiplet封测解决方案;在存储器领域,多层堆叠NAND Flash及LPDDR封装实现稳定量产,并在国内首家完成基于TSV技术的3DS DRAM封装开发。华天科技工业级12吋TSV-CIS产品已实现量产。晶方科技应用晶圆级硅通孔(TSV)封装技术,聚焦以影像传感芯片为代表的智能传感器市场,封装的产品主要包括CIS芯片、TOF芯片、生物身份识别芯片、MEMS芯片等,应用于智能手机、安防监控数码、汽车电子等市场领域。 3TSV制造流程及所需设备

3TSV制造流程及所需设备

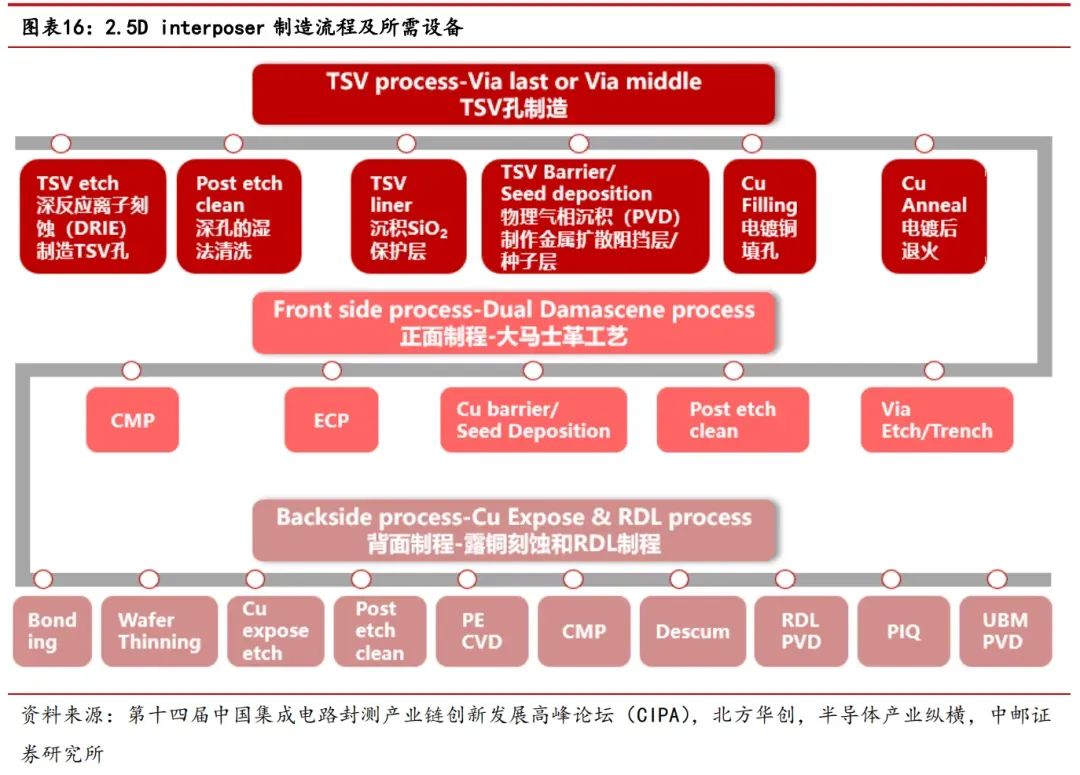

3.1 TSV制造流程以2.5D interposer为例,其制造流程可以分为三大部分:TSV process-Via last or Via middle(TSV孔的制造)、Front side process-Dual Damascene process(正面制程-大马士革工艺)以及Backside process-Cu Expose & RDL process(背面制程-露铜刻蚀和RDL制程)。每个部分具体环节对应不同设备及不同指标。TSV process:

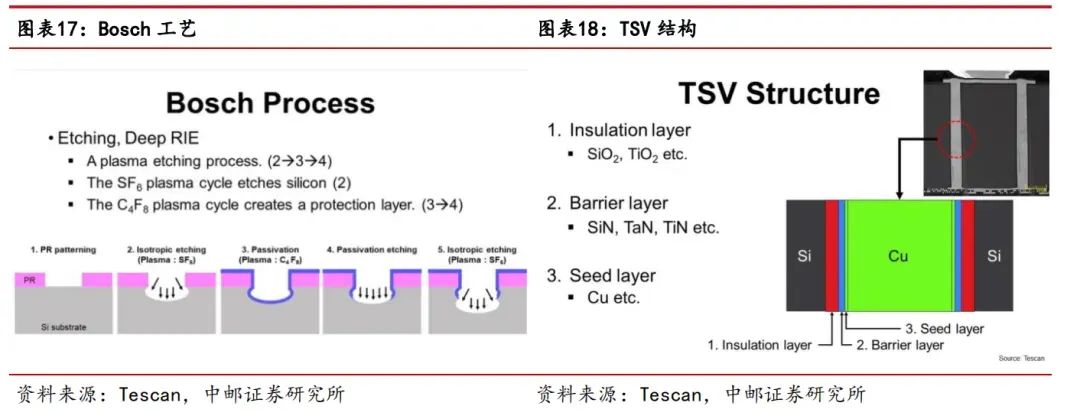

1)TSV etch:深反应离子刻蚀(DRIE)制作TSV孔,可用技术包括Non-Bosch Process与Bosch Process,其中Non-Bosch很难实现更高深宽比的刻蚀且效率有限;而Bosch工艺由于采用一步刻蚀一步沉积的方式,可以实现更高深宽比的刻蚀,另外其速率更快,可满足业界对成本与效率的要求。因此该步骤目前首选技术是基于Bosch工艺的干法刻蚀,使用到感应耦合高密度等离子体干法刻蚀机(ICP)。

2)Post etch clean:使用湿法方式进行深孔的清洗,需用到清洗设备。

3)TSV liner:沉积二氧化硅保护层liner,可用等离子增强化学气相沉积(PECVD)制作介电层;另外由于TSV的深宽比更高,亦用SACVD+PECVD的方式沉积,但是这种沉积方式要求深宽比要小于10:1并且开口需要大于10微米;北方华创用PEALD的方式。

4)TSV Barrier/Seed deposition:物理气相沉积(PVD)制作金属扩散阻挡层(业界一般使用Ti/TiN或者Ta/TaN,要求连续,需要满足最薄厚度的要求;同时要求有优良的粘附性)/种子层(业界一般使用Cu,要求连续,需要满足最薄厚度的要求;同时顶部不能有over hang),防止金属扩散到硅中或者金属扩散到氧化物中。

5)Cu Filling:用铜/钨电镀填孔,要求不留缝隙,同时尽量减少电镀过程中的应力;使用ECP。

6)Cu Anneal:电镀后的退火,因为铜在室温下有自退火效应,若不做退火,则给后道的CMP带来很大的不稳定性,做完退火后铜的晶粒分布更加均匀、晶界数量减少,增加铜的电迁移的可靠性,电阻率可以降低20%;业界用立式炉。Front side process-Dual Damascene process包括Via Etch/Trench(Etch Via/Trench的刻蚀)、Post etch clean(刻蚀后的清洗)、Cu barrier/Seed Deposition(阻挡层/种子层的沉积)、ECP(电镀)以及CMP(化学机械抛光去除多余的金属)。Backside process-Cu Expose & RDL process包括Bonding(临时键合)、Wafer Thinning(减薄)、Cu expose etch(用干法刻蚀的方式把TSV的铜柱露出来(BFR、BVR工艺))、Post etch clean(湿法清洗)、PECVD(PECVD做钝化)、CMP SiO2(磨掉铜柱上面的氮化硅,为RDL做准备)以及RDL制程(Descum、RDL PVD、PIQ、UBM PVD)。 3.2 TSV关键工艺设备及特点TSV生产流程涉及到深孔刻蚀、PVD、CVD、铜填充、微凸点及电镀、清洗、减薄、键合等二十余种设备,其中深孔刻蚀、气相沉积、铜填充、清洗、CMP去除多余的金属、晶圆减薄、晶圆键合等工序涉及的设备最为关键。1)深孔刻蚀设备深孔刻蚀是TSV的关键工艺,目前首选技术是基于Bosch工艺的干法刻蚀。深反应等离子刻蚀设备是感应耦合高密度等离子体干法刻蚀机(Inductively Coupled Plasma Etcher),采用半导体刻蚀机的成熟技术,独特设计的双等离子体源实现了对腔室内等离子体密度的均匀控制,满足硅高深宽比刻蚀工艺的要求。具有稳定可靠的工艺性能、宽阔的工艺窗口和良好的工艺兼容性,用于晶片的高深宽比刻蚀。

3.2 TSV关键工艺设备及特点TSV生产流程涉及到深孔刻蚀、PVD、CVD、铜填充、微凸点及电镀、清洗、减薄、键合等二十余种设备,其中深孔刻蚀、气相沉积、铜填充、清洗、CMP去除多余的金属、晶圆减薄、晶圆键合等工序涉及的设备最为关键。1)深孔刻蚀设备深孔刻蚀是TSV的关键工艺,目前首选技术是基于Bosch工艺的干法刻蚀。深反应等离子刻蚀设备是感应耦合高密度等离子体干法刻蚀机(Inductively Coupled Plasma Etcher),采用半导体刻蚀机的成熟技术,独特设计的双等离子体源实现了对腔室内等离子体密度的均匀控制,满足硅高深宽比刻蚀工艺的要求。具有稳定可靠的工艺性能、宽阔的工艺窗口和良好的工艺兼容性,用于晶片的高深宽比刻蚀。 2)气相沉积设备气相沉积设备主要用于薄膜电路表面的高低频低应力氧化硅等薄膜淀积。设备具有低温TEOS工艺沉积氧化硅薄膜,应力易调控,适用于薄膜电路制造中保护膜层的沉积。设备应具有预真空室、基片传送模块以及工艺模块等,传片及工艺过程自动化。绝缘层做好后,通过物理气相沉积法(PVD)沉积金属扩散阻挡层和种子层,为后续的铜填充做好准备。后续的电镀铜填充要求TSV侧壁和底部具有连续的阻挡层和种子层。种子层的连续性和均匀性被认为是TSV铜填充最重要的影响因素。根据硅通孔的形状、深宽比及沉积方法不同,种子层的特点也各有不同,种子层沉积的厚度、均匀性和粘合强度是极为重要的指标。

2)气相沉积设备气相沉积设备主要用于薄膜电路表面的高低频低应力氧化硅等薄膜淀积。设备具有低温TEOS工艺沉积氧化硅薄膜,应力易调控,适用于薄膜电路制造中保护膜层的沉积。设备应具有预真空室、基片传送模块以及工艺模块等,传片及工艺过程自动化。绝缘层做好后,通过物理气相沉积法(PVD)沉积金属扩散阻挡层和种子层,为后续的铜填充做好准备。后续的电镀铜填充要求TSV侧壁和底部具有连续的阻挡层和种子层。种子层的连续性和均匀性被认为是TSV铜填充最重要的影响因素。根据硅通孔的形状、深宽比及沉积方法不同,种子层的特点也各有不同,种子层沉积的厚度、均匀性和粘合强度是极为重要的指标。

3)铜填充设备深孔金属化电镀设备用于新一代高频组件高深宽比通孔填孔电镀铜工艺,解决高深宽比微孔内的金属化问题,提高互联孔的可靠性。TSV填孔镀铜工序是整个TSV工艺里最核心、难度最大的工艺,对设备的要求比较高,成熟的用于TSV填孔镀铜的设备价格昂贵。

4)减薄抛光设备一旦完成了铜填充,则需要对晶圆进行减薄抛光。TSV要求晶圆减薄至50μm甚至更薄,要使硅孔底部的铜暴露出来,为下一步的互连做准备。目前晶圆减薄可以通过机械研磨、化学机械抛光、湿法及干法化学处理等不同的加工工序来实现,但晶圆很难容忍减薄过程中的磨削对晶圆的损伤及内在应力,其刚性也难以使晶圆保持原有的平整状态,同时后续工艺的晶圆传递、搬送也遇到了很大的问题。目前业界的多采用一体机的思路,将晶圆的磨削、抛光、贴片等工序集合在一台设备内。

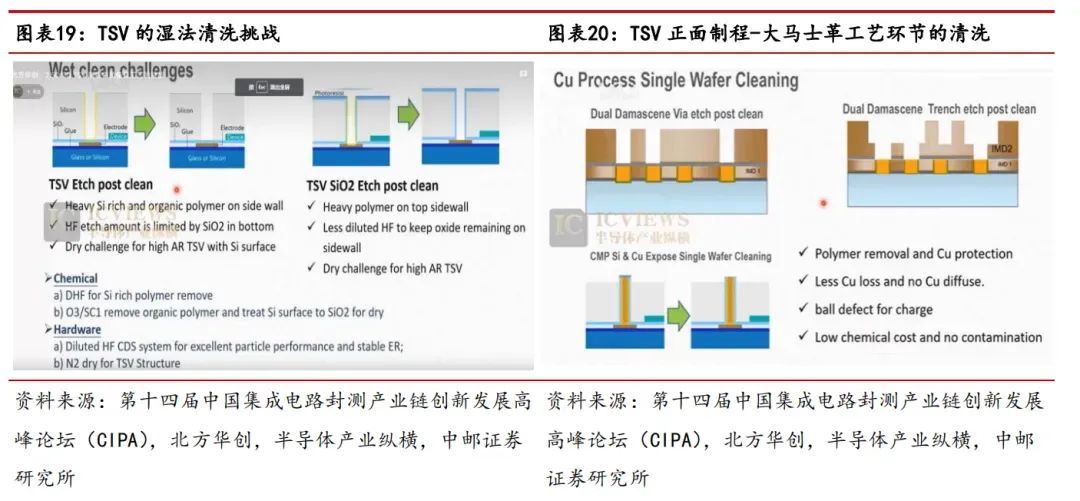

5)清洗设备TSV的湿法清洗不同于晶圆级封装等先进封装,其中有几个关键工序需用到清洗:①TSV刻蚀后清洗:有比较重的硅的残留、侧壁的polymer比较重,清洗的时候不能破坏底部的二氧化硅;②TSV长完liner后要把底部的二氧化硅打开后清洗,清洗底部的同时不能破坏侧壁长好的liner的二氧化硅;③大马士革正面制程刻蚀后的清洗包括Via刻蚀后和Trench刻蚀后;④露铜过程前后的清洗。 6)检测量测设备:在后段封装工艺中,芯片倒装(Flip-chip)、圆片级封装(Wafer-level Packaging)和硅通孔(Through-silicon Via,TSV)等先进工艺要求对凸点(Bump)、通孔(TSV)、铜柱(Copper pillar)等的缺损/异物残留及其形状、间距、高度的一致性,以及重布线层(Re-distribution layer,RDL)进行无接触定量检查和测量,以保证集成电路芯片生产线快速进入量产阶段并获取稳定的高成品率和高经济效益。

6)检测量测设备:在后段封装工艺中,芯片倒装(Flip-chip)、圆片级封装(Wafer-level Packaging)和硅通孔(Through-silicon Via,TSV)等先进工艺要求对凸点(Bump)、通孔(TSV)、铜柱(Copper pillar)等的缺损/异物残留及其形状、间距、高度的一致性,以及重布线层(Re-distribution layer,RDL)进行无接触定量检查和测量,以保证集成电路芯片生产线快速进入量产阶段并获取稳定的高成品率和高经济效益。

4 风险提示下游需求不及预期;行业景气度复苏不及预期;公司技术与产品迭代进展不及预期等。

-

芯片

+关注

关注

455文章

50851浏览量

423863 -

半导体

+关注

关注

334文章

27389浏览量

218993 -

封装

+关注

关注

126文章

7916浏览量

142995 -

后摩尔时代

+关注

关注

0文章

12浏览量

9182 -

TSV

+关注

关注

4文章

112浏览量

81483

发布评论请先 登录

相关推荐

TSV三维堆叠芯片的可靠性问题

先进封装中的TSV/硅通孔技术介绍

TSV 制程关键工艺设备技术及发展

大族封测创业板IPO终止

基于两步刻蚀工艺的锥形TSV制备方法

TSV与异构集成技术的前沿进展与趋势展望

半导体封测厂日月光投控宣布收购英飞凌2座封测厂!

大族封测IPO终止

大族封测创业板IPO最新进展

一文详解硅通孔技术(TSV)

封测:TSV研究框架

封测:TSV研究框架

评论