正文

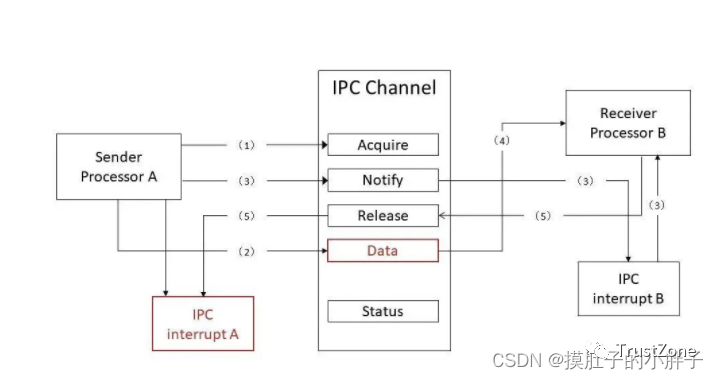

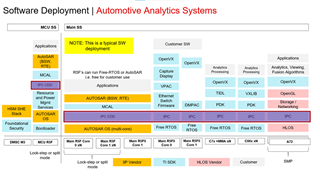

目前很多芯片都会有几个core核,有的是Cortex M0+、M4、M7、A53、A73等等,有的有着2核、3核、4核甚至6核8核,不同的核的主频支持度不一样,适用的具体应用场景也不同,因此需要IPC(Inter-processor communication)来核间通信,进行数据的交互。

核间通信(IPC)的主要目标是:充分利用硬件提供的机制,实现高效的CORE间通信;给需要CORE间通信的应用程序提供简洁高效的编程接口。

根据所使用的硬件特性,核间通信的实现机制有:

• ·Mailbox中断

• ·基于共享内存的消息队列

在这里插入图片描述

在这里插入图片描述

在这里插入图片描述

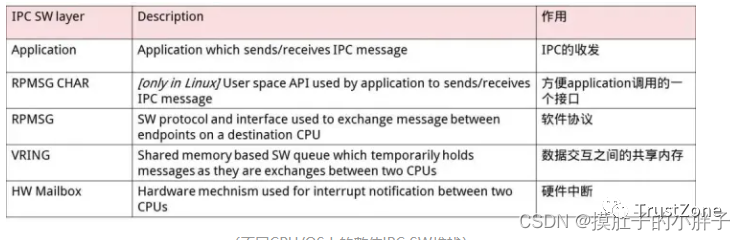

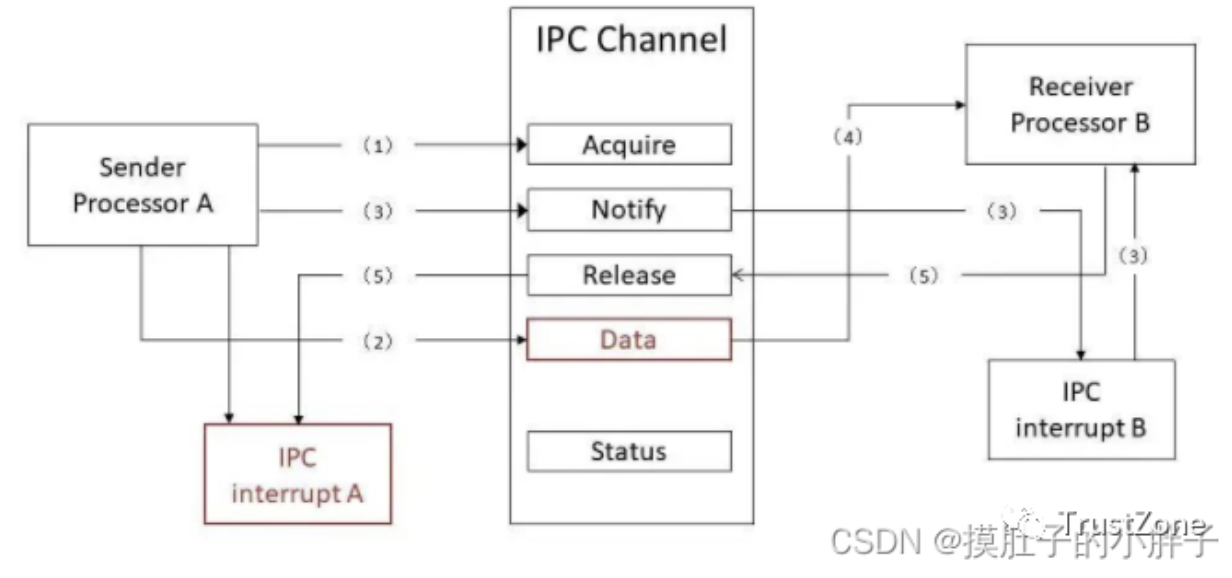

封装-VRING-解析的过程:

1、应用程序向给定目的地(CPU、端点)发送消息

2、消息首先从应用程序复制到两个CPU之间使用的VRING。此后,IPC 驱动程序在硬件邮箱中发布 VRING ID。

3、这会触发目标 CPU 上的中断。在目标 CPU 的 ISR 中,它提取 VRING ID,然后根据 VRING ID 检查该 VRING 中的所有消息。

4、如果收到消息,它从VRING中提取消息并将其放入目标RPMSG端点队列中。然后触发在此 RPMSG 端点上阻止的应用程序。

5、应用程序处理接收到的消息,并使用相同的RPMSG 和VRING 机制在相反方向回复发送方CPU。

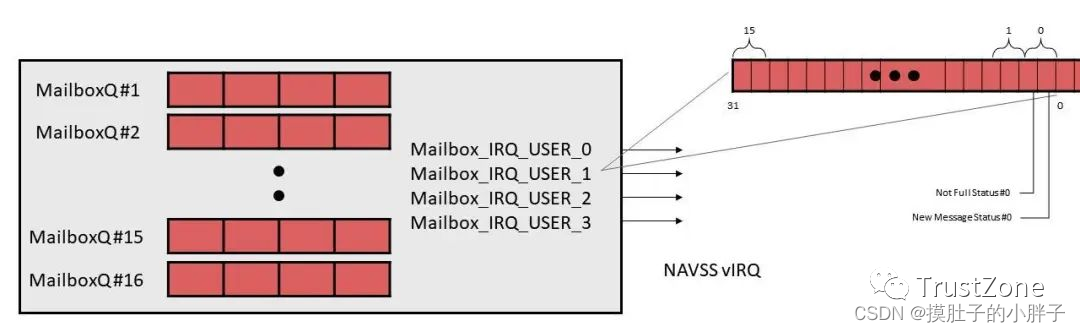

Hardware Mailbox

硬件邮箱主要用于提供具有小的 32 位有效负载的中断事件通知。

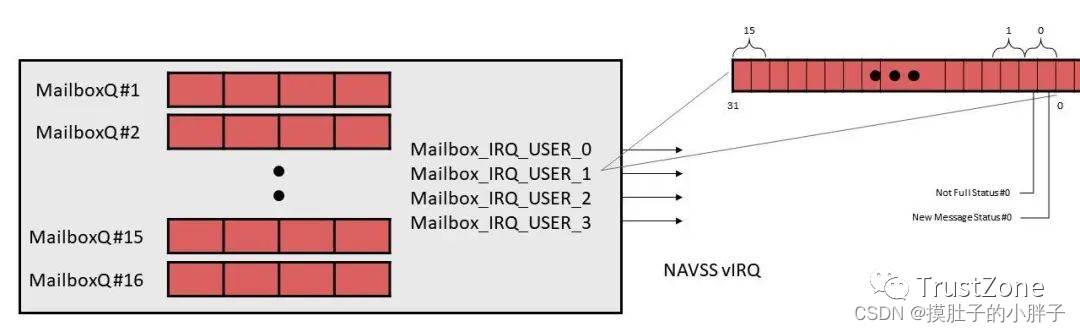

VRING 使用硬件邮箱在目标 CPU 上触发中断。每个邮箱包含 16 个单向 HW 队列,最多可连接 4 个通信用户或 CPU。

J721E SoC 有 12 个硬件邮箱实例。即 12x 16 个硬件邮箱队列。

(硬件邮箱的逻辑框图)

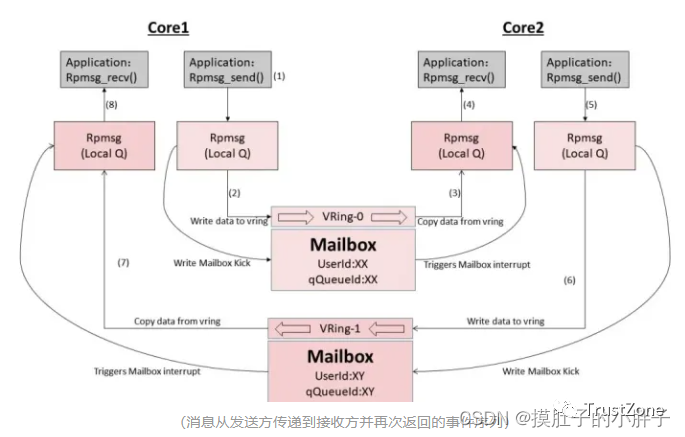

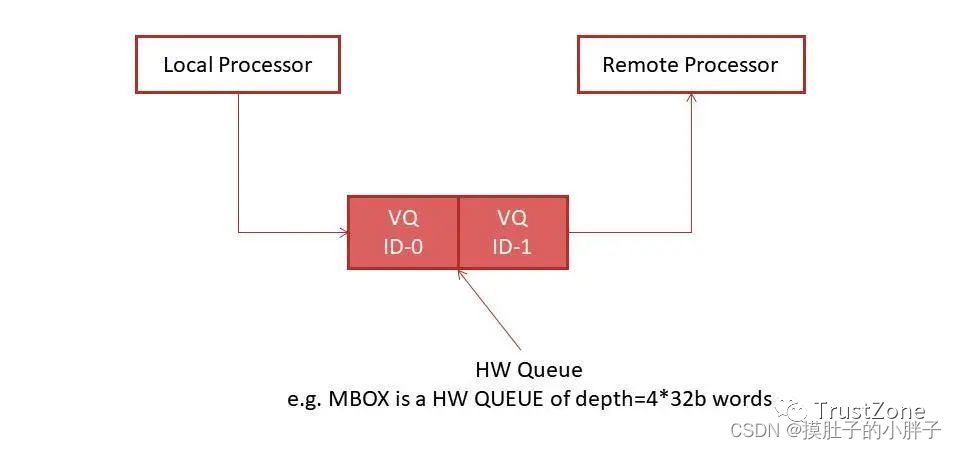

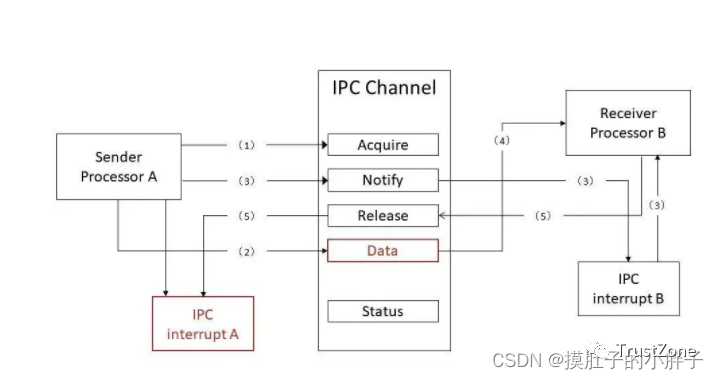

Mailbox and VRING

邮箱本质上充当一个非常小的硬件队列,其中包含 VRING ID。

VRING 是共享内存中的 SW 队列,保存两个 CPU 之间传递的实际消息。当收到中断时,邮箱消息会告知从哪个 VRING 出列消息。

VRING ID=0 tells to look at the VRING from sender to receiver

VRING ID=1 tells to look at the VRING from receiver to sender

在这里插入图片描述

散文

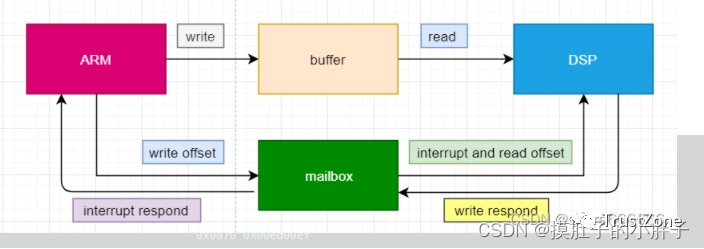

mailbox其实是多核处理器soc上,核与核之间互相发中断的机制,由于核与核之间可能存在不同的业务,故硬件上设计分配一两个中断已经无法满足业务的需求,软件拓展起来很困难,所以mailbox可以理解为软件可自由定义的中断模块。

用于在片上处理器之间通信的一种mailbox队列中断机制,mailbox队列中断机制允许软件通过一组寄存器和关联的中断设置和得到信息在二个处理之间建立通信渠道。

核间通信的主要目标是:充分利用硬件提供的机制,实现高效的CORE间通信;给需要CORE间通信的应用程序提供简洁高效的编程接口。

根据所使用的硬件特性,核间通信可能的实现机制有:

1. Mailbox中断;

2. 基于共享内存的消息队列;

3. POW + Group;

4. FAU;支持原子的读,写,fetch and add操作。

每个core有一个相应的32bit的mailbox寄存器,每一位可被单独地设置或清零。这对于core间的中断非常有用,任意core可直接通过其它core 的mailbox对其它core发出中断。当mailbox被置位时,相应core的中断寄存器也同时被置位,软件可实现其中断处理。

Bootloader支持Octeon_phy_mem_named_block_alloc( ),分配以名字命名的物理内存空间,不管是Service Executive应用程序还是linux kernel都可以通过Octeon_phy_mem_named_block_find( )找到这部分内存,实现core之间的共享数据。

Linux kernel也提供了共享内存的机制。主要有mmap(),系统V,Posix共享内存模型等。系统调用mmap()通过映射一个普通文件实现共享内存。普通文件被映射到进程地址空间后,进程可以向访问普通内存一样对文件进行访问。系统V共享内存指的是把所有共享数据放在共享内存区域(IPC shared memory region),任何想要访问该数据的进程都必须在本进程的地址空间新增一块内存区域,用来映射存放共享数据的物理内存页面。posix共享内存区首先指定一个名字参数调用shm_open,以创建一个新的共享内存区对象或打开一个以存在的共享内存区对象。然后调用mmap把这个共享内存区映射到调用进程的地址空间。传递给shm_open的名字参数随后由希望共享该内存区的任何其他进程使用。

核间通信方案

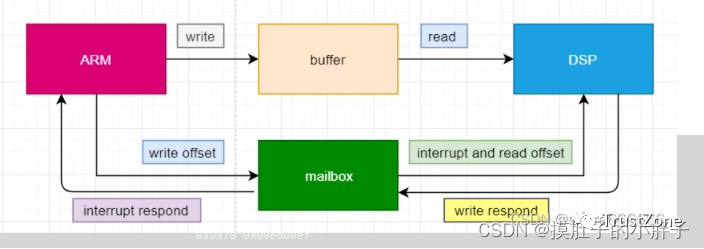

如下图所示ARM核和DSP核进行mailbox通信,ARM要发送数据给DSP:

• 1 ARM核先往某个指定的共享内存空间buffer写入数据,然后MAILBOX触发中断和写入关于共享内存空间的地址信息给DSP。

• 2 DSP通过得到mailbox中断的信息读取共享内存空间ARM核发送的buffer数据。

• 3 DSP核读取完数据后将触发mailbox中断给ARM作为回应,告诉ARM核你发送的数据我已经接受完成了。a

在这里插入图片描述

审核编辑:汤梓红

-

芯片

+关注

关注

458文章

51508浏览量

429356 -

cpu

+关注

关注

68文章

10940浏览量

213730 -

中断

+关注

关注

5文章

900浏览量

41934 -

Cortex

+关注

关注

2文章

203浏览量

46683 -

IPC

+关注

关注

3文章

353浏览量

52230

原文标题:参考资料:

文章出处:【微信号:谈思实验室,微信公众号:谈思实验室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SoC的核间通信机制—mailbox介绍

lpc54114双核通信--中断

关于AM5728核间通信方式(共享内存)问题

关于C6678核间IPC通信的问题

基于IP核的SoC接口技术

RT-thread内核之进程间通信设计实现

基于raspi 3b上的SMP设计实现

一种基于Mailbox核间机制的多核处理系统

SoC的核间通信机制硬件邮箱

SoC核间通信的实现机制之mailbox中断

SoC核间通信的实现机制之mailbox中断

评论