引言

在超大规模集成电路(VLSI)设计中,系统芯片(SoC)已经成为了主流趋势。SoC是将多种功能模块集成在一个芯片中,实现系统的集成化和高性能化。

在这个复杂的系统中,中断机制是不可或缺的一部分。中断机制可以协调各个功能模块之间的运行顺序,保证系统的稳定性和高效性。本文将探讨为什么在SoC设计中需要中断机制。

中断概念

中断是一种处理器通过暂停正在执行的程序,并跳转到特定程序段以处理中断事件的机制。中断机制包括中断源、中断请求和中断响应。中断源是指产生中断的设备或程序,中断请求是中断源向处理器发出的中断申请,中断响应是处理器对中断请求的响应。

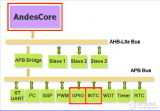

soc芯片设计中的中断机制

在SoC设计中,各个功能模块之间的通信和协调需要中断机制来实现。中断机制可以保证系统的实时性和响应性,同时也可以有效地避免功能模块之间的冲突。以下是SoC设计中中断机制的几个关键方面:

中断管理器:中断管理器是一种专门用于管理中断的硬件或软件模块。它负责接收和处理中断请求,并通知处理器处理中断事件。

中断优先级:多个中断源可能同时向处理器发出中断请求。为了确定处理器的响应顺序,中断机制需要设定不同的中断优先级。高优先级的中断请求会优先于低优先级的中断请求得到响应。

中断映射:在SoC设计中,不同的功能模块需要映射到不同的中断源上。中断映射保证了每个功能模块能够正确地响应对应的中断事件。

中断对系统性能的影响

中断机制对SoC系统的性能具有重要影响。合理的设计和使用中断机制可以提高系统的稳定性和效率。以下是中断机制对系统性能的几个影响方面:

系统稳定性:合理的设计中断机制可以减少系统故障和崩溃的可能性,提高系统的稳定性和可靠性。

系统效率:中断机制可以有效地避免功能模块之间的冲突,提高系统并行处理的效率。同时,通过设定不同的中断优先级,可以确保系统的关键部分得到优先处理,提高系统的实时性。

系统扩展性:合理设计的中断机制应具有良好的扩展性,以适应未来新增的功能模块和外部设备的接入。

结论

在SoC设计中,中断机制是实现系统协调和通信的关键部分。通过中断机制,系统可以有效地处理各种中断事件,确保系统的实时性、稳定性和高效性。因此,深入了解和掌握中断机制对于优化SoC设计具有重要意义。

审核编辑:刘清

-

处理器

+关注

关注

68文章

19259浏览量

229655 -

芯片设计

+关注

关注

15文章

1015浏览量

54879 -

SoC芯片

+关注

关注

1文章

610浏览量

34905 -

中断优先级

+关注

关注

0文章

22浏览量

9368

原文标题:为什么soc芯片设计中需要中断机制

文章出处:【微信号:快乐的芯片工程师,微信公众号:快乐的芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

以x86 CPU架构理解Linux中断机制

有什么方法让Linux在一块新的ARM SoC上运行呢

是否有一种机制可以在中断禁用后访问变量a反映在CPU的结构中呢?

SOC测试访问机制

ARM向量中断机制在uClinux下的设计

SoC设计的中断处理模式指南

在Zynq SoC上使用编写中断程序示范及实例

简述PCI总线的中断机制

STM32的中断机制 stm32中断方式有几种

【LiteOS】08-开发内核-中断机制

为什么在SoC设计中需要中断机制呢?

为什么在SoC设计中需要中断机制呢?

评论