01概述

本文总结一下前段时间完成的FPGA以太网通信功能。该方案参考了MILIANKE的设计,但在其基础上简化了某些不必要的步骤以及解决了一些由于忽视细节导致的棘手的问题。

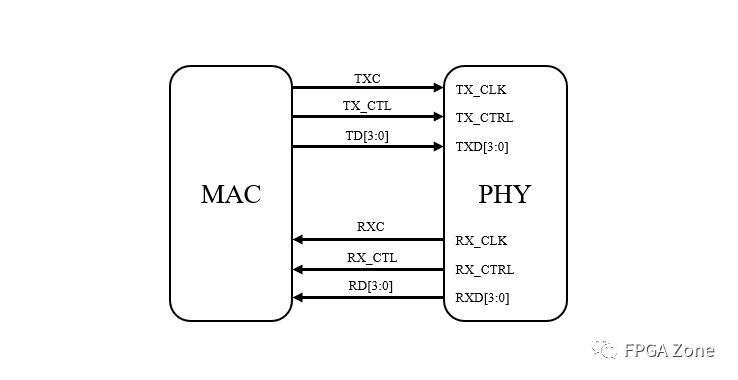

02RGMII接口

本设计采用RGMII接口的88E1512芯片。RGMII接口的主要优势在于,它可以同时适用于1000M、100M、10M三种速率,并且接口占用引脚数较少。

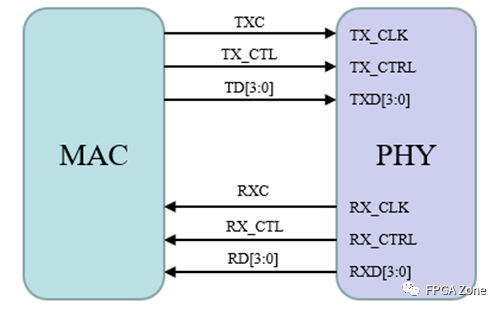

RGMII 使用 4bit 数据接口采用上下沿 DDR(Double Data Rate)的方式在一个时钟周期内传输 8bit 数据信号,即上升沿发送或者接收数据的低4位[3:0],下降沿发送或者接收数据的高4位[7:4]。同理,使用 1bit 控制接口采用 DDR 的方式在一个时钟周期内传输 2bit 控制信号。

- 发送端:tx_clk,tx_d[3:0],tx_ctrl;

- 接收端:rx_clk,rx_d[3:0],rx_ctrl;

图1 RGMII接口

- 三种速率模式

MII接口适用于1000M、100M、10M三种传输速率。

当工作于1000M 时,时钟信号 TXC 和 RXC 均为 125MHz,4bit数据信号上下沿值均有效,控制信号上下沿值也均有效。

当工作于 100M时,时钟信号 TXC 和 RXC均为25MHz,4bit数据信号只有上升沿值[3:0]有效,相当于此时数据信号切换为单沿SDR(Single Data Rata)4位输模式。控制信号仍为上下沿有效。

当工作于10M时,时钟信号TXC和RXC均为2.5MHz,数据信号和控制信号的使用和100M速率时完全相同。

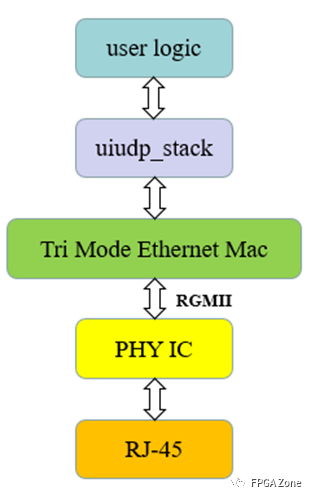

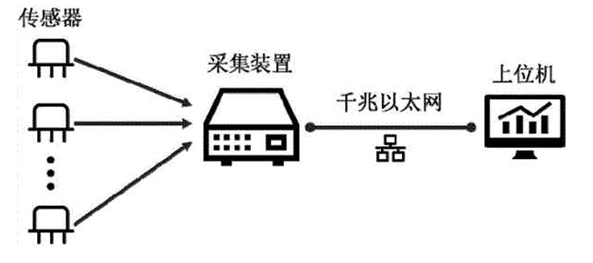

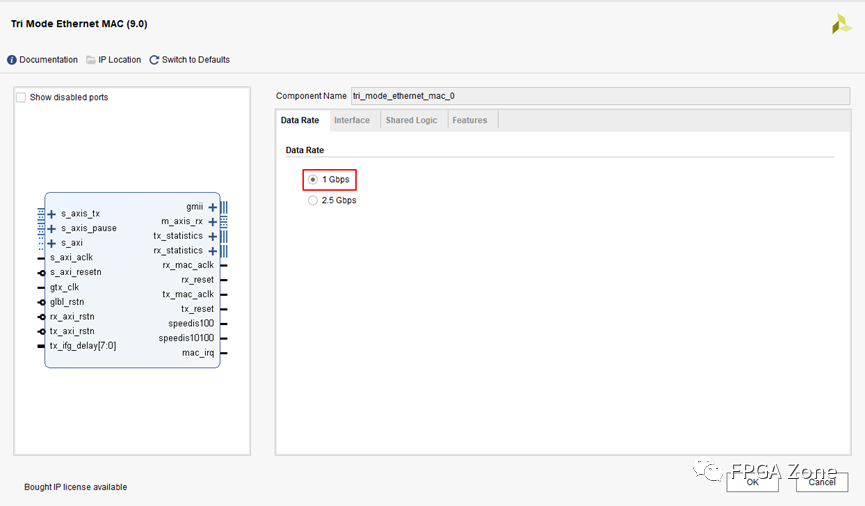

03UDP通信方案

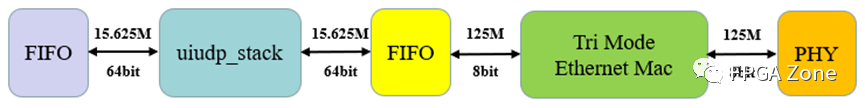

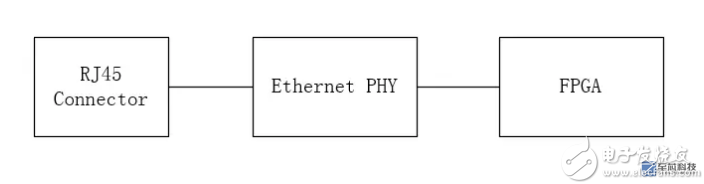

该以太网通信方案如图2所示,最上层为用户逻辑模块,用于处理和使用解析后的以太网通信数据;uiudp_stack模块采用MILIANKE提供的协议栈网表文件;FPGA 以太网IP核采用Tri Mode Ethernet Mac;PHY芯片采用88E1512;最后RJ-45接口通过网线与上位机连接。

图2 FPGA UDP以太网通信方案

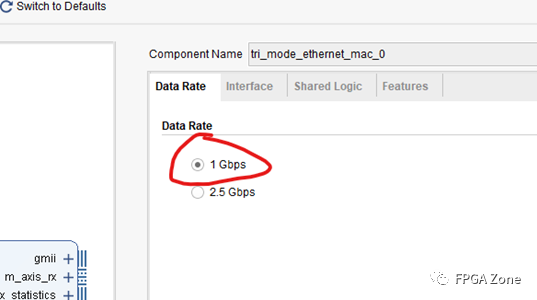

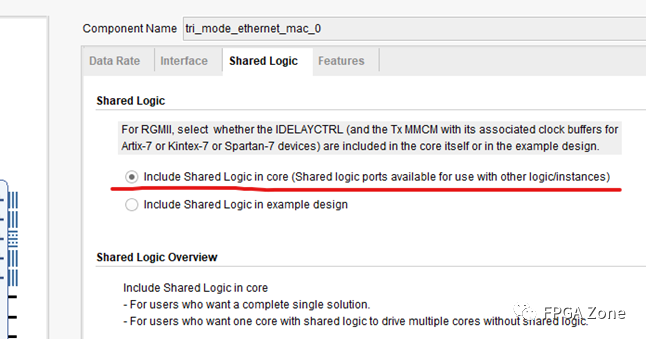

- IP核配置

使用千兆通讯,因此将速率设为 1Gbps;

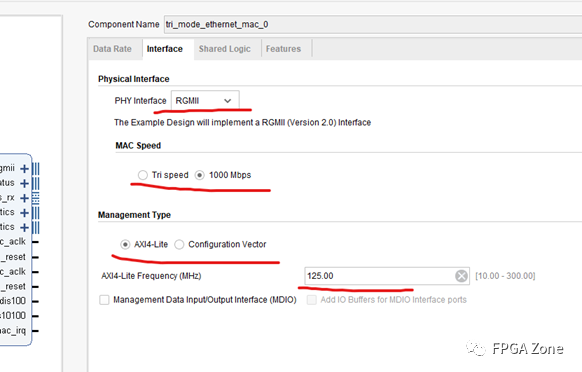

接口参数配置如下:

有关Shared Logic的选择可参考我之前写的文章。

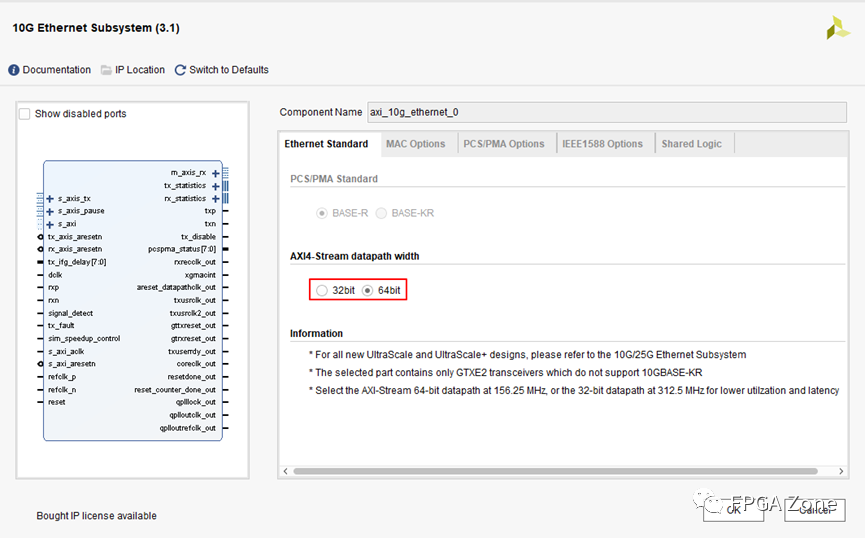

04以太网数据流回环传输方案

如图3所示,以太网数据环路传输方案,是在电脑上通过网络调试助手向FPGA发送任意小于1472字节长度的UDP数据包。由于Tri Mode Ethernet Mac IP核接口数据流为8bits/125M,而uiudp_stack为64bits/15.625M,因此需要在中间插入FIFO缓存模块,进行数据位宽转换以及跨时钟域处理。

图3 以太网数据回环传输方案

05调试遇到问题

修改电脑IP地址、子网掩码,上位机UDP端口号、IP地址,然后测试了软件功能,发现UDP丢包率较高,为30%左右,而且FPGA端接收回路数据没问题,只是发送回路有问题。因此对软件中所有模块进行测试,修改所有可能影响丢包率的代码部分,都没能解决问题。

“排除一切不可能的原因,剩下的即使再不可能,那也是真相”,当软件没有问题,那只能是硬件部分有问题了。于是我考虑这很可能是因为FPGA引脚配置不对。

一开始tx_d引脚I/O电平标准配置为LVCMOS,考虑到RGMII接口为双沿动作,数据传输速率较高,可能LVCMOS无法满足,因此参考了DDR3的设计,改用SSTL电平。编译之后重新做回环测试,UDP丢包率<1/1000,问题解决。

-

FPGA

+关注

关注

1625文章

21663浏览量

601661 -

接口

+关注

关注

33文章

8486浏览量

150804 -

千兆以太网

+关注

关注

0文章

67浏览量

13852 -

UDP

+关注

关注

0文章

322浏览量

33870 -

RGMII

+关注

关注

0文章

27浏览量

12149

发布评论请先 登录

相关推荐

基于Xilinx FPGA的千兆以太网控制器的开发

简谈基于FPGA的千兆以太网

基于FPGA的UDP RGMII千兆以太网设计

基于FPGA的UDP RGMII千兆以太网设计

评论