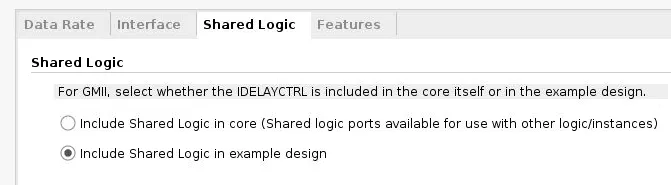

在给Vivado中的一些IP核进行配置的时候,发现有Shared Logic这一项,这里以Tri Mode Ethernet MAC IP核为例,如图1所示。

图1 IP核Shared Logic选项配置

之前都是默认选择“Include Shared Logic in Core”,一直都没考虑过“Include Shared Logic in Example Design”和“Include Shared Logic in Core”在使用上有什么区别。

从字面意思来看,“Include Shared Logic in Example Design”就是在IP核中不包括共享资源,而“Include Shared Logic in Core”则相反。Shared Logic就是共享逻辑,主要包括时钟、复位等。当选择Shared Logic in core时,这些共享的逻辑就会被集成到IP的内部。当选择Shared Logic in example design时,这些共享逻辑信号作为输入信号被IP调用。至于为什么叫in example design,是因为Vivado的IP都会提供一个例程,shared logic在example中是对外开放的,可由用户修改。

图2 例化多个IP核时shared logic信号共享连接

如图2所示,左侧的 IP 核选择了将共享资源包含在 IP 核内部,右侧的 IP 核则选择了将共享资源从 IP 核内部去除, 移至 example desgin 中。两种选项应用场景的区别主要在于:如果工程中只需要例化1个该IP核,就选择“Include Shared Logic in Core”。若需要例化多个此IP核,就可以令第一个IP选择“Include Shared Logic in Core”,将共享资源包含在 IP 核内部;其它例化的IP核选择“Include Shared Logic in Example Design”,将共享资源从 IP 核内部去除,并与第一个IP核信号共享。

-

Mac

+关注

关注

0文章

1109浏览量

51657 -

IP核

+关注

关注

4文章

331浏览量

49613 -

Vivado

+关注

关注

19文章

815浏览量

66857 -

逻辑信号

+关注

关注

0文章

12浏览量

3403

发布评论请先 登录

相关推荐

Vivado IP中的Shared Logic到底是干嘛的

Vivado IP核锁定的解决办法分享

Xilinx Vivado的使用详细介绍(3):使用IP核

Vivado IP核Shared Logic选项配置

Vivado IP核Shared Logic选项配置

评论