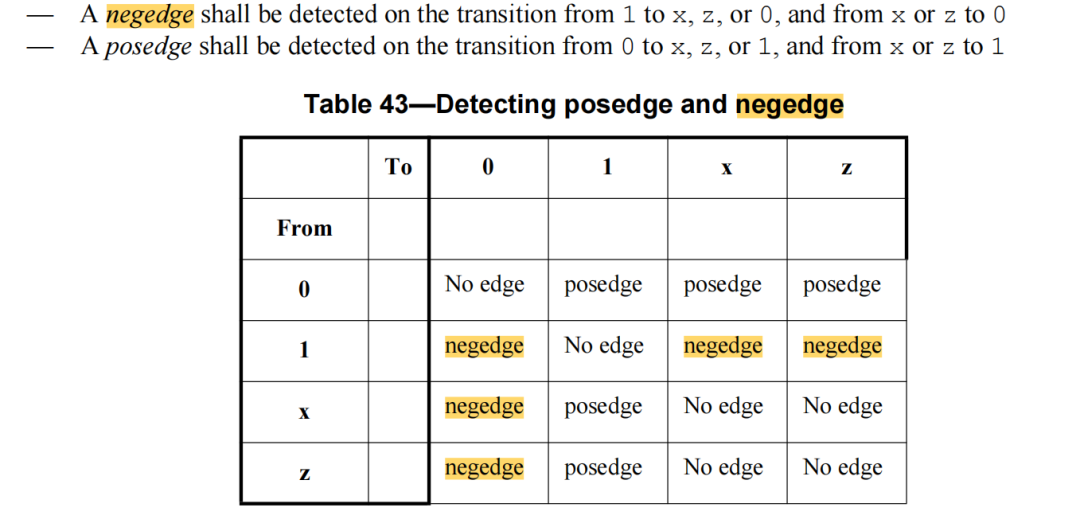

Verilog规范告诉我们:negedge 事件指的是如表43所示的跳变,发生negedge事件时才会执行操作。那么0时刻,是如何执行操作的呢?

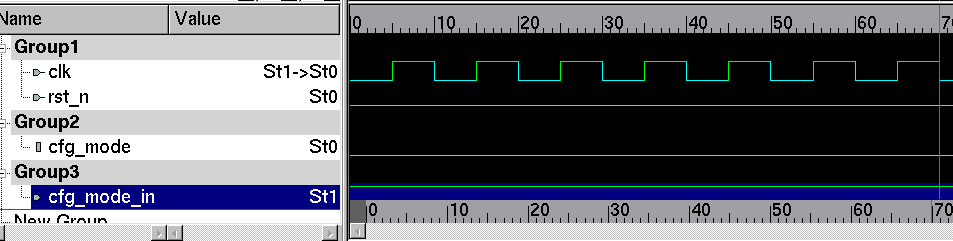

鸽子在Verilog标准中并没有找到0时刻赋值明确的说明。如下代码中,0时刻,rst_n为0,clk 处于低电平,那么cfg_mode的数值是多少呢?

always@(posedgeclkornegedgerst_n) if (!rst_n) begin cfg_mode <= 1'b0; end else begin cfg_mode <= cfg_mode_in ; end

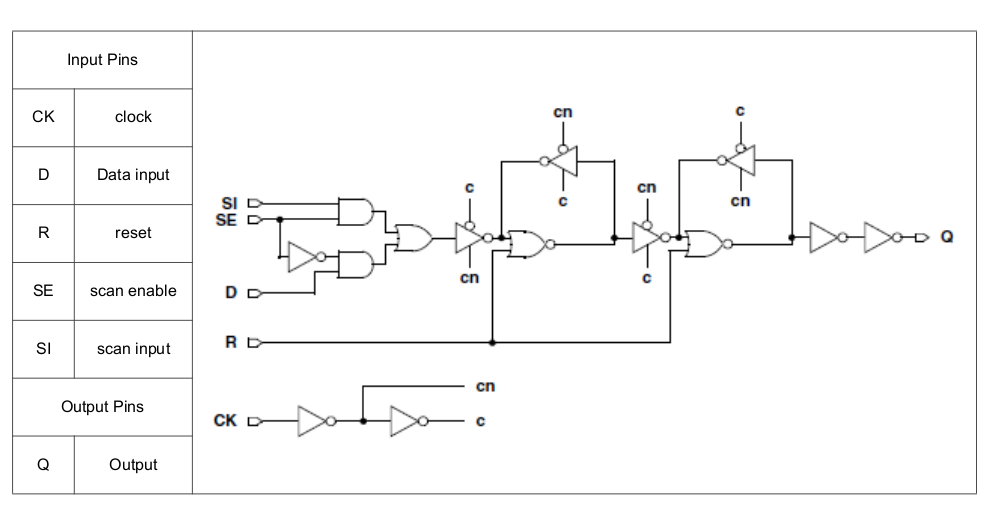

实际电路中:

在芯片上电之前,芯片的chip_reset一直处于复位状态,因此导致芯片内部的rst_n一直为0,且芯片内部PLL还没有工作,也没有产生clk,此时没有任何信号的跳变,即clk没有跳变,rst_n一直为0也没有跳变。在实际电路中,从D触发器的结构图可以看到,当复位R一直是1时,即使时钟信号不跳变,Q端输出也是0。

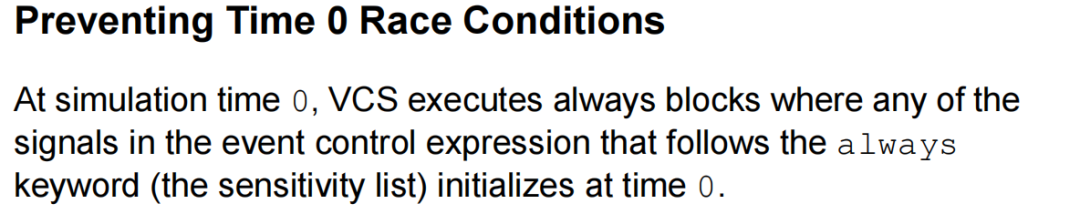

VCS在0时刻赋值

VCS 在0时刻会执行一次always块的赋值,而不是等到信号跳变。

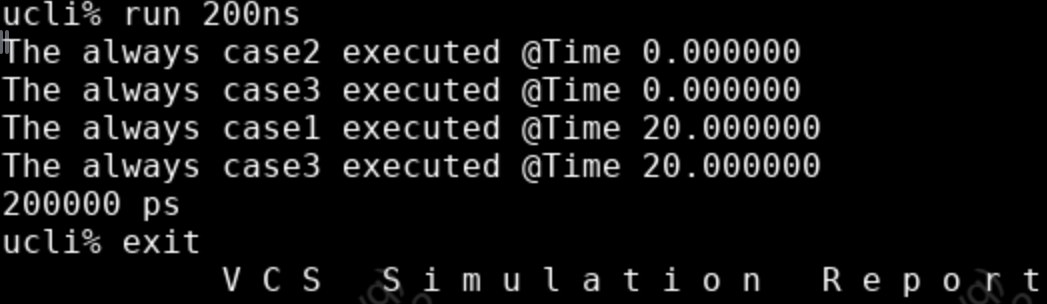

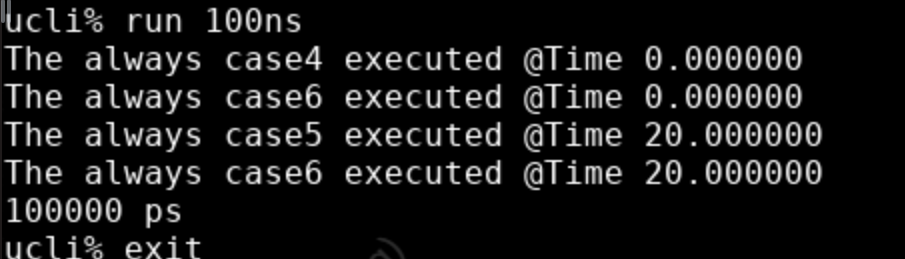

module zero_time_test; reg rst_n; initial begin rst_n = 0; #20 rst_n = 1; end always@(posedge rst_n) begin: always_case1 $display("The always case1 executed @Time %f", $time()); end always@(negedge rst_n) begin: always_case2 $display("The always case2 executed @Time %f", $time()); end always@(rst_n) begin: always_case3 $display("The always case3 executed @Time %f", $time()); end endmodule

module zero_time_test;

reg rst_n;

initial begin

rst_n = 1;

#20 rst_n = 0;

end

always@(posedge rst_n) begin: always_case4

$display("The always case4 executed @Time %f", $time());

end

always@(negedge rst_n) begin: always_case5

$display("The always case5 executed @Time %f", $time());

end

always@(rst_n) begin: always_case6

$display("The always case6 executed @Time %f", $time());

end

endmodule

审核编辑:刘清

-

寄存器

+关注

关注

31文章

5343浏览量

120380 -

D触发器

+关注

关注

3文章

164浏览量

47917 -

CLK

+关注

关注

0文章

127浏览量

17171 -

PLL电路

+关注

关注

0文章

92浏览量

6408 -

Verilog语言

+关注

关注

0文章

113浏览量

8237

原文标题:异步复位寄存器:0时刻赋值

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

常见的FPGA复位设计

寄存器reg延迟问题

简谈同步复位和异步复位

什么样的寄存器不需要复位呢?哪些寄存器是CPU能够访问的

SC130GS寄存器配置问题

Cortex-M3 内部寄存器

配置STM32寄存器控制GPIO点亮LED

异步复位寄存器的0时刻是如何进行赋值的呢?

异步复位寄存器的0时刻是如何进行赋值的呢?

评论