前面我们介绍过《EMC的三大法宝之一:接地》和《EMC的三大法宝之一:接地(二)》,本次我们就不同接地方案对EFT/B测试的影响进行举例分析。

Part 1

现象描述

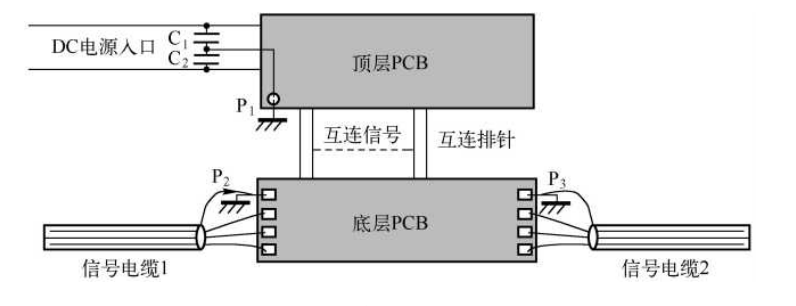

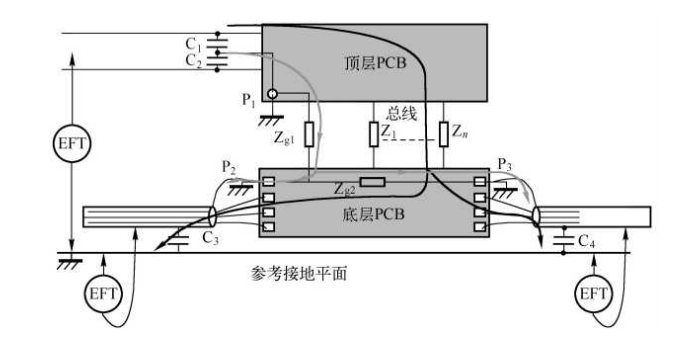

如下图所示为某产品的结构图:

在进行电源端口±2kV、信号端口±1kV的EFT/B测试时,有如下现象:

当 P1、P2、P3同时接地时, 测试全部Fail。

当只有P1接地时,电源端口的测试Pass,信号电缆1、2 测试Fail。

当P1、P2接地,P3不接地时,电源端口和电缆1测试Pass,线缆2测试 Fail。

当P1、P3接地,P2不接地时,电源端口和电缆2的测试Pass,信号电缆1测试Fail。

从结果来看,以上接地方式都不能让测试完全通过。

究竟是什么原因导致的呢?遇到这样的问题,可以从以下方面去分析:

确认接地是否良好(线的粗细、固定或者搭接方式是否合适),系统是单点接地还是多点接地。

找分布电容位置,画系统等效原理图,判断EFT共模电流的流向,从而有针对性的去改善。

Part 2

原因分析

在分析原因之前,我们首先要了解EFT/B(电快速瞬变脉冲群波形)测试的实质和特点。

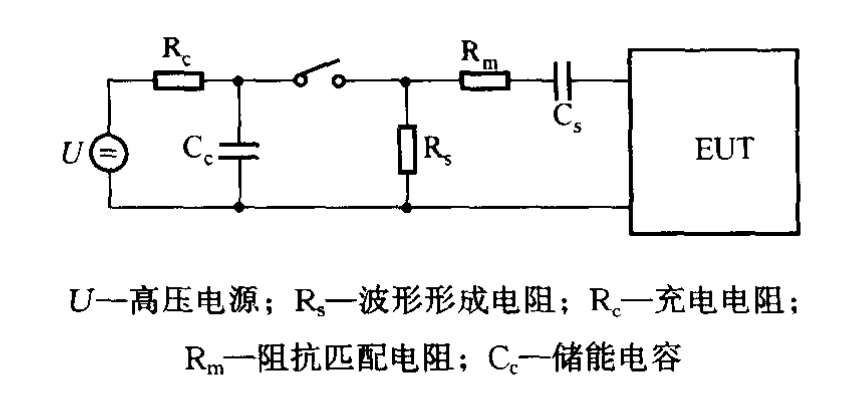

其主要是模拟电路中的感性负载(例如开关电源中的电感、电机等)断开时产生的一连串的脉冲波形,其模拟发生器原理图如下图所示:

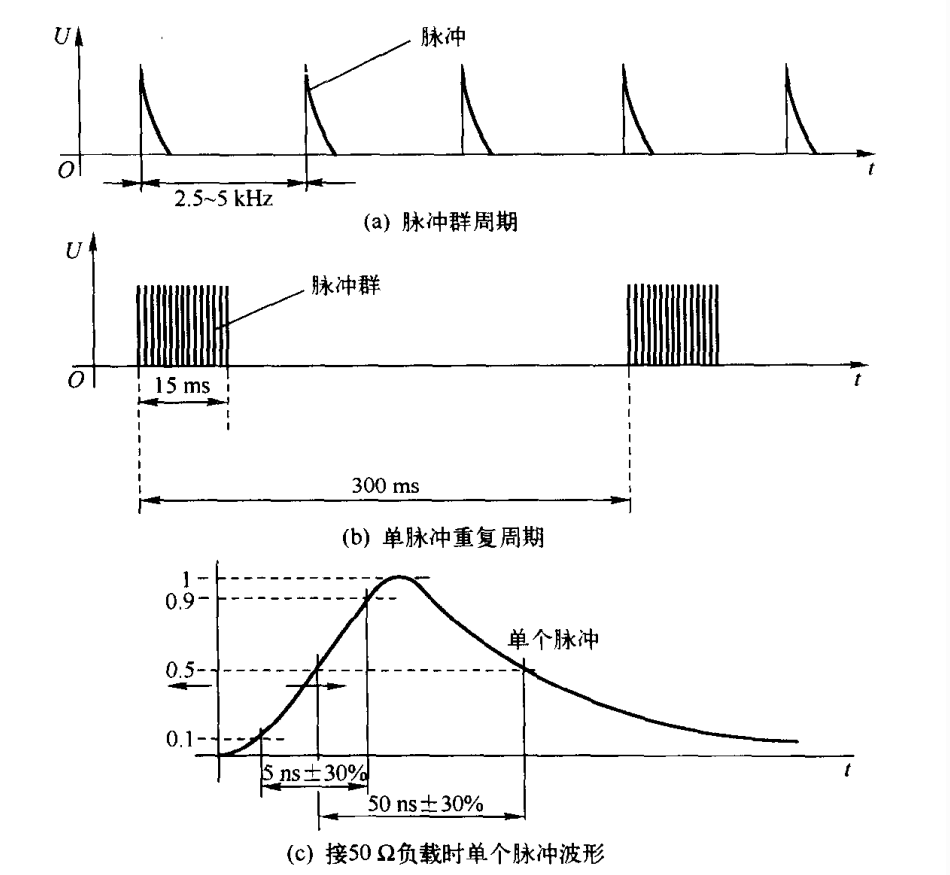

其产生的波形如下图所示:

由上图可以看出,其单个脉冲的上升延tr为5ns左右,半宽(归一化幅值的0.5倍以上的宽度)T在50ns左右。

这样周期性干扰波形具有丰富的谐波成分,周期性函数的傅里叶变换可得,其幅最大的谐波的频率(通常为1次谐波)f=1/πtr,经计算约为60MHz。

在系统中,电源线、信号线、EUT和参考接地板之间都有寄生电容(或者称为分布电容)的存在,正是因为有这些等效的电容存在,才会为EFT/B干扰提供了高频干扰路径。

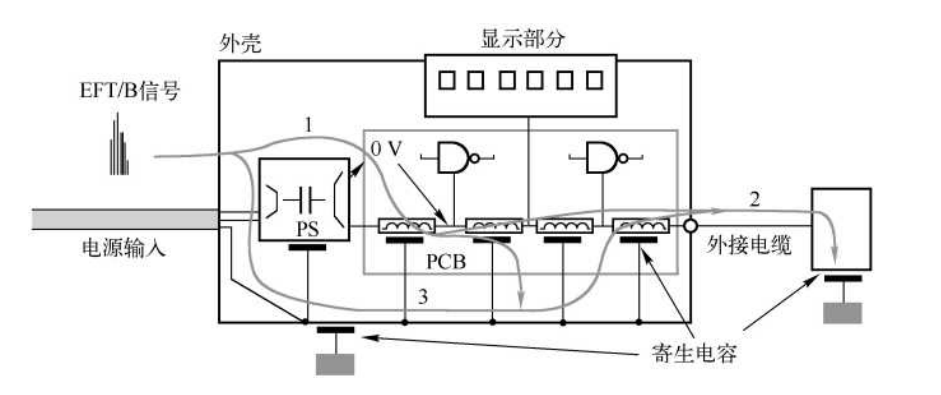

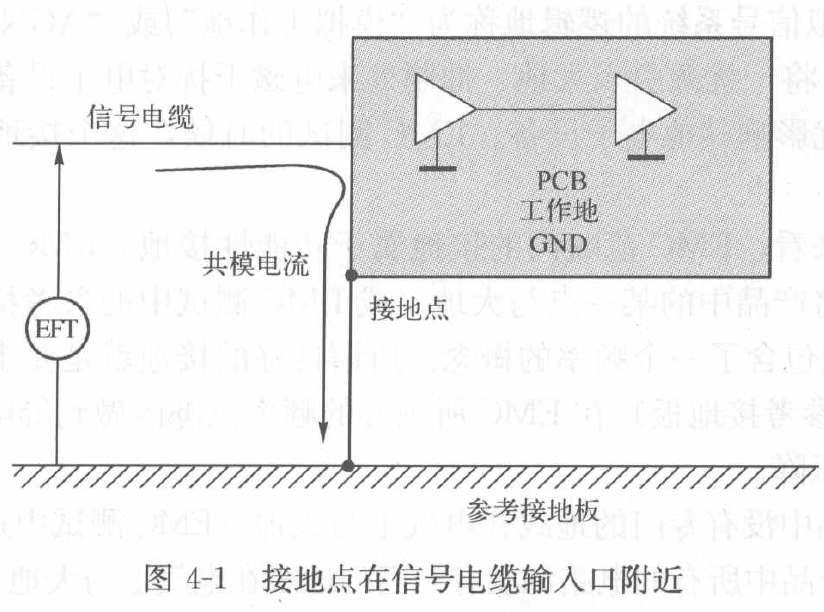

而这些干扰,通常是以共模电流的形式流入到电路中的各个单元中,进而对电路产生未知的影响,其影响设备的原理图如下所示:

周期性的连续干扰脉冲会在电路中产生累积效应,累积到一定程度,超过电路所能够承受的阈值,就会对电路产生影响。

基于这个理论,脉冲的周期越短(电容电还没有放完就又开始充电,直至达到最大),对电路的影响越大。

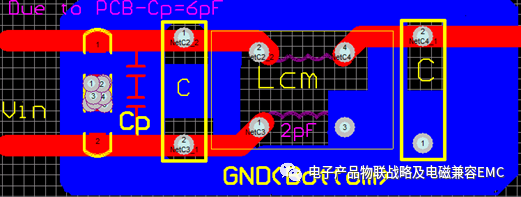

经过前面对EFT/B测试实质的分析,我们可以画出前面产品EFT/B测试的原理图:

测试时,EFT干扰脉冲群分别施加在电源端口、信号电缆1和2上,图中:

C1、C2是产品电源输入口的Y电容。

C3、C4是信号电缆对参考地的分布电容。

P1、P2、P3分别是三个接地点。

Z1~ Zn表示信号排针的阻抗。

Zg1表示地排针的阻抗。

Zg2表示 P2、P3之间互连PCB印制板布线的阻抗。

图中的箭头代表试验时共模电流的流向,因此,当在EFT/B干扰信号的远端进行接地(如P3接地)时,共模电流会从电流内部流过。

当共模电流流经电路内部时,内部电路的阻抗大小就决定了干扰电压是否会超过电路中的某些判别阈值(如逻辑电平)。

在本产品中,上下电路互联的排针在高频下的阻抗较大(一般PCB上的接插件,其分布电感有520nH,一个双列直插的24引脚的IC插座,会引入4-8nH的分布电感,有关分布电容或者分布电感的计算可以参考《PCB之分布电感&分布电容》)。

三个接地点之间是通过排针和PCB印制线接在一起的,阻抗较大,所以,需要通过单点接地来减少流过电路内部的共模电流,还需要想办法降低三点之间的阻抗,从而使得共模干扰电压最小。

我们用万用表直接测量三点之电阻,发现地线电阻都是毫欧级别的,那为什么这么小的电阻和共模电流还会产生足以干扰电路正常运行的电压呢?

那就不得不提电阻和阻抗的区别。

两者概念区别如下:

电阻:指的是在直流状态下导体对电流呈现的阻抗。

阻抗:指的是在交流状态下导体对电流呈现的阻抗,和频率有关,这个阻抗通常是由导体的等效电感产生的。

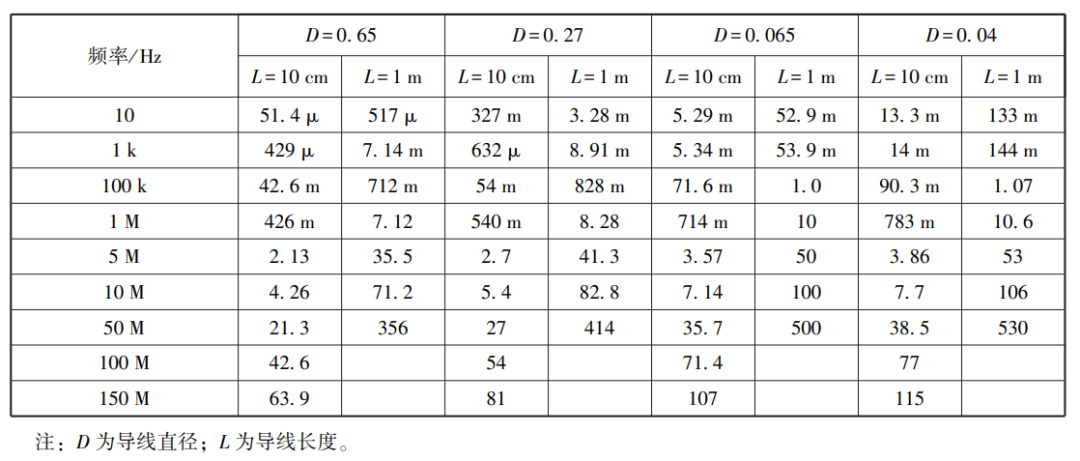

任何导体都有电感,而导体的阻抗和频率成正相关,当频率较高时,其阻抗远远大于其直流电阻。下面这个表格对比一目了然:

由表格可以看出:

对于1m长的线缆,它在10Hz的阻抗和在10MHz时的阻抗,相差1000倍甚至10万倍,因此,对于高频的电流流过地线时,其压降也会很大。

增加导线的直径可以有效地减小直流电阻,但是减小交流阻抗的作用有限。为了减少交流阻抗,在电路设计时,通常会采取平面的形式来布置,就像PCB中的完整的地平面。

像前文《EMC案例分析——连接器金属外壳搭接不良对静电放电抗扰度的影响》中介绍过的完整的、无过孔的地平面上任何两点间在100MHz的频率下, 阻抗可以认为是 3mΩ。

在这种地平面下,TTL电路可以承受600A的脉冲电流(此时的压降为1.8V),受EFT/B发生器50Ω内阻的限值,其在4kV以下的最大电流只有80A。

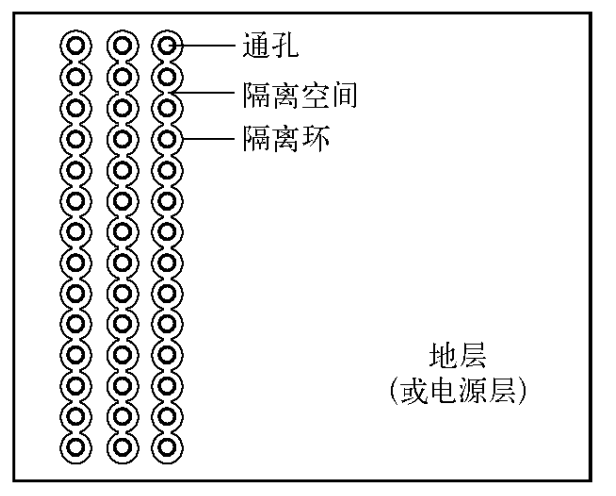

在实际的电路中,地平面上不可避免会有过孔或者缝隙,如下图所示:

每1cm长的缝隙的等效电感为10nH,那么当80A的电流流过时,产生的压降为:

U=LdI/dt=160A

式中:

L为缝隙等效电感。

dI为EFT/B产生的电流,此处假设为80A。

dt为EFT/B脉冲电流上升沿,此处假设为5ns。

这个压降对普通的数字电路是非常危险的,这就需要通过接地、滤波、添加金属平面等多种组合方式来解决干扰问题了。

可见,完整的地面对提高产品抗干扰能力非常重要,尤其对于不接地的设备来说,完整的地平面显得尤为重要。

Part 3

处理措施

通过前面的分析,我们可以通过下面的方法来解决EFT/B干扰问题:

将多点接地改为单点接地,即P1接大地(PE),P2、P3仅接信号电缆的屏蔽层。

用一块长宽比小于3的金属片(可以认为阻抗比较低)将P1、P2、P3连接在一起。

经过以上整改之后,测试通过。

Part 4

思考和启示

经过上面的分析,我们可以得到如下启示:

在高频,多点接地时的各个接地点之间的导体连接部分长宽比要保证小于5 (长宽比小于3更好)。

EFT/B干扰源的远端一定不要接地,这会导致共模电流流过电路中的地平面,从而在地平面上产品压降。

保持地平面的完整性,不但对EMS有很重要的作用,对EMI同样很重要。

有关接地,要注意以下几个方面:

对于高频元件的布局要格外小心,保证其电流环路面积最小。

PCB或者系统分区布局,高频噪声电路和低频电路分开。

PCB设计或者系统设计时,要保证干扰电流不会通过公共接地回路影响其它电路。

选择接地点时,要保证环路电流、接地阻抗及电路的转移阻抗最小。

在进行噪声分析时,可以将流过接地系统的电流看成是噪声的源头。

对于非常敏感的电路,要保证将其连接在一个稳定的参考接地平面,并保证接地平面阻抗尽量小。

审核编辑:汤梓红

-

模拟电路

+关注

关注

126文章

1611浏览量

105959 -

接地

+关注

关注

7文章

877浏览量

48026 -

PCB设计

+关注

关注

396文章

4944浏览量

96030 -

emc

+关注

关注

177文章

4482浏览量

192499

原文标题:EMC案例分析——不同接地方案对EFT/B测试的影响

文章出处:【微信号:EMC_EMI,微信公众号:电磁兼容EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

YY-0505医疗器械EMC整改测试

脉冲群EFT整改措施和影响?|深圳比创达电子a

PCB设计考虑EMC的接地技巧

电快速脉冲群(EFT)设计-EMC系列 硬件设计笔记4

EFT/B测试问题案例分析

产品接地设计与 EMC 分析:打造电磁兼容的坚实基础

EMC案例分析:不同接地方案对EFT/B测试的影响

EMC案例分析:不同接地方案对EFT/B测试的影响

评论