实现原理概括

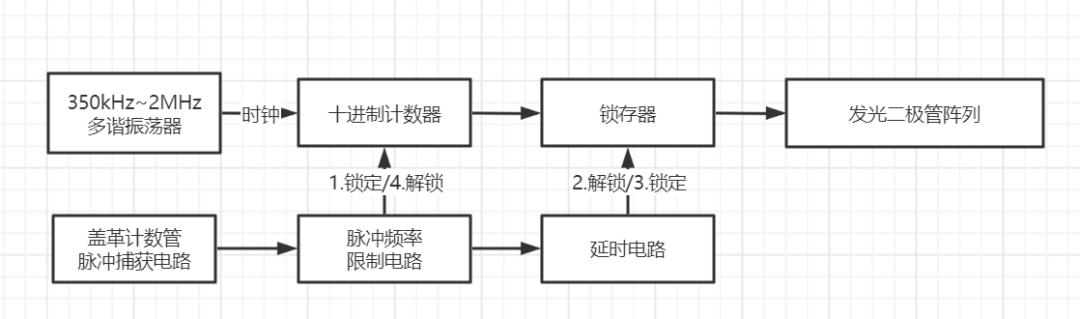

diag.2-1 原理框图

diag.2-2 总电路图

由七个模块组成。多谐振荡器 不间断地产生350kHz~2MHz的时钟脉冲,盖革计数器无输入时,***十进制计数器 ***做0,1,2,3...9,0,1,2...的周期性计数。

脉冲捕获电路 捕获并处理盖革计数管的短暂脉冲信号,触发 脉冲频率限制电路 。该电路立即锁定十进制计数器,并拒绝接收下一个输入信号,防止信号跳变对读数造成的影响。这时,十进制计数器的输出值即电路产生的随机数。

同时,延时电路 激活,在数百纳秒后解锁 锁存器 ,1~2秒后重新锁定,使锁存器在十进制计数器输出值业已锁死时保存脉冲输入时计数器的输出值。发光二极管阵列显示这个数字。

自此又数百纳秒后,脉冲频率限制电路解锁计数器,并允许接收盖革计数管的下一个信号。

** 由于盖革计数管何时产生脉冲是高度随机的,十进制计数器何时停止计数也高度随机**,这是实现真随机性的核心原理。

在七个模块中,十进制计数器选用CD4017芯片,锁存器选用74HC573芯片。下面对除发光二极管阵列外的四个模块进行解释分析。

脉冲捕获电路

diag.2-3 盖革计数管脉冲捕获电路

订正:RV3阻值当为200k

与上期推文的实验电路类似地,J3接盖革计数管阴极,脉冲经R23、R18分压,C4耦合后再经D13整流,接入电压比较器正极。R19、RV3通过分压调制一个基准电压,接比较器负极。R22是上拉电阻。

脉冲超过基准电压时,U9输出高电平,低于基准电压时输出低电平,以此完成对盖革计数管脉冲的数字化,并彻底滤除杂波。

脉冲频率限制电路

盖革计数管产生脉冲的时刻是高度随机的,但其平均间隔时间取决于当地本底辐射强度。如果辐射强度过高,则脉冲间隔过短,将对读数效果造成很大影响。因此有必要限制脉冲频率。

diag.2-4 脉冲频率限制电路原理图

图中,U6A是与(AND)门芯片74HC08的一个单元,U5是时基集成电路NE555,PULSE接脉冲捕获电路。

未出现脉冲时,C3经由R4、D3快速充电至VCC。Q输出高电平,U6A pin3为低电平,DC对地表现为高阻。

输入脉冲时,U6A pin3翻转为高电平,TH出现上升沿,U5内部电路动作,使Q输出低电平, 这时无论PULSE是否出现高电平,U6A pin3始终保持低电平,从而阻断了电路对下一个盖革管脉冲的响应,下面称这一阶段为不应期。

与此同时,DC对地短路,D3截止,C3经由D4、RV2向地放电,直至TR电位下降到低于1/3 VCC。然后,DC对地高阻,D4截止,C3通过R4、D3快速充电,Q也翻转为高电平, 使U6A pin3的电位又由PULSE决定,即允许电路响应下一个盖革管脉冲。

U8是非(NOR)逻辑门芯片74HC04。电路处于不应期时,图中U8的两个单元都输出高电平,触发后续模块。

延时锁存电路

diag.2-5 延时电路原理图(以红框标注)

延时电路用以 在前级电路已锁定计数器一段时间后,使数据进入锁存器 。

结合前一节的讲解,PULSE产生高电平时,C3将进入一个放—充电周期,其两极板电压如下图所示:

gra.2-1 C3两极板电压

如图,在约430ms时刻PULSE产生高电平,C3开始缓慢放电。1.8s时刻C3极板电压低于阈值,电路控制C3快速充电。故430ms时计数器锁定,1.8s时计数器解锁。

延时电路中U7是电压比较器芯片LM393,A/B两单元构成窗口比较器,当C3极板电压小于4V、大于2.5V时,U6:B pin3输出高电平。为了防止电路在C3充电时再度触发,引入另一个与门单元U6C,于是,只有在C3电压介于2.5~4V之间,且脉冲限制电路处于不应期时,延时电路才输出高电平。

由于电容放电时间较长,延时电路输出高电平比前级电路滞后一些:

gra.2-2 延时电路输出波形(红线标志)

这一滞后保证了锁存器解锁时,计数器输出值已经稳定,因此保证了LED阵列示数不会跳变。

变频多谐振荡器

diag.2-6 变频多谐振荡器原理图

订正:RV1阻值当为2k

多谐振荡器采用逻辑门方案,U4是四联CMOS高速与非(NAND)门芯片,U4:A/B/C指其包含的三个与非门。

电路开始工作时,由于SW1断开。U4:A pin3必定处于高电平,故U4B pin4/5都处于高电平,故U4B pin6处于低电平,C1充电至下正上负。鉴于U4A pin2寄生电容充电时间极短,R1上很快无电流经过,U4A pin2与C1下端等势,电位记为φ。

SW1闭合后瞬间,U4A pin1/2全为高电平,故pin3翻转为低电平,U4B pin6翻转为高电平。C1电荷不能立即释放,故C1下端电位提升至2φ。U4A pin2很快又与C1下端等势,此时C1通过RV1、U4B放电,电势能转化为RV1上的热能,C1、U4A pin2电势不断下降,直至低于芯片阈值0.5φ左右,此时U4A pin3翻转为高电平,U4B pin6翻转为低电平,C1下端电位降低至-0.5φ,又充电直至C1下端提升至0.5φ,U4A pin3又翻转为低电平,如此反复,形成振荡。

gra.2-3 C1下端电位-时间曲线

gra.2-4 C1下端电位、U4B pin6电位-时间曲线

由图可知,该芯片U4A pin2在上升沿、下降沿的阈值其实不同。不过我也懒得改前面写的。

电路中RV1是电位器。改变RV1的阻值,可以改变C1充放电时间,即改变电路振荡频率。RV1取1kΩ、C1取1nF时计算频率为369kHz,理论上RV1短路时电路频率无穷大,但考虑到逻辑门延迟、下级电路的计数器延迟等因素,这种谐振器的频率最高为2MHz。

-

发光二极管

+关注

关注

13文章

1199浏览量

66321 -

延时电路

+关注

关注

8文章

85浏览量

47061 -

锁存器

+关注

关注

8文章

906浏览量

41508 -

CD4017

+关注

关注

10文章

99浏览量

48842 -

多谐振荡器

+关注

关注

14文章

207浏览量

37766

发布评论请先 登录

相关推荐

一种基于FPGA的真随机数发生器设计与实现

怎么设计基于USB和FPGA的随机数发生器验证平台?

Zynq-7000 AP SoC是否具有真正的随机数发生器?

随机数发生器的相关资料分享

学习笔记 | 基于FPGA的伪随机数发生器(附代码)

真随机数发生器的容差分析

【STM32】随机数发生器详解

一种利用本底γ辐射的真随机数发生器设计

一种利用本底γ辐射的真随机数发生器设计

评论