红外探测器可将不可见的红外辐射转换为可测量的电信号。作为中波红外探测的主流,锑化铟红外探测器具有稳定的器件性能以及高可靠性,占据了大量的市场份额。作为探测器的核心,混成芯片的性能直接决定了红外探测器的性能水平,这对器件制备工艺提出了很高的要求。锑化铟混成芯片封装之前,需要通过背减薄工艺实现其量子效率最大化。

据麦姆斯咨询报道,中国电子科技集团有限公司第十一研究所的科研团队在《红外》期刊上发表了以“大面阵锑化铟探测器芯片背减薄工艺技术开发”为主题的文章。该文章第一作者为李海燕高级工程师,主要从事锑化铟、超晶格红外探测器方面的研究。

本文从背减薄工艺原理入手,针对大尺寸锑化铟红外探测器混成芯片的特点,开发了单点金刚石车削与磨抛相结合的复合背减薄工艺。结果表明,减薄后的器件表面质量满足工艺要求,双晶衍射测试达标,封装后成像质量良好。

背减薄工艺原理

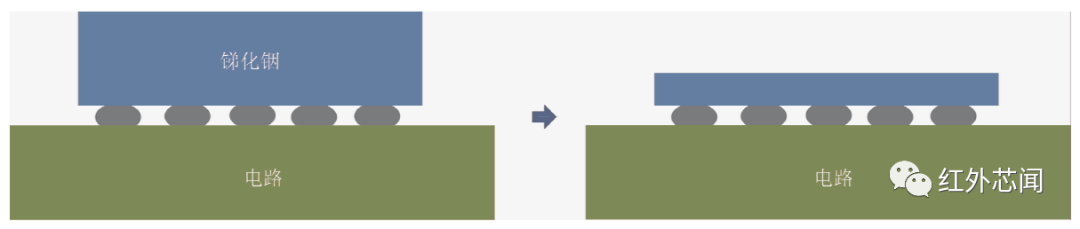

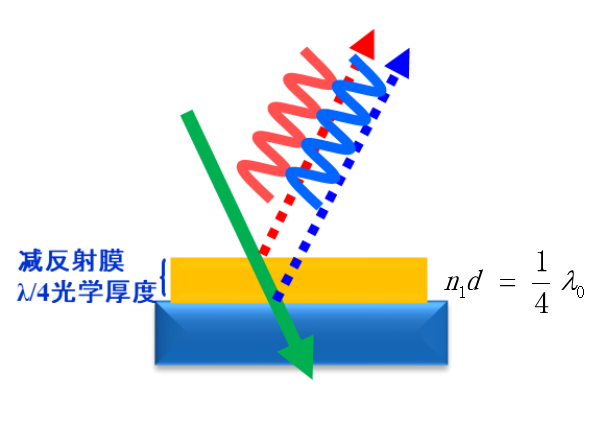

在混成芯片制备过程中,将光敏芯片与读出电路芯片倒装互连,采用背光照方式采集光信号。光照射光敏芯片,在其内部被转换为电信号,然后通过读出电路的读出、转换、放大、去噪等功能实现电信号处理与引出。为了实现量子效率的最大化,提高探测率,减小表面复合速率,使锑化铟体结构中产生的光生电荷得到最大效率的应用,其剩余厚度必须小于少子扩散长度,即30~35 μm。在工艺制备过程中,混成芯片采用背减薄工艺将锑化铟材料厚度从几百微米减小到十几微米,如图1所示。背减薄质量指标(如粗糙度、划痕、平整度、剩余厚度等)直接影响器件电学性能(如探测率和光响应均匀性),工艺设计直接决定了生产的产能能力、成品率和成本。考虑到锑化铟材料为脆性半导体材料,混成芯片自身存在应力形变,背减薄工艺开发难度极大(大尺寸锑化铟混成芯片尤甚)。

图1 背减薄工艺示意图

背减薄工艺选取

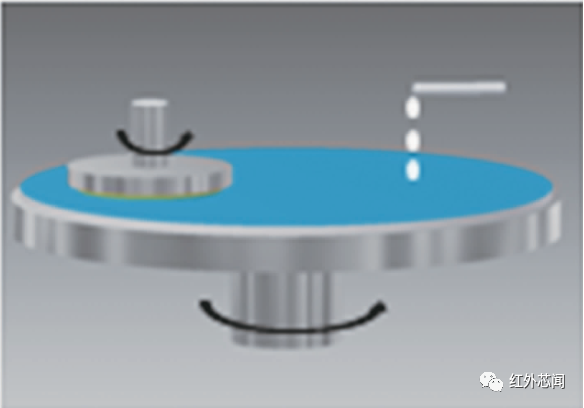

锑化铟背减薄工艺的技术水平主要从两个方面来考察:一个是表面质量,主要涉及表面平整度、表面粗糙度、表面损伤和表面外观质量(橘皮、划痕、雾面)等;另一个是成品率,主要涉及裂纹、裂片、崩边崩角等形貌问题。表面粗糙度不理想,表面损伤大,形成凹坑、橘皮形貌、相变、位错等表面损伤时,会造成表面悬挂键密度和陷阱密度大。这将吸附杂质离子,形成陷阱中心以及高表面态密度,可能会增大暗电流,导致器件性能下降。目前,主流减薄工艺基于旋转磨削原理实现器件减薄(见图2):将混成芯片倒压在磨抛盘上;在磨抛盘上加入磨抛液,施加一定的压力,在磨抛盘、芯片、磨抛料的自转及公转效果下,通过材料与磨抛盘、磨抛液产生物理、化学反应,实现材料由粗磨到精抛的加工工艺过程;在此过程中,不断实现材料减薄,同时不断去除前一道磨抛的工艺损伤,逐步实现材料表面抛光;最终,通过化学抛光去除精抛损伤层,进一步提高表面质量。该方法作为锑化铟混成芯片背减薄工艺,已经极为成熟,操作简单,被长期应用于芯片减薄工艺中。随着超精密加工技术的进步,磨抛工艺可以实现纳米级的加工质量。

图2 磨抛工艺示意图

旋转磨削加工有很多优点,其不足在于加工过程中存在大量、长时间的砂轮磨粒机械作用。这不可避免地会在器件表面形成微裂纹等损伤,不仅易引入新的应力,而且易造成裂片。锑化铟材料硬度较低,在磨抛过程中压力控制不当时极易出现裂纹、裂片情况。该问题在大尺寸混成芯片制备过程中尤为明显,极大降低了器件成品率。

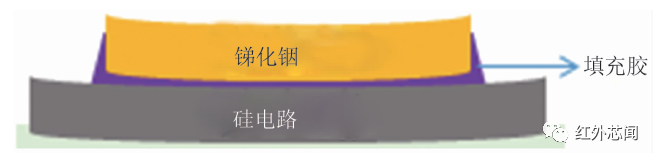

大尺寸锑化铟混成芯片由于自身存在应力,粘接在玻璃板上时会呈现四角翘曲、中心凹陷的形貌状态,如图3所示。在工艺开发中发现,若在混成芯片因自身应力而存在较大翘曲面型的情况下强行将其压平磨抛,容易造成芯片裂片,因此需要开发新的工艺技术方案进行器件减薄。

图3 混成芯片翘曲形态示意图

本文讨论1280×1024元(25 μm)大尺寸锑化铟混成芯片的背减薄工艺。芯片尺寸约为32 mm×26 mm。在大尺寸探测器上实现背减薄需要非常强的工艺控制能力:一方面要严格控制工艺损伤,避免在背减薄工艺中裂片,避免因减薄损伤而增加表面态、增大器件漏电流、降低器件性能;另一方面要实现低粗糙度光滑表面的制备。本文采用单点金刚石车削工艺配合磨抛工艺进行大尺寸锑化铟混成芯片的背减薄。

背减薄工艺过程

单点金刚石车削工艺通过机床控制单点金刚石刀具对材料进行车削。该技术已较为成熟,可实现微米级精度控制和微米级粗糙度加工。

器件表面的加工质量与刀具进给量、金刚石刀头半径、刀具磨损、机床的稳定性等多种因素相关。因此,无法通过调节刀具进给量等工艺参数无限制地优化表面质量。实际加工的材料表面的粗糙度要远大于理论值。考虑到传统的磨抛工艺已经非常成熟,在损伤及表面粗糙度的控制方面十分稳定,因此在本项目研发中,用单点车削工艺实现高成品率地去除锑化铟材料的大部分厚度,且对损伤控制、表面粗糙度方面的要求降低。通过传统磨抛工艺进一步减薄和去除单点车削损伤,然后利用更进一步的精抛工艺实现器件对粗糙度的要求,最终实现锑化铟芯片的完全减薄。

车削工艺的操作如图4所示。首先,将混成芯片粘接在玻璃基板上。测算减薄厚度后将芯片连同玻璃基板放置在车削机床上并加以固定。设置车削参数后进行车削。在车削机床上设置多级车削参数,使车削过程由粗加工向精细加工逐级进行。减薄初期,车削工艺设置以快速减薄厚度为主要目标。随着芯片厚度下降,牺牲减薄速度以逐级降低切削损伤与切削粗糙度。图5所示为车削之后的材料表面。可以看出,采用金刚石单点车削工艺进行器件减薄时,加工后的器件表面完整度良好,表面光亮。与传统的磨抛减薄工艺相比,该工艺在减薄过程中减少了外来应力带来的器件裂片风险,极大提高了成品率。

图4 车削设备加工示意图

图5 减薄后器件表面的形貌图

由于单点车削属于大进给粗抛工艺,器件表面会形成一层损伤层。损伤层的存在会严重影响器件性能。因此,单点车削步骤完成后,需进行第二步芯片精抛,通过旋转磨削工艺去除第一阶段研磨造成的损伤。单点车削完成后,由于锑化铟厚度大幅减薄,应力及翘曲情况改善。此时将混成芯片倒扣在磨抛设备上,继续减薄。裂片风险相比于原始混成芯片极大降低。本文采用的机械化学抛光法(CMP)具有简单方便、成本低的优点。该方法大致分为三个步骤:首先进行粗磨,将材料进行较大厚度量的去除,同时去除单点车削损伤;其次进行粗抛,去除粗磨带来的损伤并进一步减小锑化铟厚度;最后是精抛,主要去除粗抛损伤,同时进一步降低表面粗糙度。

结果与分析

如图5和图6所示,减薄后的混成芯片表面光亮完整。通过显微观察没有发现划道、损伤、沾污等情况。采用双晶衍射方法测试材料损伤。半峰宽值约为8.20~11.90 arcsec,基本达到测试极限,表明背减薄工艺后锑化铟晶片表面晶格的完整性很好。

图6 器件局部效果图

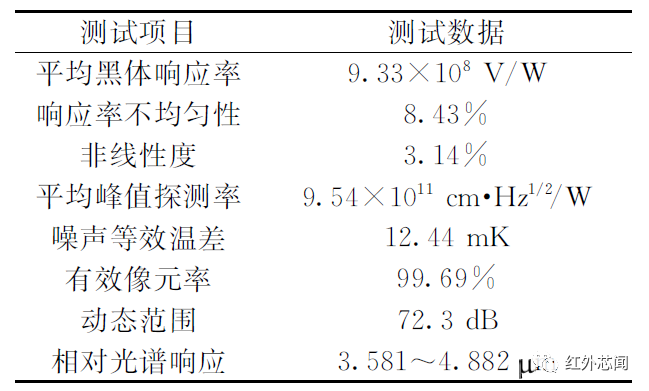

该工艺应用于1280×1024元(25 μm)大尺寸锑化铟混成芯片。芯片减薄增透后,将其封装于微杜瓦结构中进行测试(结果见表1)。图7为探测器组件的成像效果图。可以看出,该组件具有良好性能。

表1 探测器组件的光电性能参数

图7 探测器组件的成像效果图

结束语

与传统磨抛工艺相比,本文采用单点金刚石车削工艺实现混成芯片大部分厚度的减薄,然后通过磨抛工艺去除单点车削带来的材料表面损伤。采用单点金刚石车削工艺的优势在于减薄过程中减小了对混成芯片纵向上的压力,同时随着芯片厚度的不断降低,不断释放芯片应力,大大减小了裂片率;采用传统成熟的磨抛工艺去除损伤,在较低工艺难度下即可获得满足产品性能要求的混成芯片。该工艺技术尤其适用于大尺寸混成芯片的高质量减薄,对芯片的原始平整度要求低,有利于获得高均匀性、高质量的混成芯片。

审核编辑:刘清

-

转换器

+关注

关注

27文章

8705浏览量

147194 -

红外探测器

+关注

关注

5文章

289浏览量

18082 -

CMP

+关注

关注

6文章

150浏览量

26015 -

电信号

+关注

关注

1文章

817浏览量

20585

原文标题:大面阵锑化铟探测器芯片背减薄工艺技术开发

文章出处:【微信号:MEMSensor,微信公众号:MEMS】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

背钻设计与生产:技术解析及应用

晶圆为什么要减薄

芯丰精密第二台12寸超精密晶圆减薄机成功交付

eXcelon ®工艺介绍

背钻设计时要优先保证哪一项,STUB长度真的是越短越好吗

光学减反膜的工作原理和制作工艺

晶盛机电减薄机实现12英寸30μm超薄晶圆稳定加工

X-FAB为其CMOS传感器工艺平台引入背照技术

北京中电科国内首创WG-1220自动减薄机交付

RFID背夹在仓库管理中的应用

背减薄工艺的原理是什么?背减薄工艺过程介绍

背减薄工艺的原理是什么?背减薄工艺过程介绍

评论