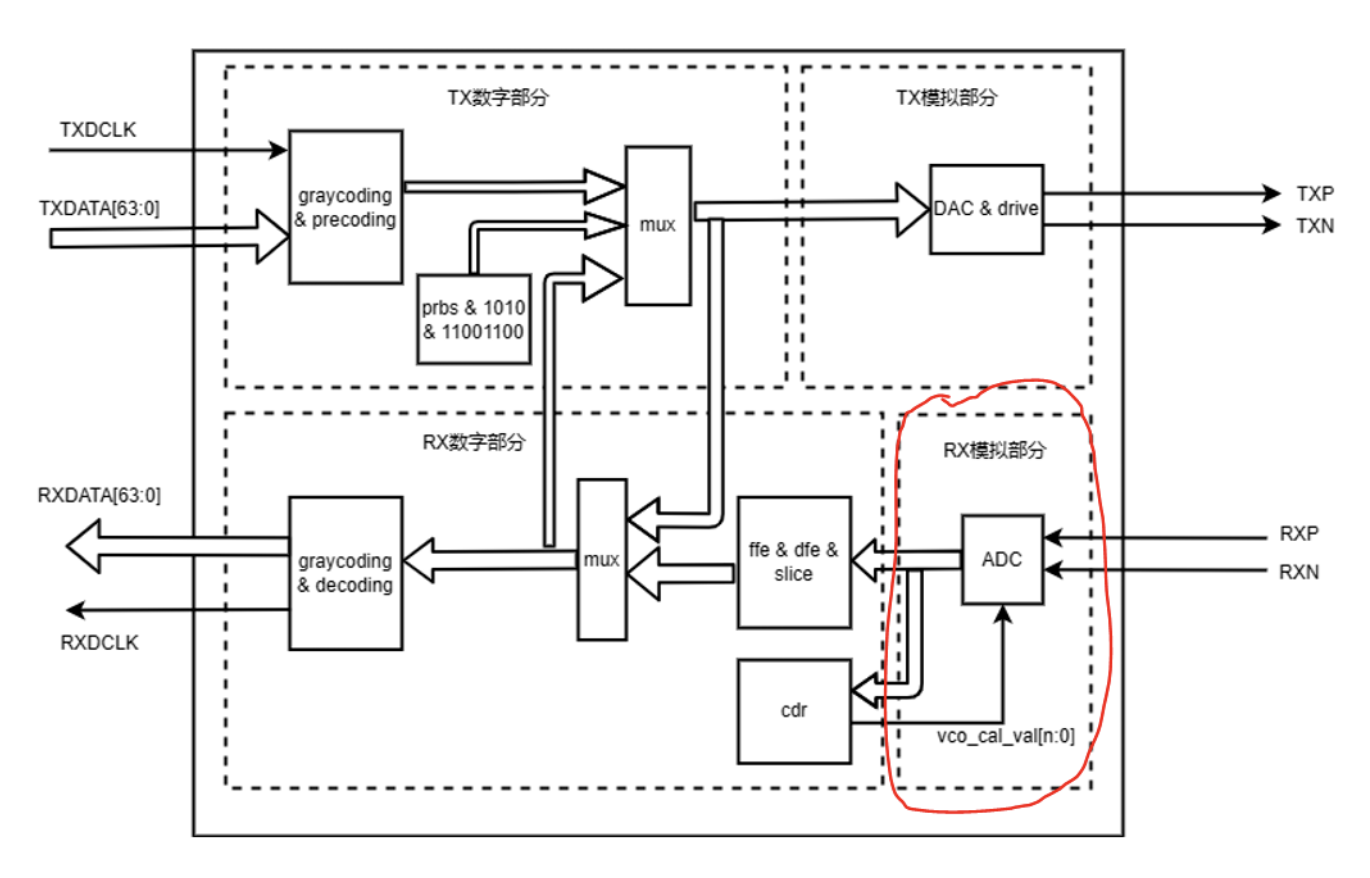

对于图1所示TX/RX模拟部分的实现方式,大家是不是一直有这样的疑问: Serdes在将并行data通过DAC串行发出去的时候,或者在接收端通过ADC进行串行data采样的时候,是怎么实现的?比如56G的serdes就是用56G的ADC和DAC吗?

答案是肯定不是,没有那么高频的ADC和DAC,通常ADC和DAC最大可以工作在1G频率左右,再大的频率无法实现精度的。所以采用多个ADC/DAC分时工作的模式。

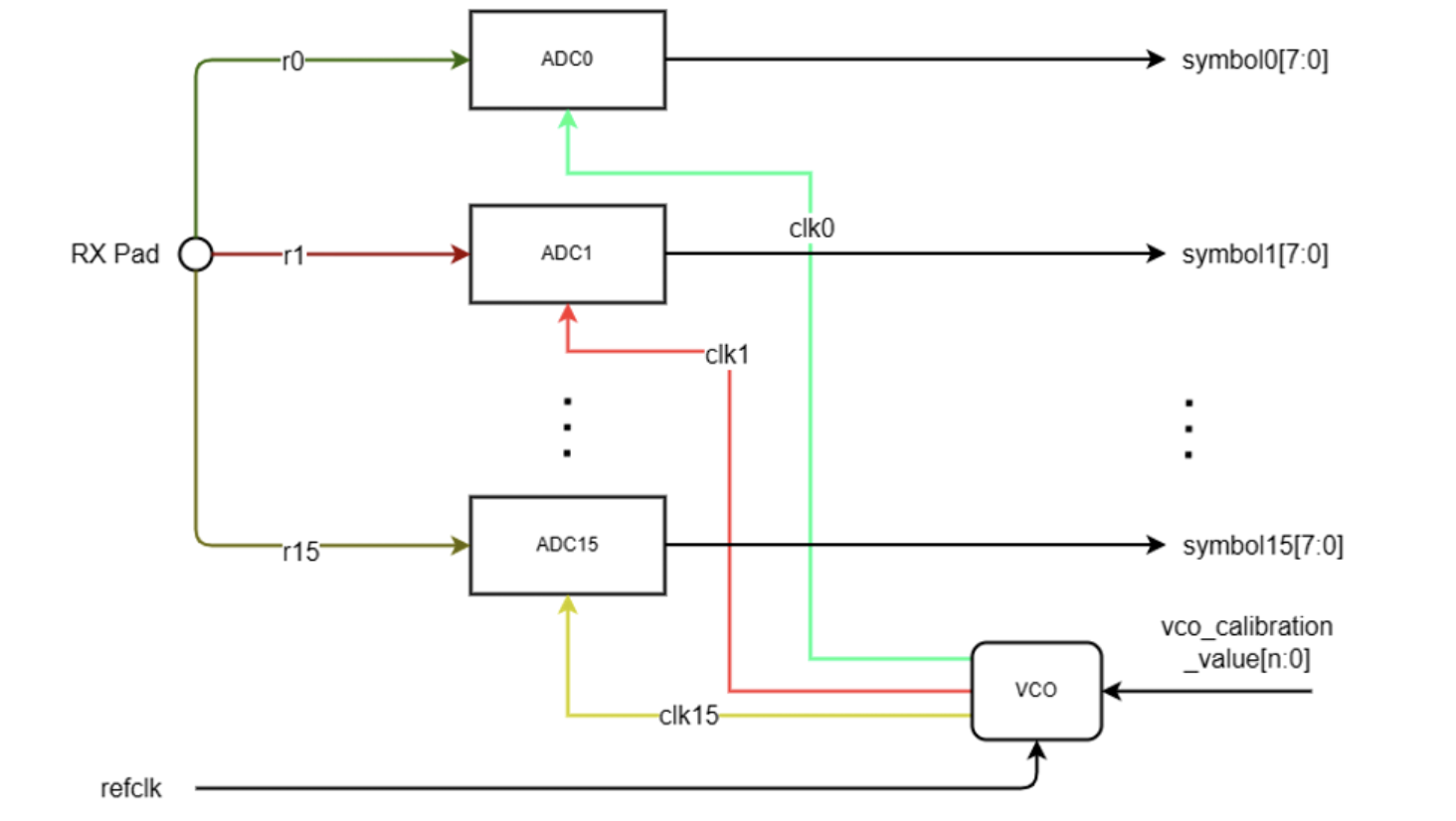

RX接收端采样方式如下图2,RX Pad连接到16个ADC上,后端要严格约束Pad到不同ADC之间的走线一样长,可以通过绕线方式实现。

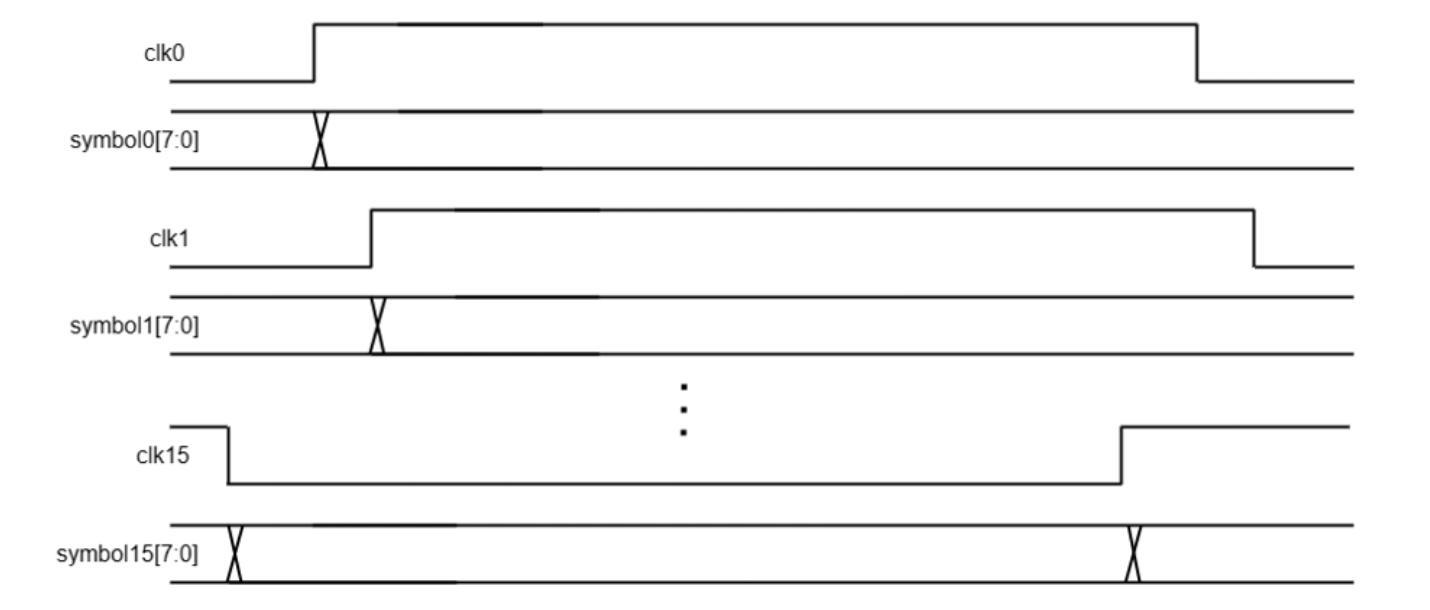

CDR的数字逻辑输出vco_calibration_value[n:0]到模拟VCO实现相位调整。VCO输出多路时钟到多个ADC,如图3所示,比如通过16个ADC分时采样,VCO输出的相邻时钟差90°/16。

ADC在时钟上升沿进行采样,然后模拟通过clk15将16个采样symbol[7:0] pipe到数字逻辑,然后进行均衡判决。TX端的DAC发送端是相同的方式进行的。

图1:serdes架构框图

图2:RX ADC采样框图

图3:RX ADC采样时钟图示

-

接收机

+关注

关注

8文章

1181浏览量

53469 -

adc

+关注

关注

98文章

6498浏览量

544596 -

时钟信号

+关注

关注

4文章

448浏览量

28568 -

ADC采样

+关注

关注

0文章

134浏览量

12845 -

VCO设计

+关注

关注

0文章

2浏览量

3489 -

SERDES接口

+关注

关注

0文章

28浏览量

2983

发布评论请先 登录

相关推荐

SERDES接口电路设计

FPGA SERDES接口电路怎么实现?

SERDES传输和引脚关联

使用SERDES(LVDS)作为背板怎么实现?

SerDes是怎么工作的

基于SERDES时钟的频率跟随的设计

如何使用FPGA实现SERDES协议

serdes串行发送和接收是怎么实现的?serdes就是用56G的ADC和DAC吗?

serdes串行发送和接收是怎么实现的?serdes就是用56G的ADC和DAC吗?

评论