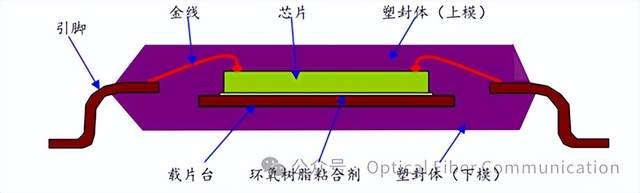

在集成电路发展的数十年里,封装形式从最典型的DIP、QFP发展到系统级SiP封装和PoP封装(Package on Package),再到如今的2.5D、3D高阶封装,封装技术和集成度得到了显著提升。

2.5D封装简介

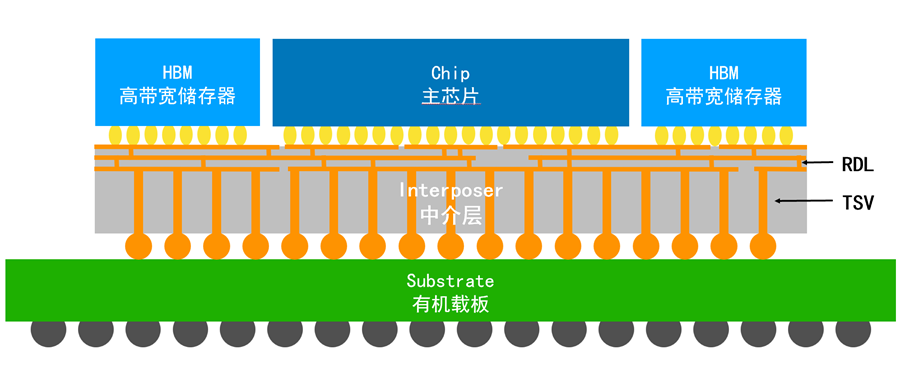

2.5D封装通常应用于高性能的CPU、FPGA和人工智能等领域。它是一种将主逻辑芯片和HBM高带宽储存器等芯片同时集成的封装形式,具体的封装结构因厂家而异,主流的技术路线包括英特尔的EMIB和台积电的CoWoS。以CoWoS为例,它是由Chip on Wafer on Substrate缩写而来,即先将各主芯片和储存器集成堆叠到无源的Wafer(中介层)上,再将CoW部分封装在有机载板Substrate上。

2.5D封装芯片的典型结构

2.5D封装芯片的典型结构Interposer上的RDL使得各芯片之间的电信号可以直接交流,并通过Interposer中的硅通孔(TSV)传输到有机载板以完成与外界的连接。这种封装形式具有以下优点:

1、减小器件所占用的面积,充分利用纵向空间,降低功耗;

2、缩短各芯片之间的电信号传输距离,减少导线寄生电容的影响。

然而,复杂的封装过程也增加了制程工艺的难度,导致某些制程环节成本高昂以及整体良率下降等问题。

切片制样是常见的破坏性物理分析手段,常见于检查器件内部结构或缺陷等场景。在制样过程中,需要避免人为引入的noise和crack,否则将影响我们对器件本身的缺陷的判断。

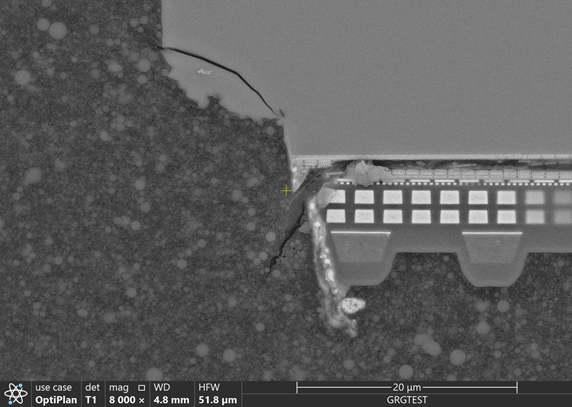

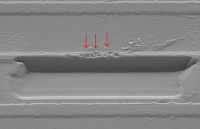

难点1:避免机械应力对芯片结构的异常损伤

在复杂封装如2.5D,3D封装中,主芯片为通常采用ELK材质工艺的先进制程芯片,由于ELK材质自身对机械应力承受能力较低的特点,在切片制样过程中极易出现研磨导致金属布线层出现Crack,严重的甚至会使金属布线层与衬底直接分层。

图2 2.5D封装切片制样裂纹的典型形貌

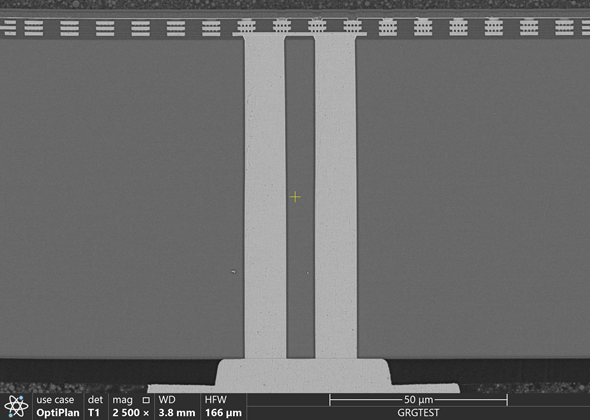

图2 2.5D封装切片制样裂纹的典型形貌难点2:微结构尺寸较小易磨过位置

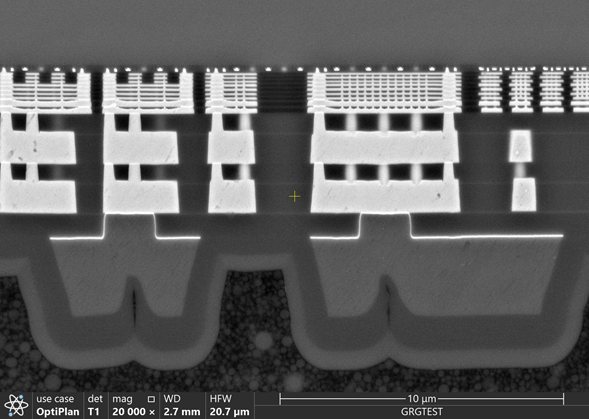

一般采用复杂封装如2.5D封装形式的器件,整体尺寸可超过5*5cm,但是,器件内部的关键结构尺寸却在微米级。如下图,TSV孔在同一排中可存在超过150个相同的结构,每个TSV孔直径仅10微米。要保证所有结构都能同时呈现在一个截面中,切片制样时左右两端研磨深度误差就不能超过10微米;需要在研磨过程中进行精细控制。

图3 TSV通孔剖面形貌

图3 TSV通孔剖面形貌广电计量的服务优势

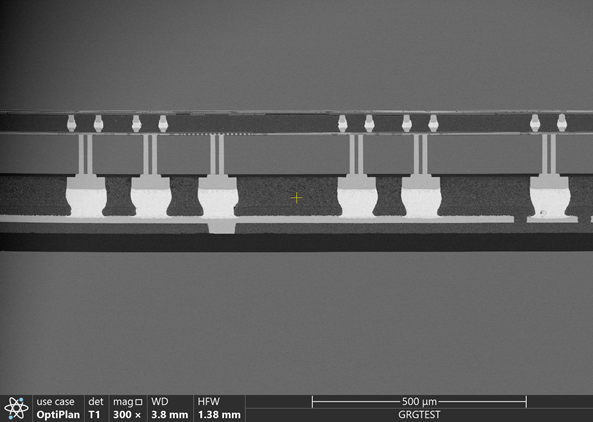

广电计量DPA团队,通过多年在高阶封装的DPA分析技术上的不断探索,在高阶封装的DPA(破坏性物理分析)领域积累了大量的经验;能够对FCBGA,COWOS,SIP,FOP等复杂封装集成电路进行定点切片制样的同时不会引入结构分层,开裂等制样异常。同时配合OM,SEM等微观分析技术,可以进一步分析高阶封装内部的芯片互联工艺质量,underfill填充质量,芯片金属电路工艺质量以及复杂封装的封装应力筛查,失效形貌观察等图:

图4 2.5D封装剖面局部形貌(COWOS)

图4 2.5D封装剖面局部形貌(COWOS) 图5 2.5D封装芯片ELK位置局部形貌

图5 2.5D封装芯片ELK位置局部形貌 -

元器件

+关注

关注

113文章

4756浏览量

93026 -

封装

+关注

关注

127文章

8061浏览量

143596 -

DPA

+关注

关注

0文章

31浏览量

15770 -

失效分析

+关注

关注

18文章

220浏览量

66526

发布评论请先 登录

相关推荐

余承东疑再次喊话比亚迪,高阶智驾如何界定?

聚焦离子束FIB在失效分析技术中的应用-剖面制样

比亚迪全系车型搭载高阶智驾技术

破坏性物理分析(DPA)技术在元器件中的应用

轻舟智航中高阶智驾解决方案再获项目定点

芯片为什么要进行封装?

DPA分析-高阶封装的剖面制样

DPA分析-高阶封装的剖面制样

评论