1. 什么是BSDL文件?

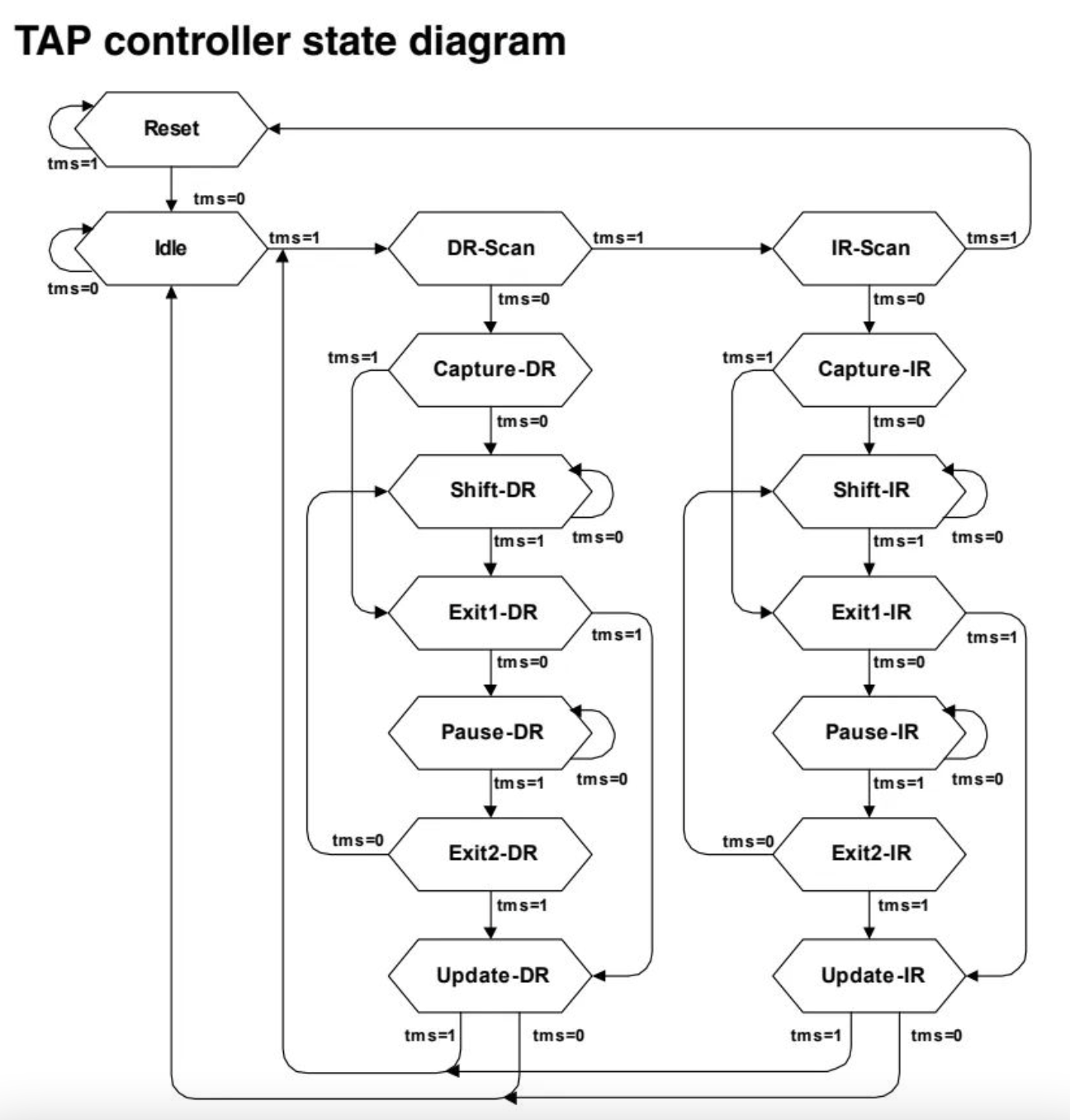

上一篇文章,我们介绍了JTAG边界扫描的基础知识,今天我们来看看边界扫描测试必须使用到的一个文件,BSDL文件。BSDL,Boundary Scan Description Language的缩写,即边界扫描描述语言,属于VHDL的一个子集,内容符合VHDL的语法标准,用于描述JTAG在指定设备中的实现方式,只要设备符合JTAG标准,那么它必须具有对应的BSDL文件。BSDL文件主要包括以下信息:BSDL目前有两种标准IEEE 1149.1和IEEE 1149.6。IEEE 1149.6在IEEE 1149.1标准的基础上丰富了一些内容,它可以兼容IEEE 1149.1。2. BSDL文件的获取

方式1:BSDL Library

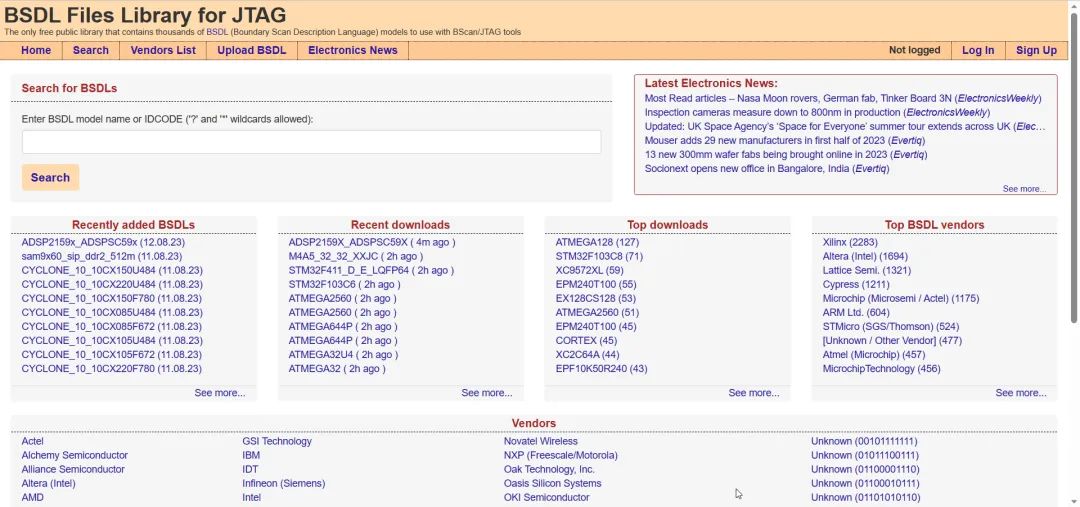

https://www.bsdl.info/ 这个网站几乎包括所有支持JTAG芯片的BSDL文件,超过100家半导体公司的上万款芯片,包括MCU、DSP、PowerPC、CPLD、FPGA等,现在还在持续更新中。

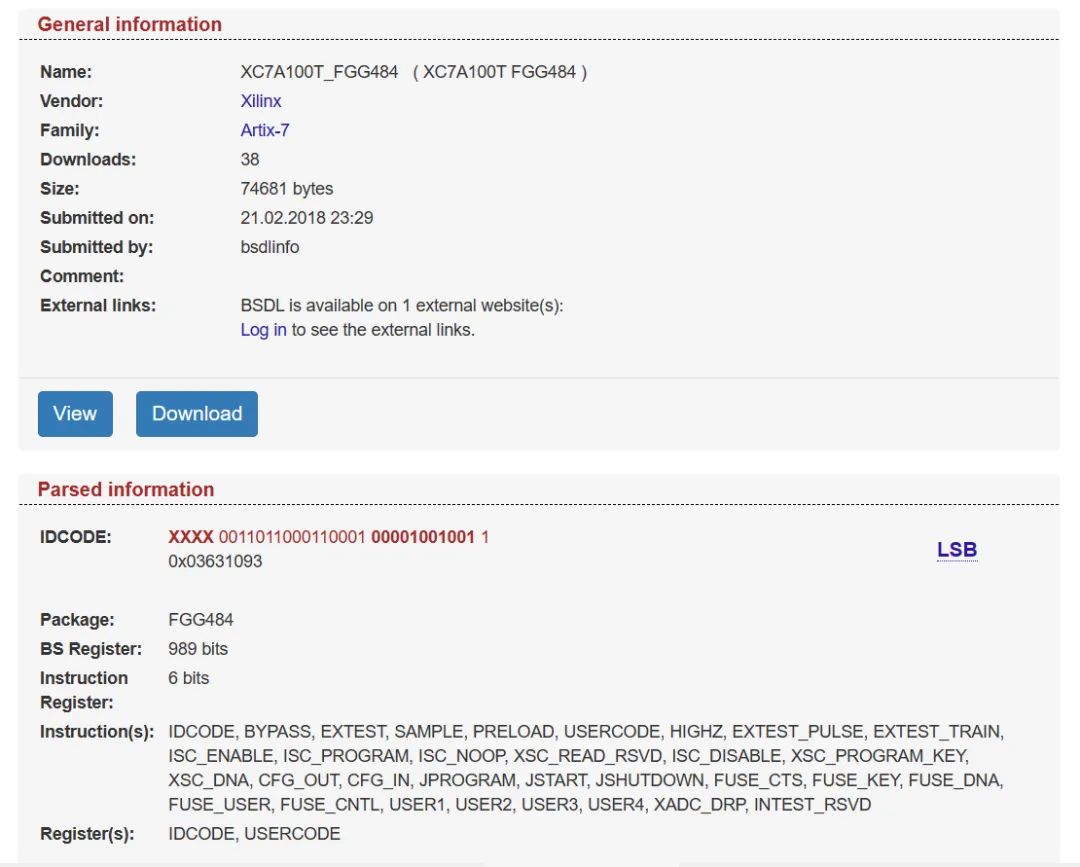

支持通过芯片型号或IDCODE搜索对应的BSDL文件,可以在线进行预览,非常方便

支持通过芯片型号或IDCODE搜索对应的BSDL文件,可以在线进行预览,非常方便

方式2:各芯片的官方网站

在各大芯片厂商的官方网站一般会提供BSDL文件,下面以Xilinx、Altera、Microsemi、ST意法半导体为例,介绍如何获取BSDL文件。Xilinx FPGA BSDL文件获取

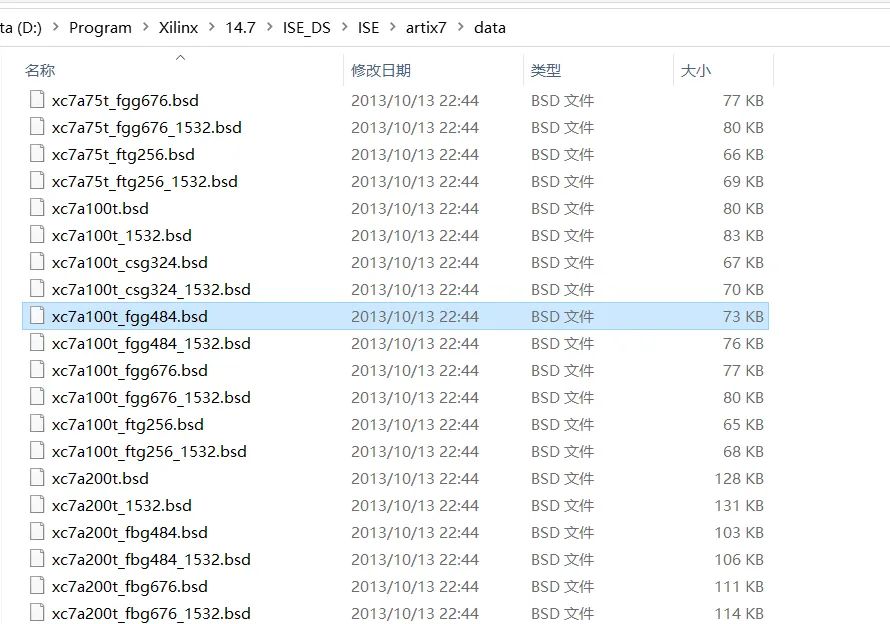

Xilinx CPLD/FPGA BSDL文件一般位于开发环境ISE或Vivado安装路径下:ISE 14.7对应路径为,例如Artix-7系列XC7A100T的BSDL文件位于:Xilinx14.7ISE_DSISEartix7data

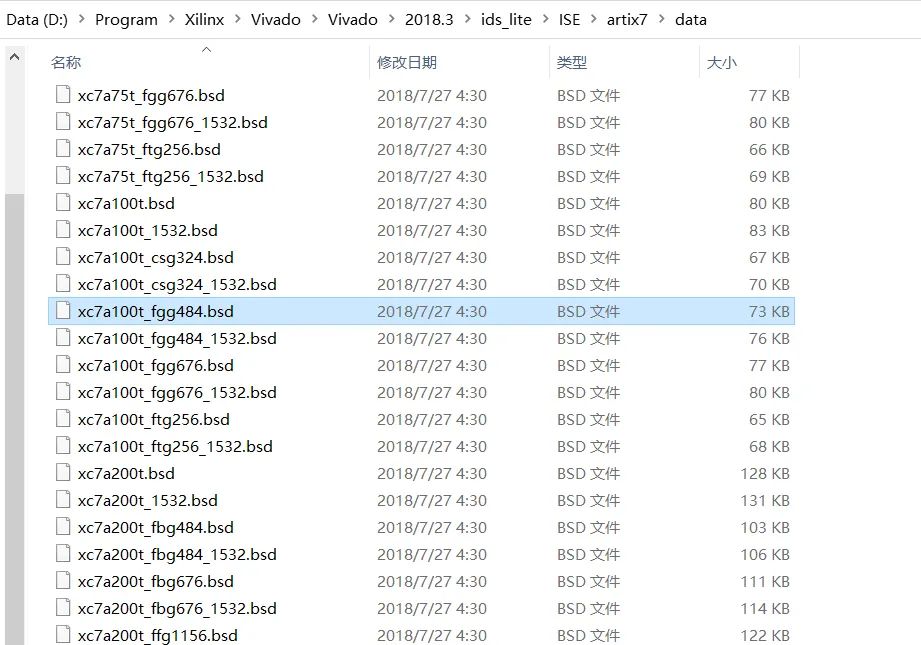

Vivado 2018.3对应路径如下:

Vivado 2018.3对应路径如下:VivadoVivado2018.3ids_liteISEartix7data

除了开发环境的安装目录,Xilinx还在官方网站上提供有各系列FPGA的BSDL文件下载:

除了开发环境的安装目录,Xilinx还在官方网站上提供有各系列FPGA的BSDL文件下载:https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/device-models/bsdl-models/artix-series-fpgas.html

Altera FPGA BSDL文件获取

由于我的电脑没装Quartus开发环境,所以不确定BSDL文件是否能在安装路径下找到,Altera官方网站也可以进行下载:IEEE 1149.1 BSDL 文件下载https://www.intel.cn/content/www/cn/zh/support/programmable/support-resources/board-layout/bsd-11491.html IEEE 1149.6 BSDL 文件下载

https://www.intel.cn/content/www/cn/zh/support/programmable/support-resources/board-layout/bsd-11496.html

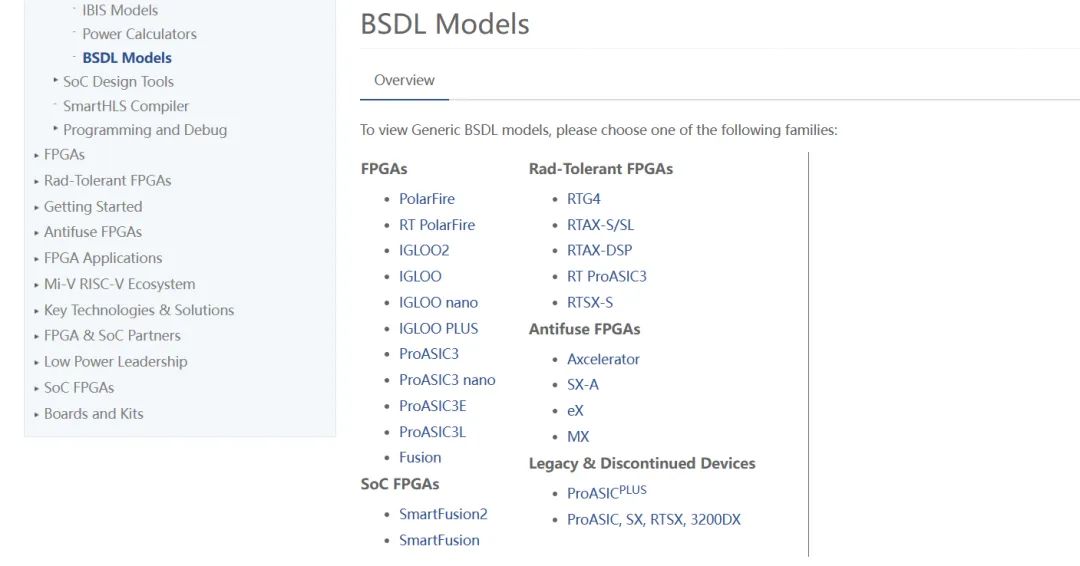

Microsemi FPGA BSDL文件获取

Microchip(Microsemi)FPGA的BSDL模型下载地址:https://www.microsemi.com/product-directory/design-resources/1717-bsdl-models

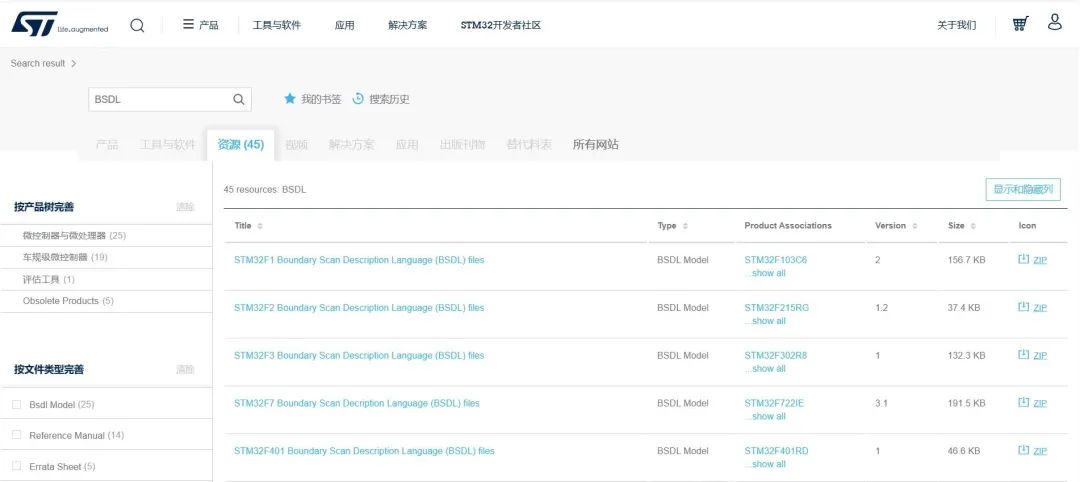

ST MCU BSDL文件获取

意法半导体MCU的BSDL文件可以到官方网站搜索BSDL,就会弹出对应系列的BSDL文件包。 部分系列的BSDL文件下载地址:

部分系列的BSDL文件下载地址:STM32F1: https://www.st.com/content/ccc/resource/technical/ecad_models_and_symbols/bsdl_model/75/4a/50/d0/ad/aa/49/92/stm32f1_bsdl.zip/files/stm32f1_bsdl.zip/jcr:content/translations/en.stm32f1_bsdl.zip STM32F2: https://www.st.com/content/ccc/resource/technical/ecad_models_and_symbols/bsdl_model/e9/d6/86/75/13/99/46/c8/stm32f2_bsdl.zip/files/stm32f2_bsdl.zip/jcr:content/translations/en.stm32f2_bsdl.zip STM32F17: https://www.st.com/content/ccc/resource/technical/ecad_models_and_symbols/bsdl_model/ad/a6/69/0f/70/95/49/92/stm32f7_bsdl.zip/files/stm32f7_bsdl.zip/jcr:content/translations/en.stm32f7_bsdl.zip

3. BSDL文件示例

下面是Xilinx CPLD XC95144的BSDL文件的部分内容:-- --BSDLFilecreated/editedbyBCADBSDEditorVersion3.1 -- --BSDE$Header:/devl/xcs/repo/env/Jobs/iMPACT/data/xc9500/xc95144.bsd,v1.22000/10/240057sanjaysExp$ --BSDEXilinx144macrocellFastFLASHISPCPLD entityXC95144is generic(PHYSICAL_PIN_MAP:string:="DIE_BOND"); port( PB00_00:inoutbit; PB00_01:inoutbit; PB00_02:inoutbit; ........ VSSINT_4:linkagebit; VSSIO_1:linkagebit; VSSIO_2:linkagebit; VSSIO_3:linkagebit; VSSIO_4:linkagebit; VSSIO_5:linkagebit; VSSIO_6:linkagebit; VSSIO_7:linkagebit; VSSIO_8:linkagebit; VSSIO_9:linkagebit ); useSTD_1149_1_1990.all; attributePIN_MAPofXC95144:entityisPHYSICAL_PIN_MAP; constantDIE_BOND:PIN_MAP_STRING:= "PB00_00:PAD25,"& "PB00_01:PAD18,"& "PB00_02:PAD19,"& "PB00_03:PAD27,"& "PB00_04:PAD21,"& "PB00_05:PAD22,"& "PB00_06:PAD32,"& "PB00_07:PAD23,"& "PB00_08:PAD24,"& "PB00_09:PAD34,"& ........ "VSSIO_3:PAD51,"& "VSSIO_4:PAD80,"& "VSSIO_5:PAD99,"& "VSSIO_6:PAD110,"& "VSSIO_7:PAD120,"& "VSSIO_8:PAD137,"& "VSSIO_9:PAD160"; attributeTAP_SCAN_INofTDI:signalistrue; attributeTAP_SCAN_OUTofTDO:signalistrue; attributeTAP_SCAN_MODEofTMS:signalistrue; attributeTAP_SCAN_CLOCKofTCK:signalis(1.00e+07,BOTH); attributeINSTRUCTION_LENGTHofXC95144:entityis8; attributeINSTRUCTION_OPCODEofXC95144:entityis "BYPASS(11111111),"& "CONLD(11110000),"& "EXTEST(00000000),"& "FERASE(11101100),"& "FBULK(11101101),"& "FPGM(11101010),"& "FPGMI(11101011),"& "FVFY(11101110),"& "FVFYI(11101111),"& "HIGHZ(11111100),"& "IDCODE(11111110),"& "INTEST(00000010),"& "ISCEN(11101000),"& "SAMPLE(00000001),"& "USERCODE(11111101)"; attributeINSTRUCTION_CAPTUREofXC95144:entityis"000XXX01"; attributeINSTRUCTION_DISABLEofXC95144:entityis"HIGHZ"; attributeIDCODE_REGISTERofXC95144:entityis "0010"&"1001010100001000"&"00001001001"&"1"; attributeUSERCODE_REGISTERofXC95144:entityis "XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX"; attributeREGISTER_ACCESSofXC95144:entityis "BYPASS(CONLD,HIGHZ),"& "ISCENABLE[12](ISCEN),"& "ISCONFIGURATION[27](FERASE,FBULK,FPGM,FVFY),"& "ISCDATA[10](FPGMI,FVFYI)"; attributeBOUNDARY_CELLSofXC95144:entityis "BC_1"; attributeBOUNDARY_LENGTHofXC95144:entityis432; attributeBOUNDARY_REGISTERofXC95144:entityis "0(BC_1,*,internal,X),"& "1(BC_1,*,internal,X),"& "2(BC_1,*,internal,X),"& "3(BC_1,*,controlr,0),"& "4(BC_1,PB07_16,output3,X,3,0,Z),"& "5(BC_1,PB07_16,input,X),"& "6(BC_1,*,controlr,0),"& "7(BC_1,PB07_15,output3,X,6,0,Z),"& "8(BC_1,PB07_15,input,X),"& "9(BC_1,*,controlr,0),"& "10(BC_1,PB07_14,output3,X,9,0,Z),"& ...省略部分... endXC95144;

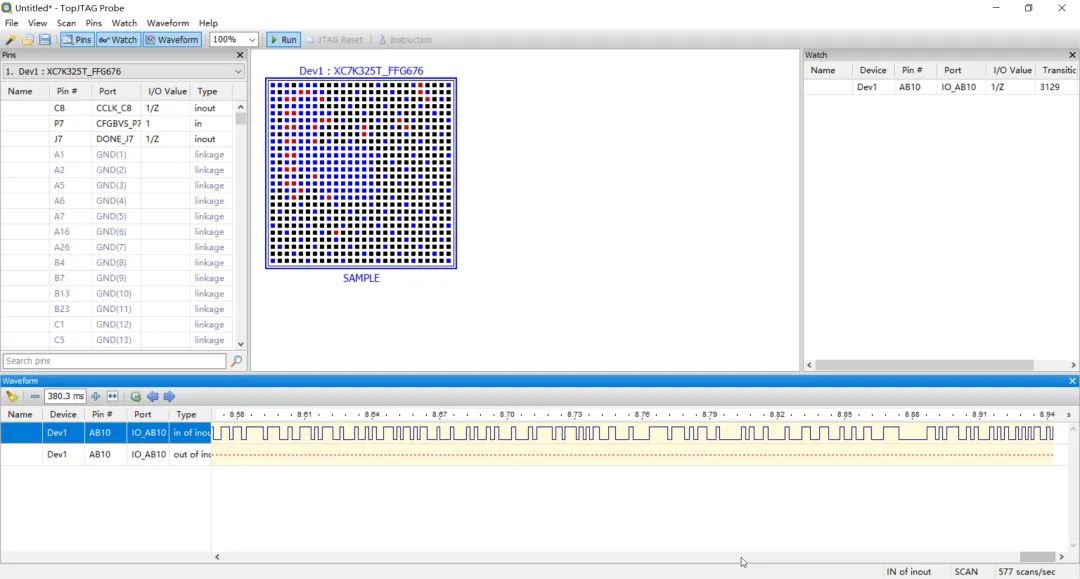

4. BSDL文件的应用

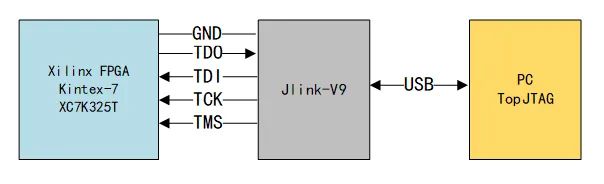

BSDL文件可以在一些边界扫描的软件中被使用,如XJTAG,TopJTAG等等,通过加载对应的BSDL文件可以实现对芯片外部所有管脚的读取和控制。具体使用方法,我会在后面的文章介绍。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

寄存器

+关注

关注

31文章

5336浏览量

120224 -

JTAG

+关注

关注

6文章

399浏览量

71673 -

vhdl

+关注

关注

30文章

817浏览量

128118

原文标题:强大的JTAG边界扫描2-BSDL文件

文章出处:【微信号:mcu149,微信公众号:电子电路开发学习】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

有没有办法使用JTAG提供LVDS信号的测量响应?

大家好,我试图在两个FPGA(Spartan 6)之间运行边界扫描互连测试。但是,某些信号有LVDS缓冲器。有没有办法使用JTAG提供LVDS信号的激励/测量响应?AR#6664规定必须将后配置

发表于 08-06 11:00

JTAG边界扫描技术设计方案

JTAG边界扫描技术设计方案

JTAG(Joint Test Action Group�联合测试行动小组)是一种国际标准测试协议IEEE 1149.1兼容),主要用于芯片内部测

发表于 03-04 14:40

•29次下载

基于JTAG边界扫描方式的重构控制器的设计

基于JTAG边界扫描方式的重构控制器的设计

引言

JTAG(联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),目前主要用于芯片内部测试。现在多数的

发表于 02-06 10:48

•1320次阅读

TMS320C5502 GZZ BSDL Model DSP边界扫描模型的详细概述

本文的主要内容概述的是TI的产品TMS320C5502 GZZ BSDL Model DSP边界扫描模型的详细资料

发表于 05-04 16:48

•12次下载

TMS320VC5507 GHH BSDL Model DSP边界扫描模型的详细资料概述

本文档的主要内容介绍的是TI的产品TMS320VC5507 GHH BSDL Model DSP的边界扫描模型的详细资料概述

发表于 05-04 16:58

•17次下载

TMS320C5515 ZCH BSDL Model DSP边界扫描模型的详细资料概述

本文档的主要内容介绍的是TI的产品TMS320C5515 ZCH BSDL Model DSP的边界扫描模型的详细资料概述

发表于 05-04 17:05

•12次下载

JTAG(四) 边界扫描测试技术

边界扫描测试技术 不属于 coresight架构,边界扫描测试技术 被 coresight 架构 使用.综述 联合测试行动组(Joint Test Action Group,简称

发表于 12-20 19:47

•20次下载

DS21Qx5y BSDL扫描链映射

本应用笔记介绍了四端口单芯片收发器(SCT)的JTAG硬件边界扫描功能。四端口器件的JTAG功能与四个以菊花链方式连接在一起的独立DS21x5y器件基本相同。DS21Q352、DS21

强大的JTAG边界扫描2-BSDL文件

强大的JTAG边界扫描2-BSDL文件

评论