随着薄膜晶体管液晶显示器的迅速发展,产品高分辨率、广视角、高响应速度 、 高开口率等需求对器件的显示质量提出了更高的要求。而伴随着像素尺寸变小, 线间距越来越小, 当信号线上有电流通过时,线间感应电场的千扰变得尤为突出,像素之间的合加剧,这些都会导致串扰现象的发生,大大影响了产品良率和显示效果。所以串扰对来说,是一个急需解决的重大问题

串扰的定义及分类

在薄膜晶体管液晶显示器中,人们将串扰定义为整个屏幕中某一区域的显示会受到另一区域的影响,而造成画面失真的一种显示异常的现象。但是由于人眼对显示屏幕不同亮度的敏感度不同,只有在某些灰阶背景下,串扰现象才能够较容易地观察出来。

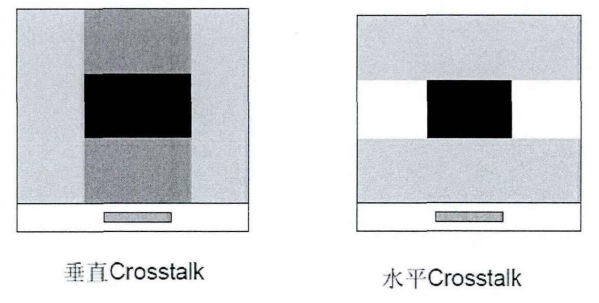

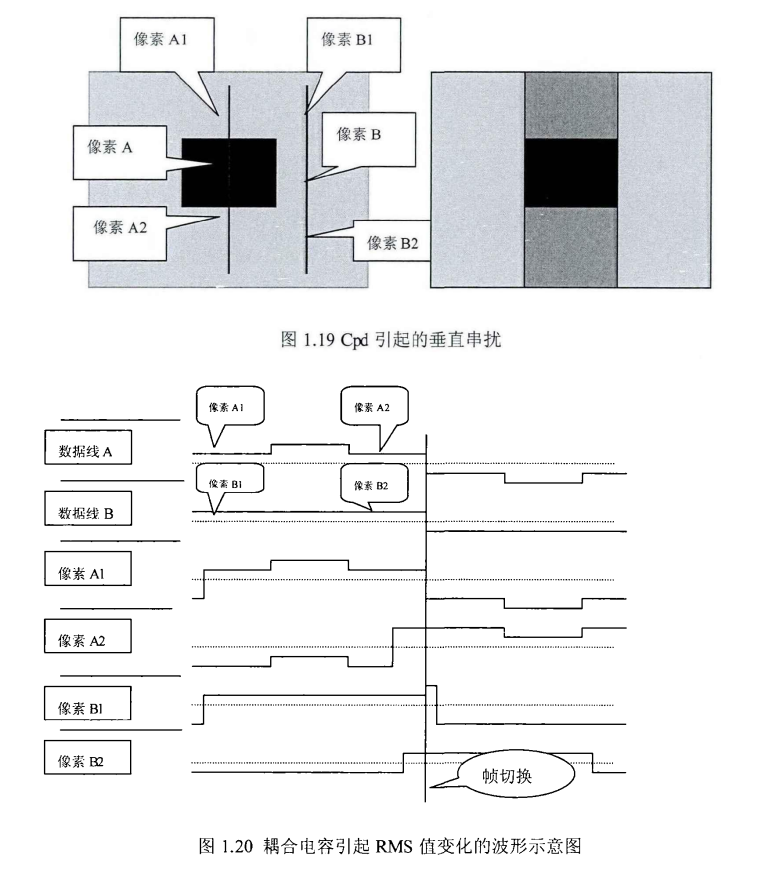

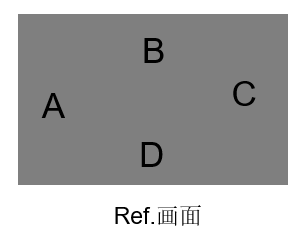

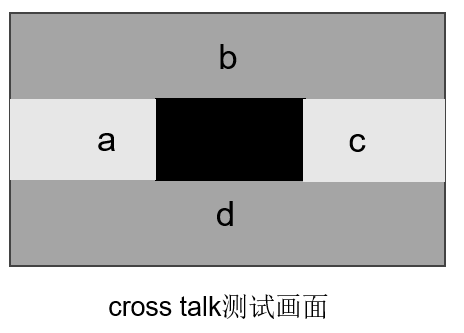

串扰常见的有两种分别称为垂直串扰和水平串扰。如下图所示,背景为46 灰阶,中间为黑色方块。黑色方块的周边区域根据位置可以分为上、下、左、右四个区域。当上、下区域受到黑色区域的影响而变的比背景更暗时,称为垂直串扰。同理,当左、右区域受到黑色区域的影响变的比背景更亮时,称为水平串扰。

(串扰比较容易发生在列反转、顿反转、com反转模式中,而在目前常用的点反转模式中出现较少)

水平串扰产生的原因

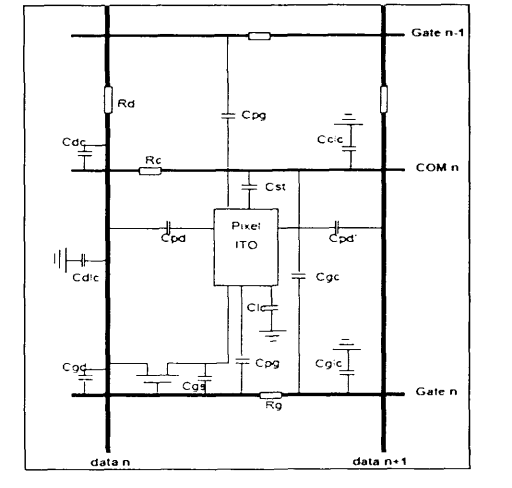

TFT面板在上板共电极与 TFT 面电容除了像素ITO与上板ITO电极形成的液晶电容以外,还有数据线和扫描线与上板电极形成的寄生电容,见下图。

上板共电极其实是一个 RC 延时很大的电阻-电容网络,当数据线电压变化时,便会经由数据线与上极板形成的寄生电容,影响到上极板共电极电位,由于上极板电阻很大,没办法短时间内消除电位变化的影响,恢复不到设定的电压,便会形成串扰。

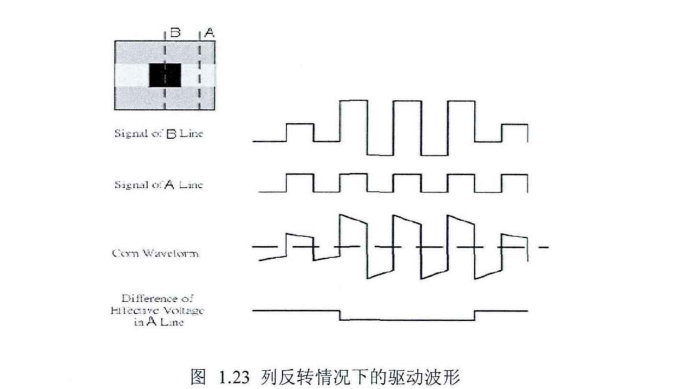

对列反转的情况下,如图 1.23。如果 A、B 两条信号加的电压不同,这时 B上的信号会通过 Com 电极合到A 信号线上,使得 A列的像素电压异常,不能显示正常灰阶,导致水平串扰。

垂直串扰产生的原因

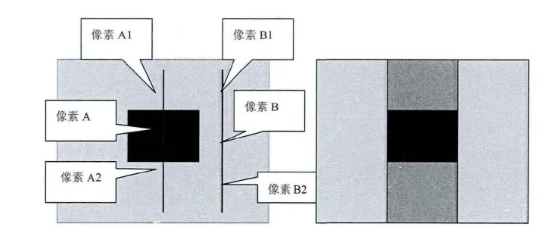

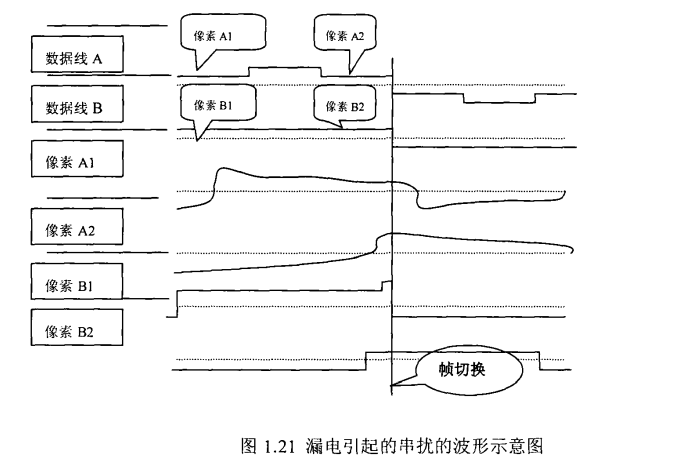

在共电极结构中,像素电极本身和下一条数据线间存在寄生电容,如下图所示。数据线上信号的变化会经由这些电容耦合到下一个数据线,引起下一个数据线上连接的子像素行成串扰。

在帧反转中,参考波形图 1.20,像素 A1 和A2与B1和 B2上的电压波形会有所差别。像素 B1、B2 显示的灰阶是相同的,但是 Vms 值比较会发现: A1会比B1的Vrms 值大,所以A1 会显示的灰阶比较深,而A2会比 B2的 Vms 值小,所以显示的灰阶值较浅。最终出现如图 1.19 的串扰。

Vrms 也称液晶的有效电压,液晶屏的透过率和相应时间都是与它直接相关的。

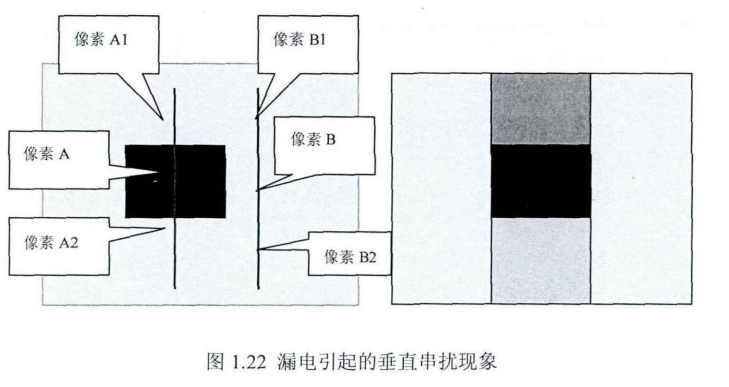

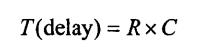

除了寄生电容能引起垂直串扰以外,还有一个因素也是不能忽略的,那就是漏电过大。不难想象,如果 TFT 漏电过大,加在存储电容上的电压会漏到信号线上而使存储中容的电压改变,但由于 A、B 两列信号线上加的电压不同,最后导致的像素电压 Vms 值也会不同,造成串扰现象,信号波形描述示意图如图 1.21

水平串扰的改善方法

水平串扰的主要原因是共电极的延迟,参考共电极延迟的计算公式可知,可以从减小共电极电阻及共电极耦合电容两方面来对水平串扰进行改善。

降低共电极的电阻,可以采用如下方法:

1.在布线空间允许情况下,将 Vcom ITO线宽做到最大

2增加Vcom ITO电极的膜厚;

3.采用具有更小Rs的透明材料取代ITO 材料,如IZO

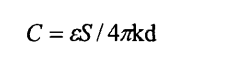

电容方面,已知平板电容的决定式为:

其中S为两板正对面积,ε为介电常数,k为静电常量,d为两极板之间的距离从该公式可知,减小电容需从减小交叠面积S和增大两极板距离d两方面进行。

垂直串扰的改善方法

造成垂直扰的主要因素是数据线对像素电极的合电容Cpd 以及像素 TFT 的漏电。因此,要改善垂直串扰,就需要找到数据线与像素电极之间的最佳距离,在不损失开口率的情况下降低数据线对像素电极的耦合影响;同时从TFT的开关特性出发,控制影响TFT 电的因素。

减小Cpd耦合电容:

(1)从设计上,需保证数据线与像素 ITO之间的距离为 6um 以上(其中包含了 2.5m 的工艺波动),对 IPS型TFT-LCD,还需让 Vcom ITO到数据线的距离在 3.5um 以上(其中包含了25um的工艺波动)。而针对不同的生产线,设计人员需要综合考虑所在产线的工艺波动、S/D 及 ITO线宽和位置的波动,从而敲定这两个距离的大小。

然而,随着分辨率和开口率的提高,且显示屏的边框越来越窄,设计时无法给数据线和像素ITO之间留出足够的距离,因此需考虑能够更好地屏蔽数据线对像素ITO电场干扰的方法。

对于IPS 型TFT-LCD,可以在 S/D 层上增加一层树脂(Resin)层,该 Resin 层同样可以起到屏蔽数据线电场干扰的作用。另外,也可以在扫描线下方增加一条Vcom金属线,该层金属与扫描线为同一层,并与TFT基板上的VcomITO导通。像素ITO 与该 Vcom 金属有交叠,因此可以形成存储电容 Cst。这样将Cst进一步增大,降低合电容 Cpd在总电容 Cta中的比例,减小因 Cpd而造成的影响,从而规避串扰不良的产生。

减小漏电流:

(1)在设计上,需要减小有源层面积,使其被包裹在栅极基台内,避免受到光照和温度的影响。将栅极关断电压设置在-10.5V 左右。另外也可以采用双有源层结构、双栅结构来提高 TFT 的关态特性。

(2)在工艺上,可以减小有源层厚度来优化 TFT 关态特性,同时也必须提高对位精度,严格管控有源层在工艺上的偏移。

串扰的计算方法

Cross talk计算公式:MAX(abs((A-a)/A);abs((B-b)/B);abs((C-c)/C);abs((D-d)/D))

选取最大值为最终测试结果。

注:Abs为绝对值函数。

审核编辑:刘清

-

lcd

+关注

关注

34文章

4466浏览量

168951 -

TFT

+关注

关注

10文章

386浏览量

111533 -

寄生电容

+关注

关注

1文章

294浏览量

19420 -

薄膜晶体管

+关注

关注

1文章

29浏览量

9831 -

VMs

+关注

关注

0文章

5浏览量

5251

原文标题:LCD串扰(Crosstalk)基础知识

文章出处:【微信号:心植桂冠,微信公众号:心植桂冠】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

LCD串扰的定义及分类 垂直串扰产生的原因有哪些

LCD串扰的定义及分类 垂直串扰产生的原因有哪些

评论