本篇文章将讲述如何在Cadence IC中使用ADE GXL对电路进行优化设计。

按照惯例,首先讲述一下大致的操作流程:

详细步骤

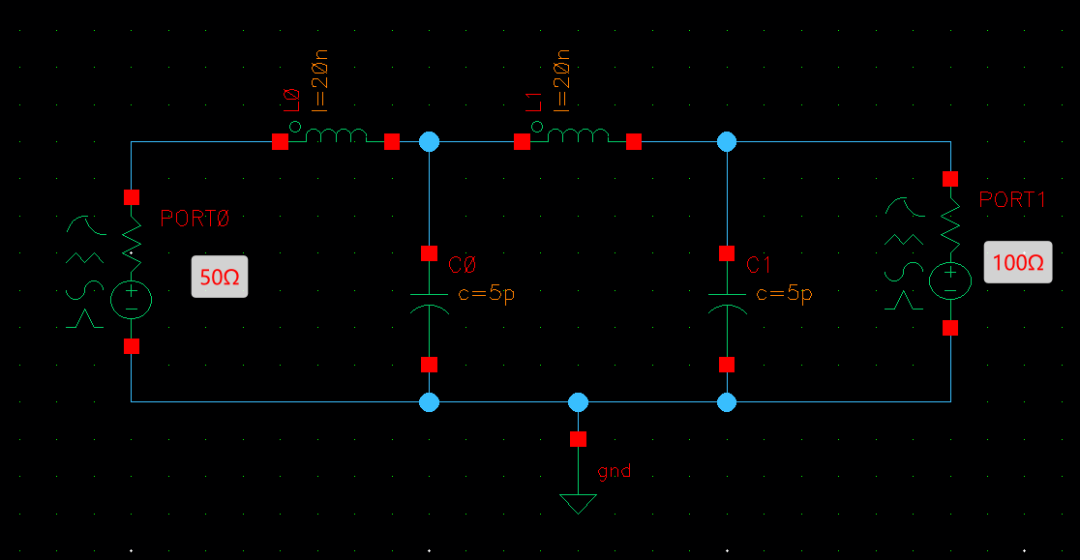

这次优化的例子是一个阻抗匹配电路,50Ω到100Ω,用电感和电容网络进行匹配。

使用analogLib中的元件搭建电路图,两个PORT的阻抗分别设置为50Ω和100Ω,匹配网络的具体参数如下:

初始电路(未匹配)

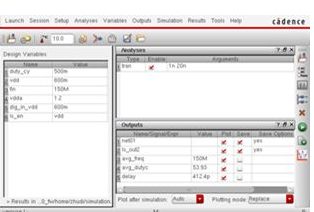

运行仿真(Launch>ADE L),运行S参数仿真,频率为100M-500M,仅查看S11参数,设置如下(注意保存仿真设置):

仿真设置

运行仿真后发现S11在部分范围大于-10dB,说明匹配效果不好(这里以小于-10dB表示匹配良好),需要修改参数。

初始电路仿真后的S11

要对电路进行优化,在原理图编辑窗口中打开ADE GXL。

打开ADE GXL

打开后显示欢迎界面,在Outputs处点击链接以打开Outputs Setup标签。之后添加Tests。

添加Tests

在ADE L窗口中加载刚才保存的仿真设置,Outputs Setup标签自动添加优化目标参数。

添加优化目标参数

接下来需要设置优化目标参数的目标值,在Details栏中修改刚刚导入的目标参数为ymax(db(spm('sp 1 1))),这是因为目标参数不能是波形,必须是点,所以修改为S11的最大值,在spec栏中选择<-10,Weight表示权重,这里填写1.这些设置表示优化目标是 S11的最大值小于-10dB。

设置优化目标

通过上图所示标号4添加要优化的元件参数。

创建参数

设置参数的范围

修改参数的范围

选择Global Optimization,设置参考态。对电路进行优化需要设置一个参考态,目的是给优化提供一个起始状态。

设置参考态

点击绿色按钮运行优化,当达到要求后会自动停止。

优化完成

可以右击某一参数点击Backannotate将参数值返回到原理图。

优化后的电路

对优化后的电路进行仿真,发现达到要求(在目标频段内均小于-10dB)。

最终仿真结果

说明:

- 本例子在Cadence IC618上完成,不同版本可能有差异。

- 电路优化过程相比ADS比较慢。

-

IC

+关注

关注

36文章

5953浏览量

175653 -

电路设计

+关注

关注

6676文章

2453浏览量

204441 -

Cadence

+关注

关注

65文章

923浏览量

142175 -

仿真

+关注

关注

50文章

4087浏览量

133642 -

ade

+关注

关注

0文章

29浏览量

15458

发布评论请先 登录

相关推荐

ALLEGRO PCB SI GXL

基于Cadence的IC设计

ADE7752/ADE7752A具有脉冲输出的多相电能计量ic

ADE7854/ADE7858/ADE7868/ADE7878:集成谐波和基波信息的多相多功能电能计量IC

ADE5166/ADE5169/ADE5566/ADE5569:带8052 MCU、RTC和LCD驱动器数据表的单相电能测量IC

ADE7854A/ADE7858A/ADE7868A/ADE7878A:多相多功能电能计量IC数据表

UG-545:评估ADE7854A/ADE7858A/ADE7868A/ADE7878A电能计量IC

在Cadence IC中使用ADE GXL优化电路设计

在Cadence IC中使用ADE GXL优化电路设计

评论