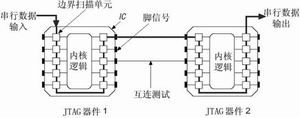

前面几篇文章,介绍了关于JTAG边界扫描的一些基础知识和常用的调试软件。

强大的JTAG边界扫描1-基本原理

强大的JTAG边界扫描2-BSDL文件

强大的JTAG边界扫描3-常用边界扫描测试软件

今天我们来演示基于STM32+Jlink的边界扫描实际应用。

试想这样一个场景,我们新设计了一款集成了很多芯片的板卡,包括BGA封装的微控制器,如FPGA/MCU,还有LED、按键、串口、传感器、ADC等基本外设。

我们需要测试一下硬件电路工作是否正常、焊接是否良好,通常我们会写个测试代码,比如控制LED闪烁,读取按键的输入,串口收发一些数据,然后把程序烧录进去,看看现象是否和我们设计的一致。

当现象和设计不一致时,是代码设计的问题、还是硬件原理的问题、又或者是焊接的问题呢?应该如何一一排除呢?

这里就可以使用JTAG边界扫描的测试方法,来验证到底是哪里出的问题,因为JTAG边界扫描不需要写任何代码,只需要一个BSDL文件,就可以控制和读取芯片的任意管脚。

下面我们以意法半导体 MCU STM32F103为例,配合JLink,演示JTAG边界扫描的应用。

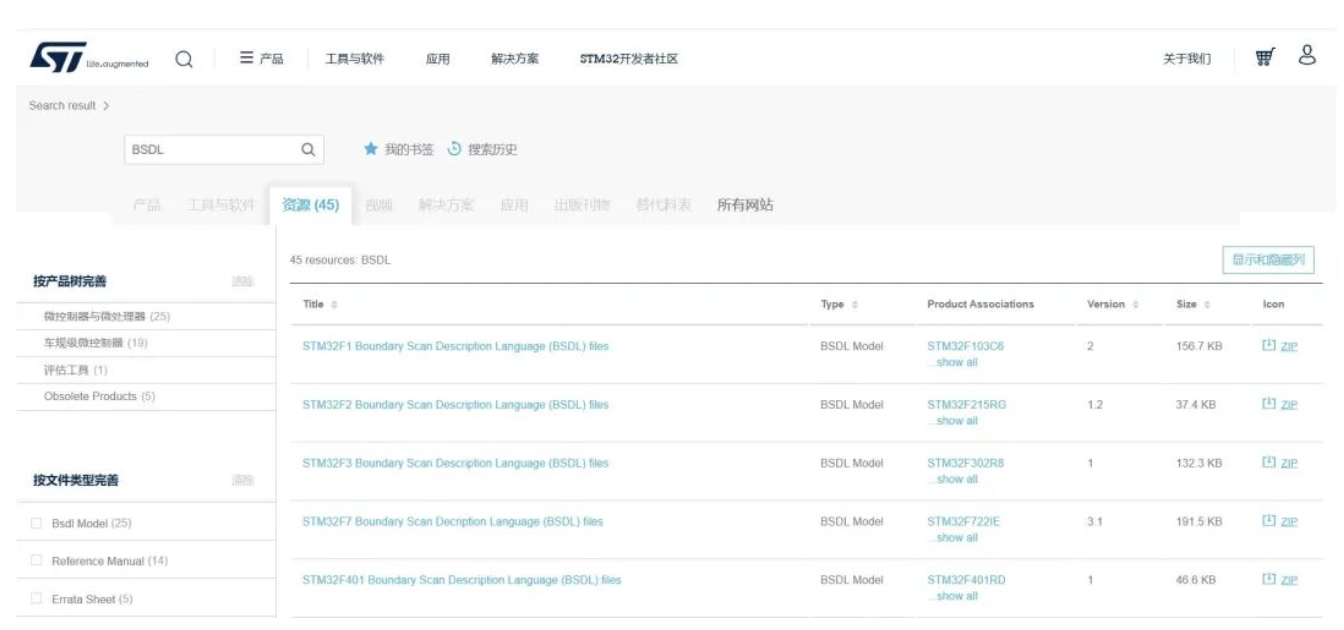

1. 获取芯片的BSDL文件

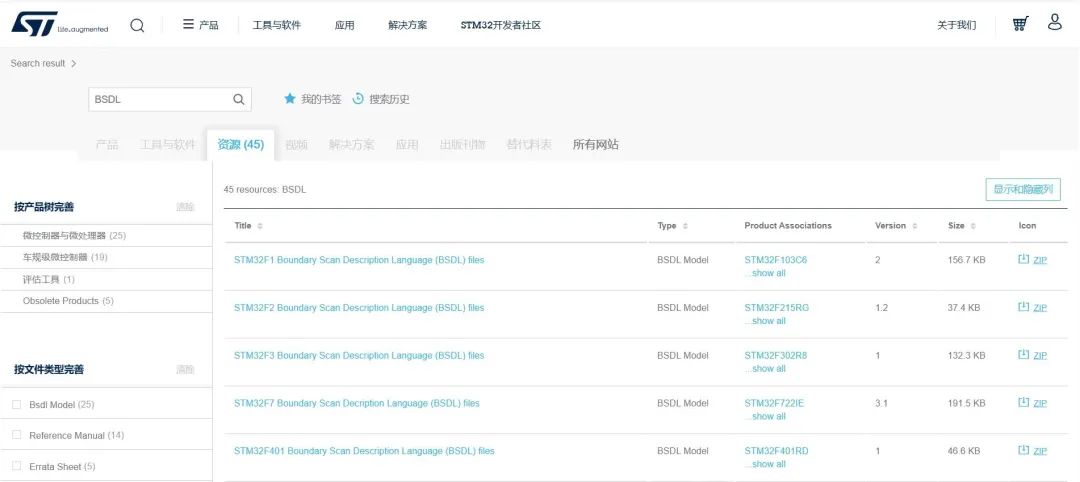

获取意法半导体MCU的BSDL文件,可以到官方网站搜索BSDL,就会弹出对应系列的BSDL文件包。

STM32F1系列BSDL文件的下载地址:

下载到本地之后解压,可以看到很多BSDL文件,我们开发板上的芯片型号是STM32F103ZET6-LQFP144,属于大容量芯片,所以BSDL文件对应的是:

STM32F1_High_density_LQFP144.bsd 关于其他芯片的BSDL文件获取方式,可以参考之前的文章:强大的JTAG边界扫描(2):BSDL文件介绍

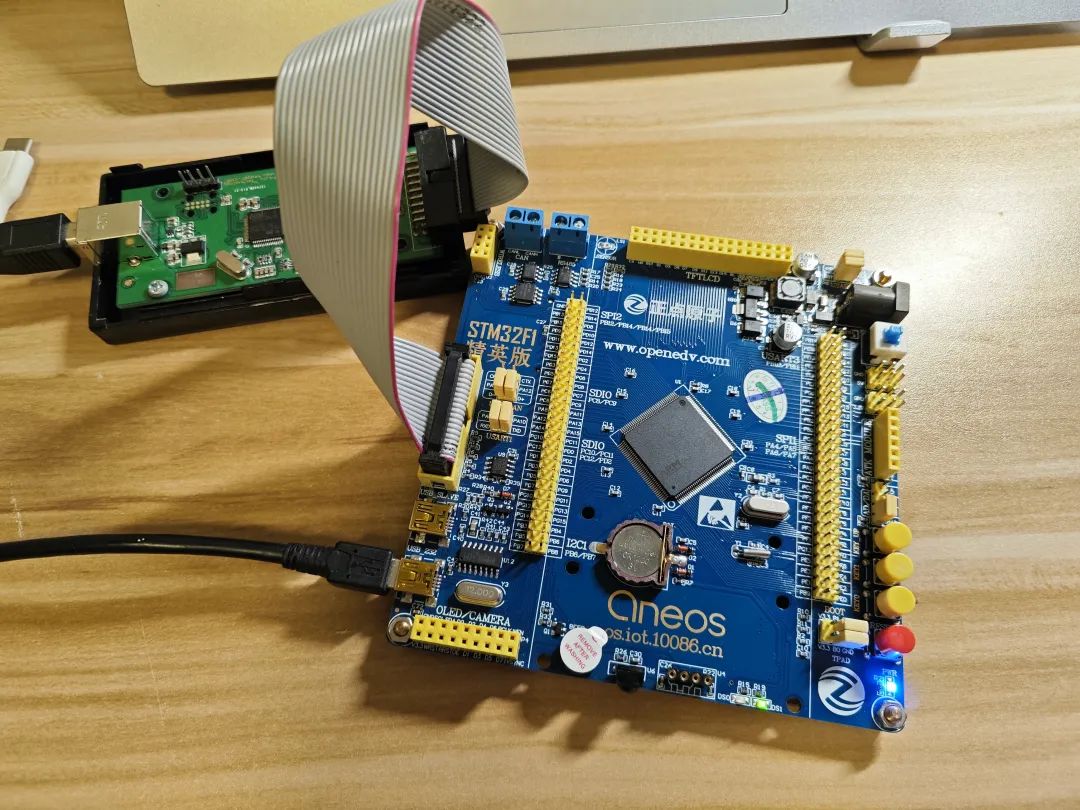

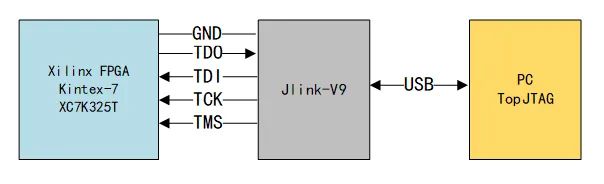

2. 硬件连接

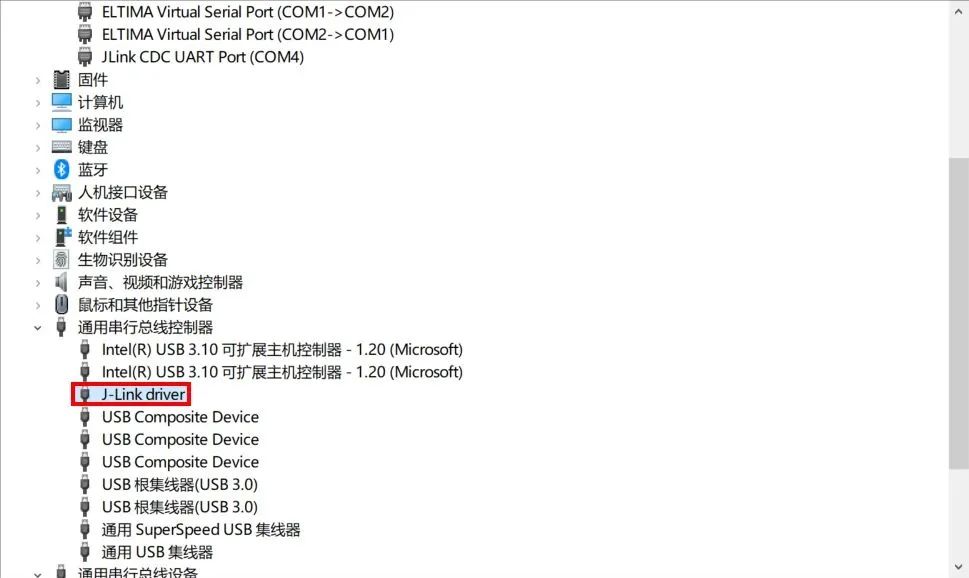

按照下图所示,使用排线连接JLink和开发板的JTAG接口。  hw 并确保设备管理器里JLink驱动被正确识别。

hw 并确保设备管理器里JLink驱动被正确识别。

3. 边界扫描测试

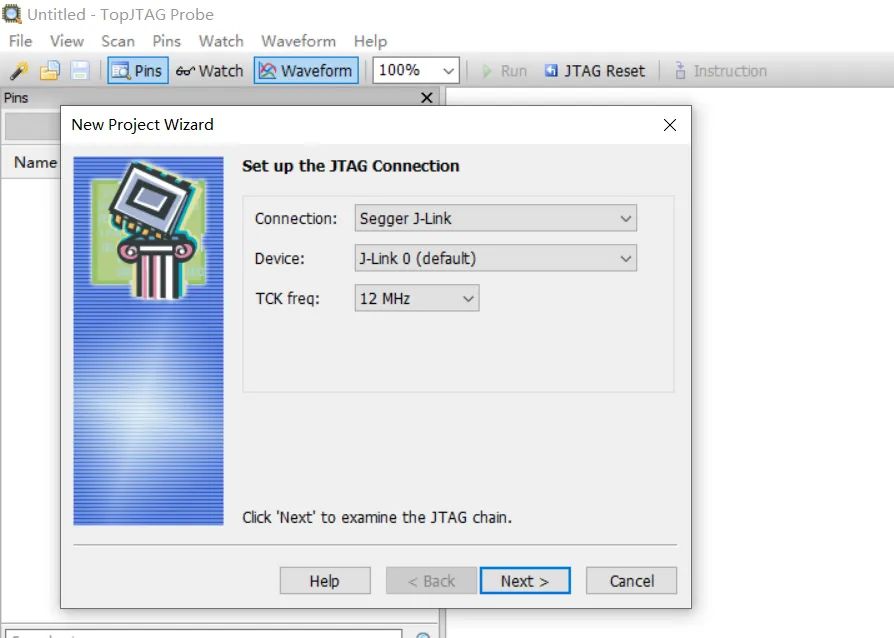

关于TopJTAG边界扫描测试软件的介绍和基本使用,可以参考之前的文章:强大的JTAG边界扫描(3):常用边界扫描测试软件 打开TopJTAG Probe软件之后,先创建一个工程,并选择JTAG设备类型,这里我们使用的是JLink。

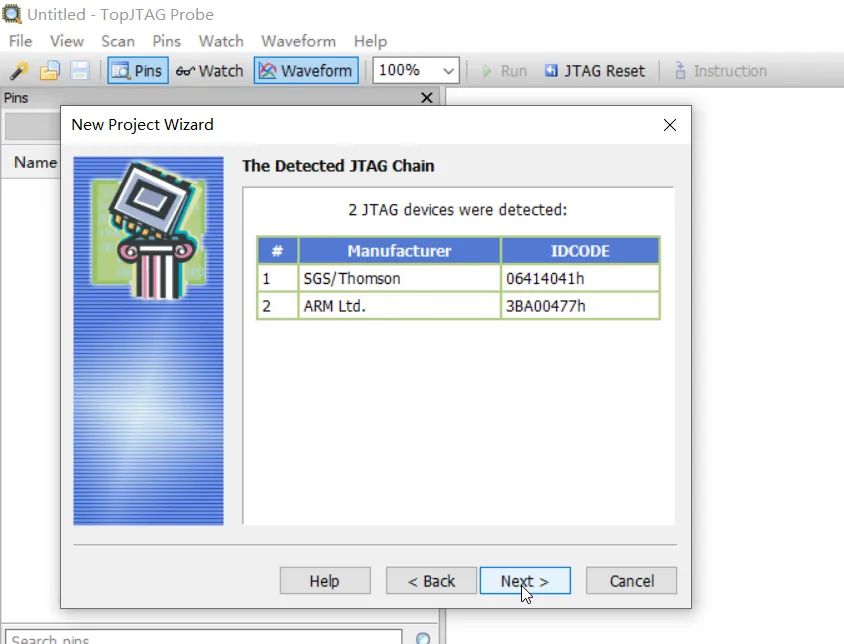

如果硬件连接正确,驱动安装正常,软件会自动识别到连接的芯片。

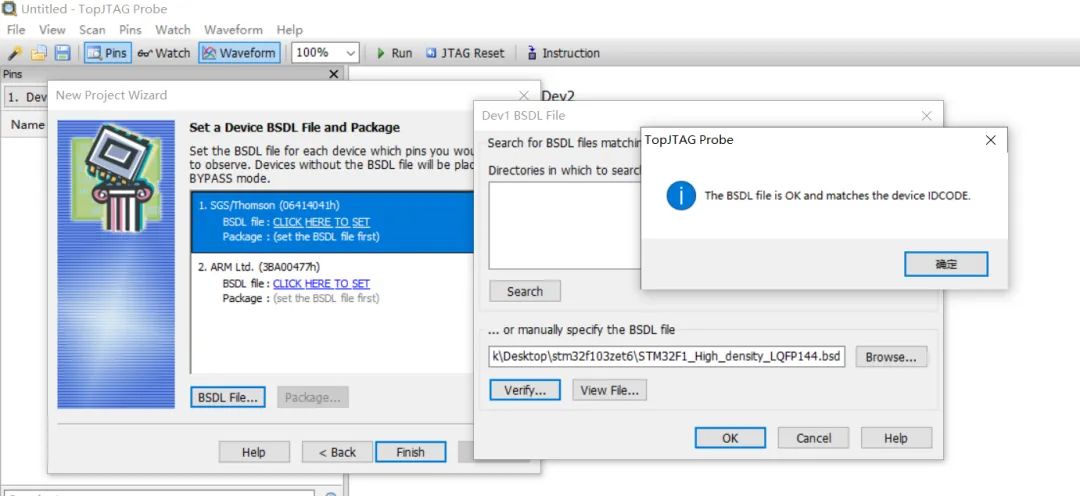

指定芯片所对应的BSDL文件,这里我们选择上一步下载的STM32F1_High_density_LQFP144.bsd文件,并进行IDCODE校验。

如果IDCODE不匹配,说明选择的BSDL文件错误,之后就进入到边界扫描测试界面了。

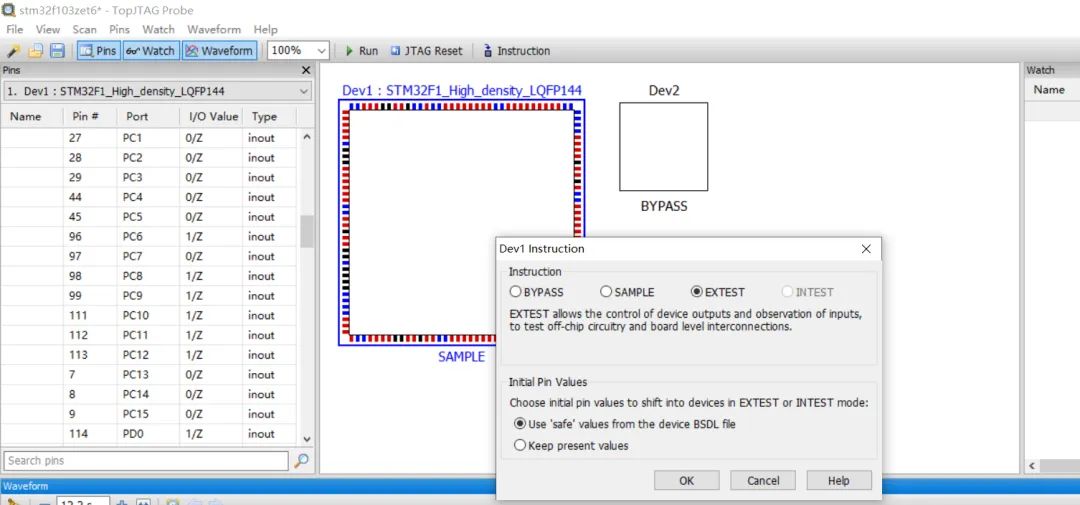

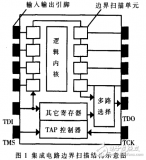

点击Instruction按钮,可以选择三种测试命令:

BYPASS:旁路掉当前器件,在菊花链拓扑方式时,跳过当前器件

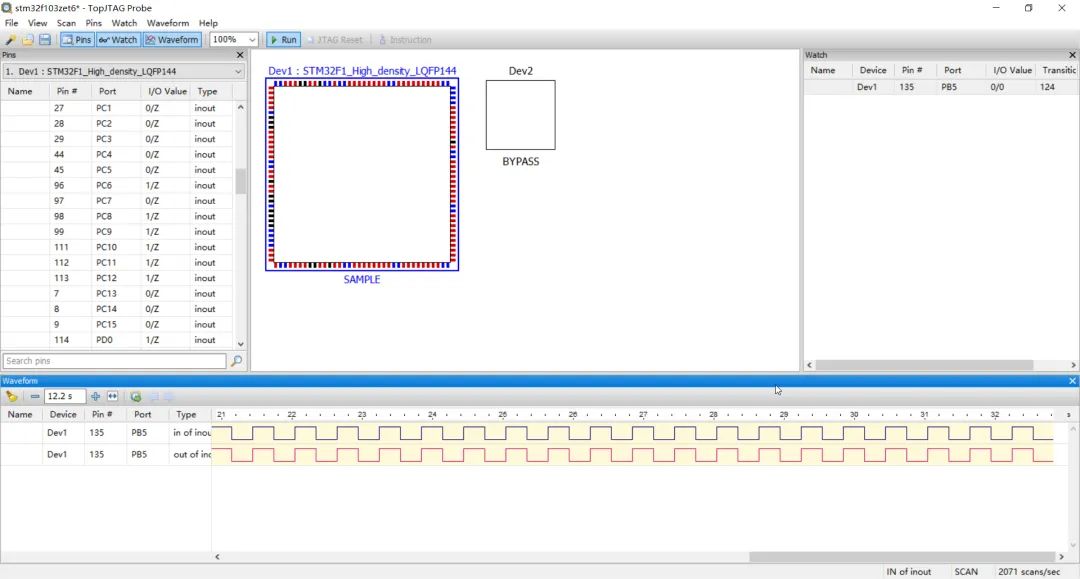

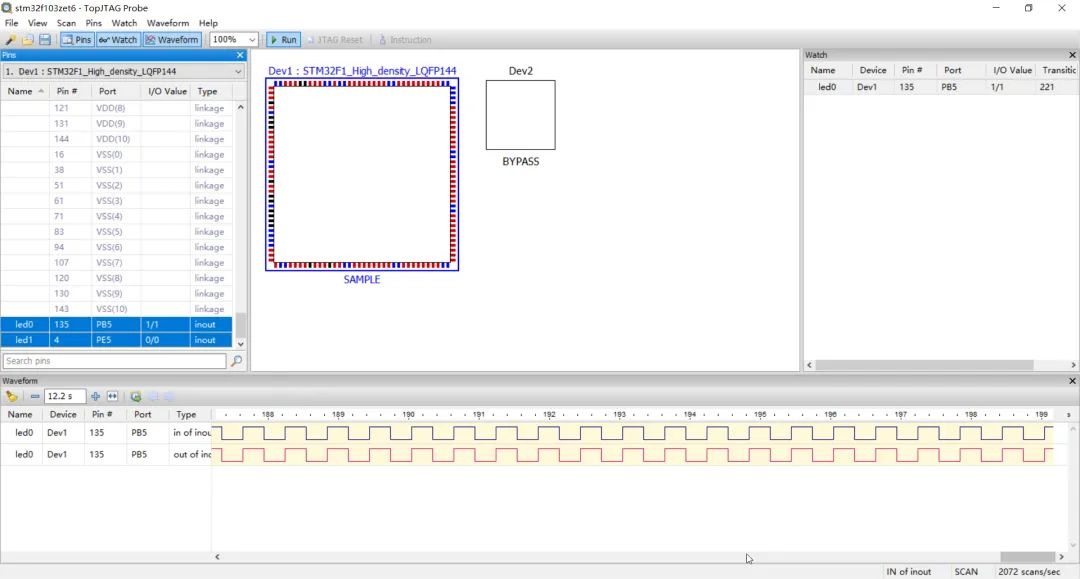

SAMPLE:采样模式,可以对所有管脚的状态进行读取,可以统计电平翻转的次数,或者以波形方式显示实时状态

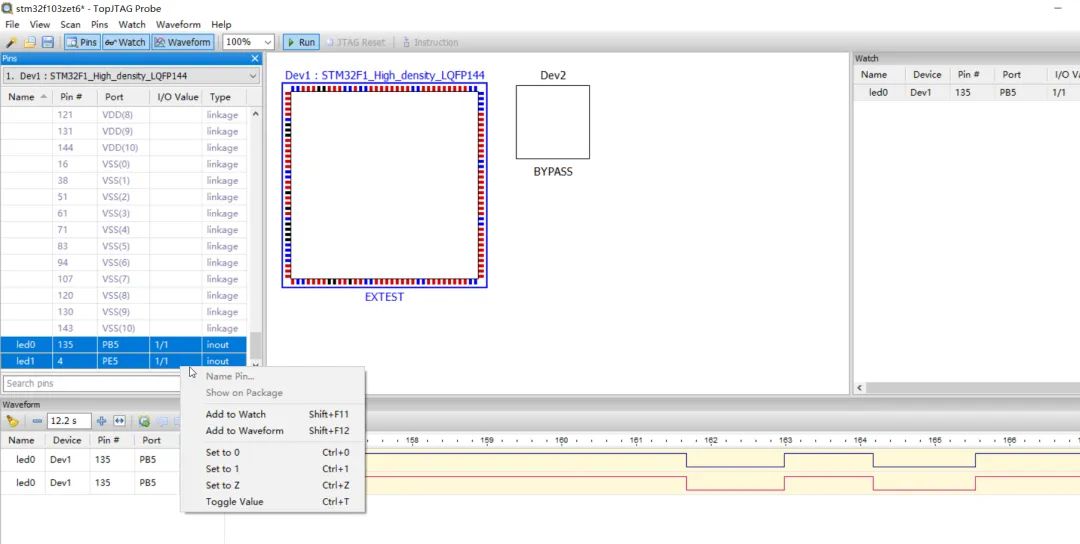

EXTEST:可以任意的控制所有外部管脚的状态,可手动指定为高低电平,高阻态。

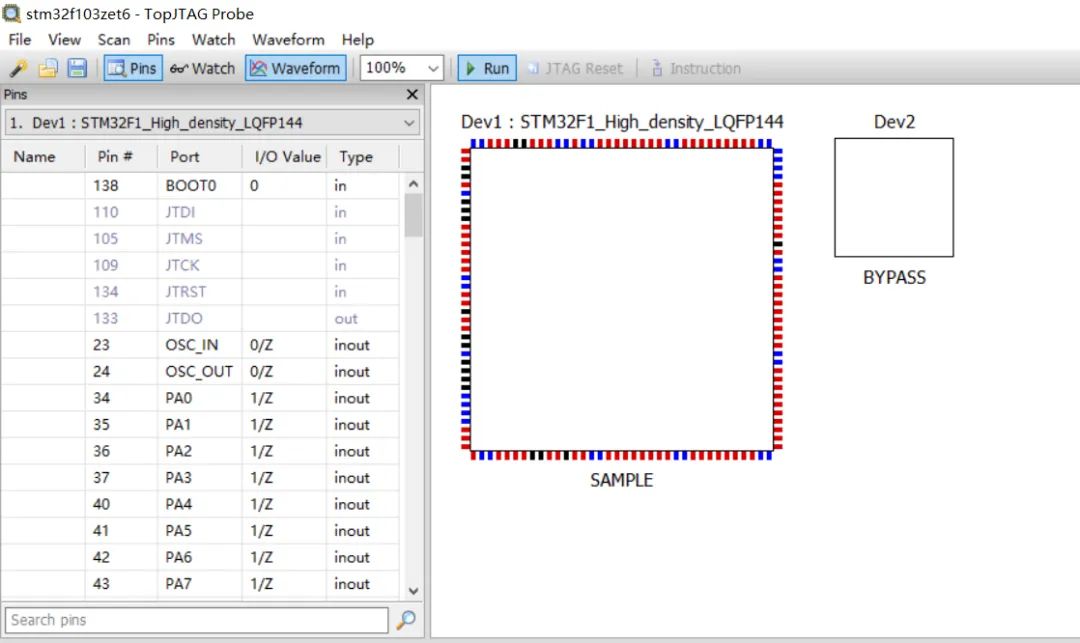

这里我们选择SAMPLE模式,点击RUN按钮,可以看到芯片所有的管脚实时状态,

在Pins窗口,可以看到所有管脚的实时状态,选中一个管脚,可以把它添加到Watch窗口,或者Waveform窗口。 切换到EXTEST模式,可以手动设置管脚的高低电平或高阻状态。

Watch窗口信号的还原能力,完全取决于JTAG_TCK的频率,即管脚信号的采样时钟。

4. 总结

通过边界扫描可以快速的判断文章开头提到的几个问题,如果使用边界扫描的方式,发现读取和控制管脚的状态不对,那么可以判定是焊接的问题,通过编程,甚至可以按照一定的时序来控制管脚的状态,从而达到控制外部器件的目的。

总之,边界扫描是一种非常实用的测试方法,在电路板生产制造、芯片设计、芯片封测等方面都有很广泛的应用。

审核编辑:汤梓红

-

mcu

+关注

关注

146文章

17458浏览量

354428 -

STM32

+关注

关注

2276文章

10947浏览量

359146 -

意法半导体

+关注

关注

31文章

3186浏览量

109180 -

边界扫描

+关注

关注

1文章

32浏览量

15066 -

Jlink

+关注

关注

6文章

111浏览量

38002

原文标题:强大的JTAG边界扫描4-STM32边界扫描应用

文章出处:【微信号:mcu149,微信公众号:电子电路开发学习】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于STM32+Jlink的边界扫描实际应用演示

边界扫描测试技术介绍

如何通过边界扫描测试进行差分信号测试?

有没有免费的工具可用于STM32F4进行边界扫描测试?

VXI边界扫描模块接口电路的设计

边界扫描与电路板测试技术

简述BSDL边界扫描语言,BSDL边界扫描语言的应用

边界扫描测试的基本原理及其测试系统的设计

边界扫描技术的详细资料描述

JTAG(四) 边界扫描测试技术

基于STM32+Jlink的边界扫描实际应用

基于STM32+Jlink的边界扫描实际应用

评论