引言

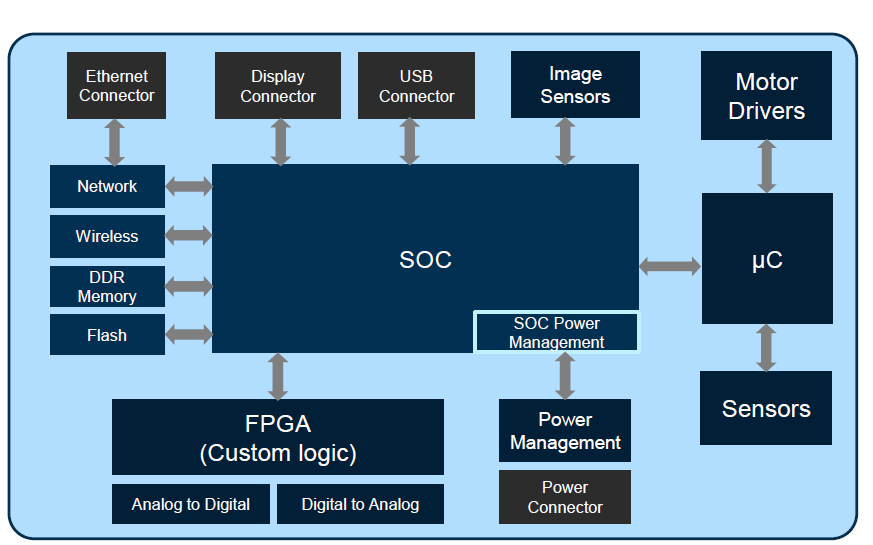

在系统芯片(SoC)设计中, DDR模块是一种重要的组成部分。它不仅在提高系统性能方面起着关键作用,还对于优化系统功耗管理具有重要意义。本文将详细介绍DDR模块在SoC设计中的应用,包括其定义、作用、设计原则和注意事项。

DDR模块的定义与作用

DDR(Double Data Rate)模块是一种高速缓存存储器,它通过在时钟的上升和下降沿读取和写入数据,从而实现更高的数据传输速率。在SoC设计中,DDR模块主要作为外部存储器接口,连接CPU和其他组件,以提供大容量、高速的数据存储和访问能力。

DDR模块的作用主要包括以下几点:

提高系统性能:DDR模块能够提供比传统静态随机存取存储器(SRAM)更高的数据传输速率,从而加快了数据访问的速度,提高了系统的响应速度和整体性能。

优化系统功耗管理:DDR模块的功耗相对较低,通过使用DDR模块作为外部存储器,可以降低整个系统的功耗。

扩展系统容量:DDR模块具有更高的存储密度,可以在有限的物理空间内提供更大的存储容量,满足系统对数据存储的需求。

DDR模块的设计原则

在SoC设计中,DDR模块的设计需要遵循以下原则:

单通道与双通道:DDR模块既可以使用单通道模式,也可以使用双通道模式。在单通道模式下,数据在每个时钟周期传输一次;而在双通道模式下,数据在每个时钟周期传输两次。因此,双通道模式能够提供更高的数据传输速率。但是,双通道模式需要更多的功耗和硬件资源,因此在设计时应根据实际需求进行选择。

像素分配:在针对图像和视频处理应用的SoC设计中,DDR模块应支持像素分配(Pixel Dump)模式。这种模式下,多个像素值可以打包成一个数据块进行传输,从而提高了数据传输的效率。

内存带宽:在设计DDR模块时,需要考虑内存带宽的分配。如果内存带宽不足,将导致数据传输延迟,影响系统的整体性能。因此,需要根据系统需求和各个组件的优先级来合理分配内存带宽。

注意事项

在设计DDR模块时,还需要注意以下问题:

寄存器的选取:在DDR模块中,需要使用寄存器来存储配置参数和状态信息。因此,寄存器的选取对于DDR模块的性能和稳定性至关重要。应选取具有快速响应速度和低功耗的寄存器,以确保DDR模块的正常运行。

输入输出映射方式:DDR模块具有多种输入输出映射方式,包括位交织(Bit Interleaved)、字节交织(Byte Interleaved)等。不同的映射方式会影响数据传输的效率,因此在设计时应根据实际需求选择合适的映射方式。

时序要求:DDR模块对时序要求非常严格,需要保证数据在规定的时间内传输完成。如果时序不满足要求,可能会导致数据传输错误,甚至损坏DDR模块。因此,在设计中需要仔细考虑时序问题,确保各个组件之间的数据传输时序配合得当。

ECC校验:为了提高系统的可靠性,DDR模块通常支持错误检测与纠正(ECC)功能。通过使用ECC校验,可以检测并纠正存储在DDR模块中的数据错误,保证数据的完整性和准确性。在设计时,需要根据实际应用需求来确定是否需要使用ECC校验功能。

电源管理:DDR模块的电源管理也是设计中需要考虑的重要问题。为了优化系统性能和功耗,需要仔细规划DDR模块的电源分布和电压降分配。此外,还需要考虑电源噪声对DDR模块性能的影响,并采取相应的措施来抑制噪声干扰。

审核编辑:刘清

-

寄存器

+关注

关注

31文章

5618浏览量

130386 -

电源管理

+关注

关注

117文章

8505浏览量

148226 -

DDR

+关注

关注

11文章

761浏览量

69532 -

SoC设计

+关注

关注

1文章

151浏览量

19598 -

SRAM存储器

+关注

关注

0文章

89浏览量

17692

原文标题:soc 设计中的 DDR 模块

文章出处:【微信号:快乐的芯片工程师,微信公众号:快乐的芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

DDR200T中DDR的使用与时序介绍

Rockchip SoC上的图像信号处理模块基本知识介绍

DDR SDRAM控制器的设计与实现

PI2DDR3212和PI3DDR4212在DDR3/DDR4中应用

外设SPI在SOC设计中的应用

DDR Inline ECC在Jacinto7 SoC中的应用

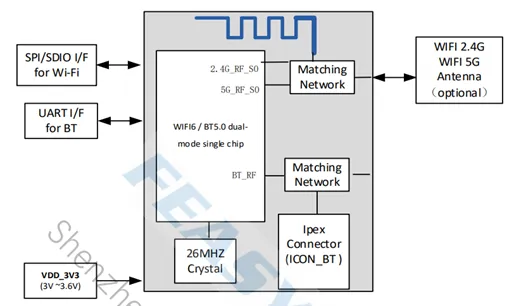

WIFI6 SOC模块介绍解析

详细介绍DDR模块在SoC设计中的应用

详细介绍DDR模块在SoC设计中的应用

评论