为实用的软件系统编写状态机并不是一件十分轻松的事情,特别是当状态机本身比较复杂的时候尤其如此,许多有过类似经历的程序员往往将其形容为“毫无创意”的过程,因为他们需要将大量的时间与精力倾注在如何管理好状态机中的各种状态上,而不是程序本身的运行逻辑。

作为一种通用的软件设计模式,各种软件系统的状态机之间肯定会或多或少地存在着一些共性,因此人们开始尝试开发一些工具来自动生成有限状态机的框架代码,而在Linux下就有一个挺不错的选择──FSME(FiniteState Machine Editor)。

可视化的FSME

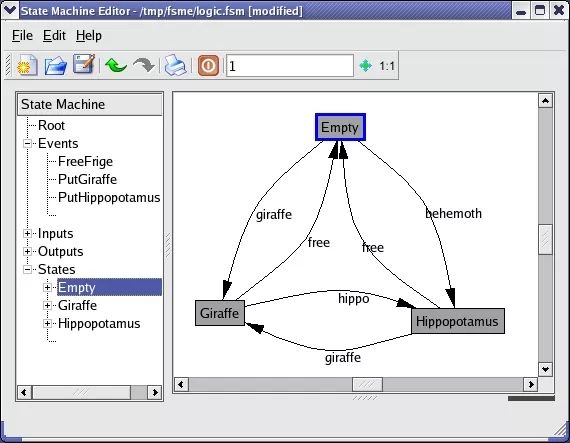

FSME是一个基于Qt的有限状态机工具,它能够让用户通过图形化的方式来对程序中所需要的状态机进行建模,并且还能够自动生成用C++或者Python实现的状态机框架代码。

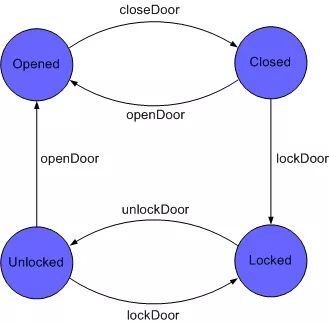

控制城门的状态机

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

软件

+关注

关注

69文章

4958浏览量

87624 -

状态机

+关注

关注

2文章

492浏览量

27556

发布评论请先 登录

相关推荐

Simulink中的状态机建模方法 Simulink数据可视化与分析功能

1. Simulink中的状态机建模方法 1.1 理解状态机的基本概念 在开始建模之前,了解状态机的基本概念是必要的。状态机由以下几个部分组成: 状

生成式AI工具作用

生成式AI工具是指那些能够自动生成文本、图像、音频、视频等多种类型数据的人工智能技术。在此,petacloud.ai小编为您整理生成式AI

如何在FPGA中实现状态机

在FPGA(现场可编程门阵列)中实现状态机是一种常见的做法,用于控制复杂的数字系统行为。状态机能够根据当前的输入和系统状态,决定下一步的动作和新的状态。这里,我们将详细探讨如何在FPG

关于SMU状态机的问题求解

我有一些关于 SMU 状态机的问题。

假设由于某种原因,SMU 已进入故障状态。 手册指出,要返回运行状态并将 FSP 恢复到无故障状态,应调用IfxSmu_releaseFSP()。

发表于 05-29 08:18

请问STM32F051用了操作系统RTX后还需要写状态机不?

现在学会了rtx操作系统后,原来用状态机的学的程序,可不可以不切割,直接单线程来执行列?各位前前辈指点一下。多谢!

发表于 05-08 06:11

在Verilog中实现Moore型和Mealy型状态机的方法简析

编写能够被综合工具识别的状态机,首先需要理解状态机的基本概念和分类。状态机(FSM)是表示有限个状态以及在这些

嵌入式编程,如何用 C 语言实现状态机设计?

方为一组输入,状态机应做出如下反应:

当某个状态遇到不能识别的输入时,就默认进入陷阱状态,在陷阱状态中,不论遇到怎样的输入都不能跳出。

为了表达上面这个

发表于 04-23 11:00

什么是有限状态机?如何解决传统有限状态机「状态爆炸」问题?

有限状态机(Finite State Machine,简称FSM)是一种用来进行对象行为建模的工具,其作用主要是描述对象在它的生命周期内所经历的状态序列以及如何响应来自外界的各种事件。

Verilog状态机+设计实例

在verilog中状态机的一种很常用的逻辑结构,学习和理解状态机的运行规律能够帮助我们更好地书写代码,同时作为一种思想方法,在别的代码设计中也会有所帮助。 一、简介 在使用过程中我们常说

单片机代码自动生成器程序

单片机代码自动生成器是一种能够帮助开发人员快速生成单片机代码的工具。它利用了现代计算机技术和算法,能够根据用户提供的输入和需求,

状态机自动生成工具FSME

状态机自动生成工具FSME

评论