Hardware Mailbox

硬件邮箱主要用于提供具有小的 32 位有效负载的中断事件通知。

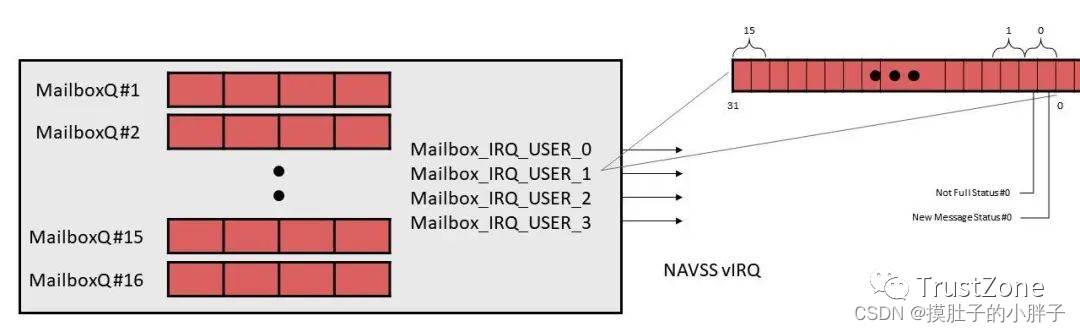

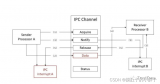

VRING 使用硬件邮箱在目标 CPU 上触发中断。每个邮箱包含 16 个单向 HW 队列,最多可连接 4 个通信用户或 CPU。

J721E SoC 有 12 个硬件邮箱实例。即 12x 16 个硬件邮箱队列。

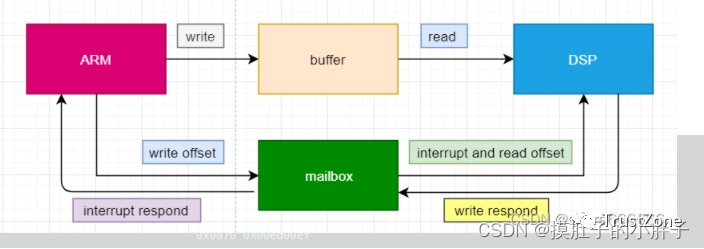

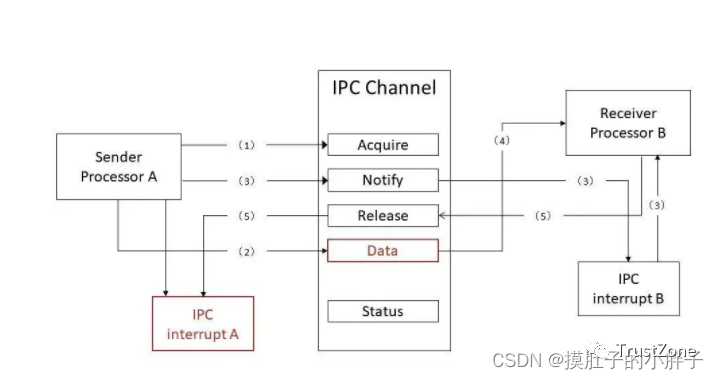

(硬件邮箱的逻辑框图)

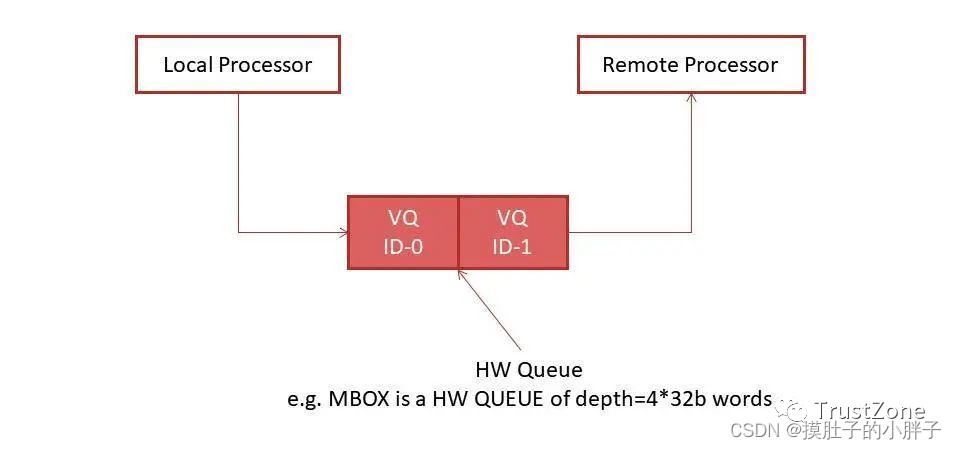

(硬件邮箱的逻辑框图)

Mailbox and VRING

邮箱本质上充当一个非常小的硬件队列,其中包含 VRING ID。

VRING 是共享内存中的 SW 队列,保存两个 CPU 之间传递的实际消息。当收到中断时,邮箱消息会告知从哪个 VRING 出列消息。

VRING ID=0 tells to look at the VRING from sender to receiverVRING ID=1 tells to look at the VRING from receiver to sender

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

cpu

+关注

关注

68文章

10868浏览量

211849 -

通信

+关注

关注

18文章

6034浏览量

136009 -

soc

+关注

关注

38文章

4169浏览量

218318 -

硬件

+关注

关注

11文章

3337浏览量

66234

发布评论请先 登录

相关推荐

SoC的核间通信机制—mailbox介绍

目前很多芯片都会有几个core核,有的是Cortex M0+、M4、M7、A53、A73等等,有的有着2核、3核、4核甚至6核8

发表于 08-11 10:51

•5781次阅读

开放核协议:IP核在SoC设计中的接口技术

的SoC 设计使芯片的设计从以硬件为中心转向以软件为中心,芯片设计不再是门级的设计,而是IP核和接口及其复用设计。IP核集成到系统所要考虑的问题包括:同步,例如全局执行、数据交换和协议

发表于 12-11 11:07

基于IP核的SoC接口技术

是基于核的免费开放的接口协议,可以根据不同IP核的通信要求进行配置和扩展,能够实现硬件集成真正的即插即用,允许系统集成根据应用需要选择最好的IP核

发表于 06-11 05:00

创龙带您解密TI、Xilinx异构多核SoC处理器核间通讯

1+1>2的效果。3.常见核间通信方式要充分发挥异构多核SoC处理器的性能,除开半导体厂家对芯片的硬件封装外,关键点还在于

发表于 09-08 09:39

实时操作系统中任务间通信的一种方法

针对实时内核这个缺点引入固定消息邮箱机制的通信方法. 这种方法的优点是:占用内存少,实时性强. 将固定消息邮箱机制与传统的

发表于 12-09 16:46

•46次下载

一种基于Mailbox核间机制的多核处理系统

基于FPGA的嵌入式应用在近几年来作为一个比较新颖的课题,本文在研究各种核间通信机制的基础上,提出了一种基于Mailbox核

发表于 11-22 17:31

•1.3w次阅读

进程间通信的机制有哪些

比较难,Linux内核提供了多种进程间通信的机制。 同一个进程的不同模块(譬如不同的函数)之间进行通信都是很简单的,譬如使用全局变量等。 通常情况下,大部分的程序是不要考虑进程

核间通信可能的实现机制

理解为软件可自由定义的中断模块。 用于在片上处理器之间通信的一种mailbox队列中断机制,mailbox队列中断机制允许软件通过一组寄存器和关联的中断设置和得到信息在二个处理之间建立通信

SoC的核间通信机制硬件邮箱

SoC的核间通信机制硬件邮箱

评论