电源是最容易被忽视的,电源是系统运行的重要组成部分,电源就像“人体的心脏”,为系统的硬件输送血液(电),要是心脏(电源)运行不正常或供血(电)不足,会导致系统不运行或运行不稳定,在设计之前应该对核心模块峰值电流表进行知悉,供PCB Layout时评估线宽作用,如表6-1,值得注意的是不能简单的全部加起来算成SOC的峰值电流,要评估散热方案,请根据实际场景的工作平均电流进行,表格参数值仅供参考。(文末附《RK3588PCB设计指导白皮书》下载入口)

3588电源的PCB设计主要注意以下几个方面:

1.1 RK806电源方案的PCB设计

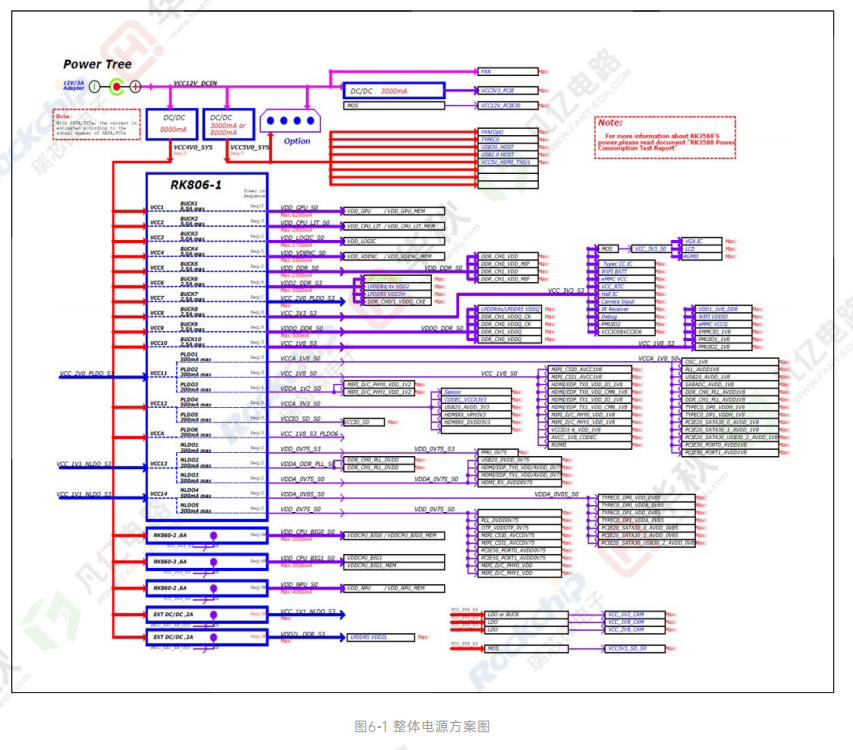

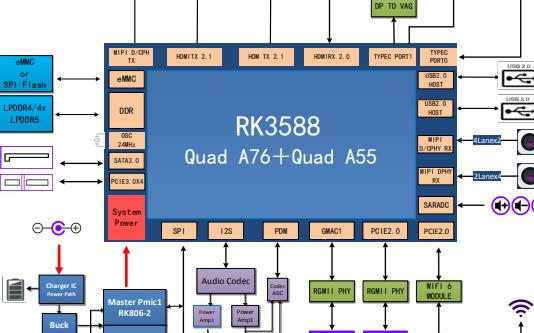

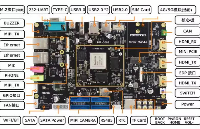

RK3588系统采用PMIC芯片RK806来进行整体供电,如图6-1所示。整体布局时在满足结构和特殊器件的布局同时RK806尽量靠近RK3588,如需要考虑散热设计,可以适当保持间距不要太靠近也不能离的太远,摆放方向时,尽量优先考虑 RK806的BUCK1、BUCK2、BUCK3、BUCK4这些输出电流比较大的电源到RK3588的信号流向是顺畅的。

1、RK806电源PCB总体要求

① 过孔数量以0.5*0.3mm尺寸的过孔为例,高压电源单个过孔推荐走0.8A,低压电源(1V 以下)按0.5A计算,当然也可以通过专业的计算工具进行计算。

② 不建议电源部分器件焊盘及过孔做十字连接处理,应该用铺铜全覆盖连接才能更好的散热和载流。

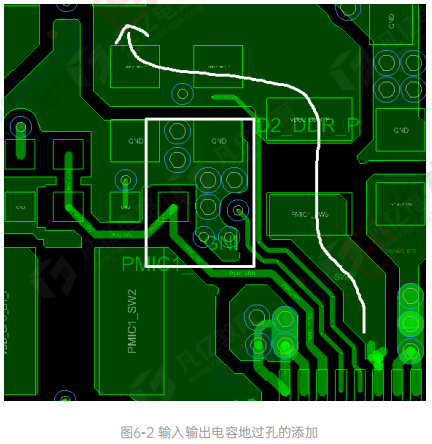

③ 大电流电路比如Buck输入输出电容的GND过孔应该要和电源输入端过孔数量多,如图6-2所示,这样才能起到较好的滤波效果(很多客户容易忽略电容GND端的过孔数量)。

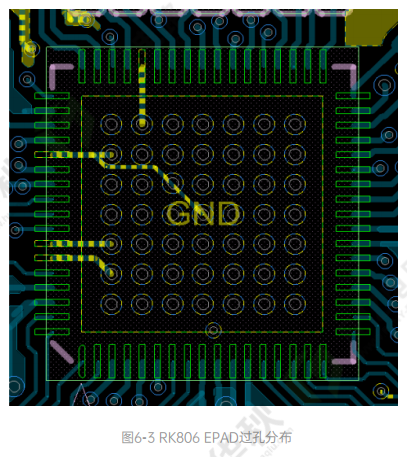

④ RK806的EPAD 接地焊盘要优先保证有足够的过孔,建议保证5*5个0.5*0.3mm 或是6*6 个0.4*0.2mm的过孔以上,降低接地阻抗和加强热量传导;盲埋孔的板子再打一些盲孔辅助降低阻抗,如图6-3所示。

2、RK806的BUCK13电路PCB要求

① 输入电容必须离芯片尽可能近,如果输入电容放在芯片的背面,需保证电容的GND端朝向芯片,这样让输入电容与VCC和GND的连接环路尽可能小。

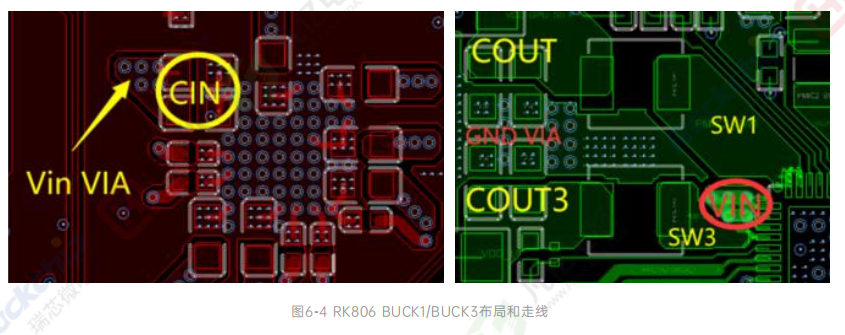

② 应当保证SW的走线出焊盘后尽可能短粗以提高载流能力及电源效率,对于需要打孔的地方,VCC1/3如果合并供电至少需要5 个0.5*0.3mm的过孔,如果分开各自需要3个及以上的0.5*0.3mm的过孔。

③ BUKC1和BUCK3的输出电容的GND端可以靠在一起共用但至少要15个以上的0.5*0.3mm过孔,如果空间不足可以打小过孔或盲孔补充。

④ BUCKl输出如果有换层至少保证15个及以上的0.5*0.3mm过孔,同样的BUCK3要保证12个及以上的0.5*0.3mm 过孔,如图6-4所示。

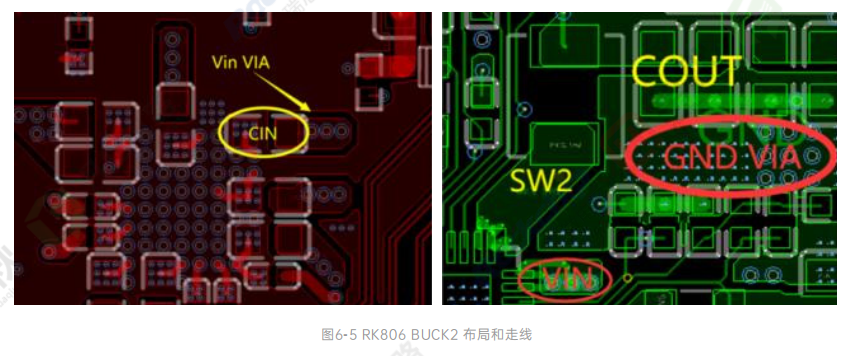

3、RK806的BUCK2电路PCB要求

① 输入电容必须离芯片尽可能近,如果输入电容放在芯片的背面,需保证电容的GND端朝向芯片,这样让输入电容与VCC和GND的连接环路尽可能小。

② 应当保证SW的走线出焊盘后尽可能短粗以提高载流能力及电源效率,对于需要打孔的地方,VCC2供电至少需要3个0.5*0.3mm过孔,输出电容的GND端至少要12个以上的0.5*0.3mm过孔,如果空间不足可以打小过孔或盲孔补充。

③ 输出如果有换层至少保证12个及以上的0.5*0.3mm过孔,如图6-5所示。

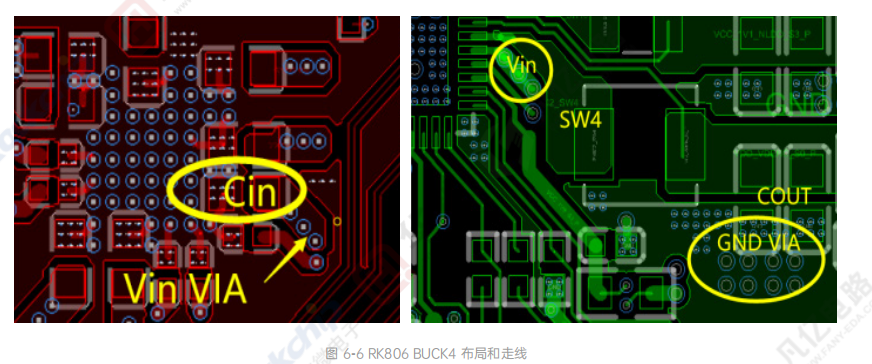

4、RK806的BUCK4电路PCB布局布线要求

① 输入电容必须离芯片尽可能近,如果输入电容放在芯片的背面,需保证电容的GND端朝向芯片,这样让输入电容与VCC和GN的连接环路尽可能小。

② 应当保证SW的走线出焊盘后尽可能短粗以提高载流能力及电源效率,对于需要打孔的地方,VCC4供电至少需要3个0.5*0.3mm的过孔,输出电容的GND端至少要12个以上的 0.5*0.3mm过孔,如果空间不足可以打小过孔或盲孔补充,如图6-6所示。

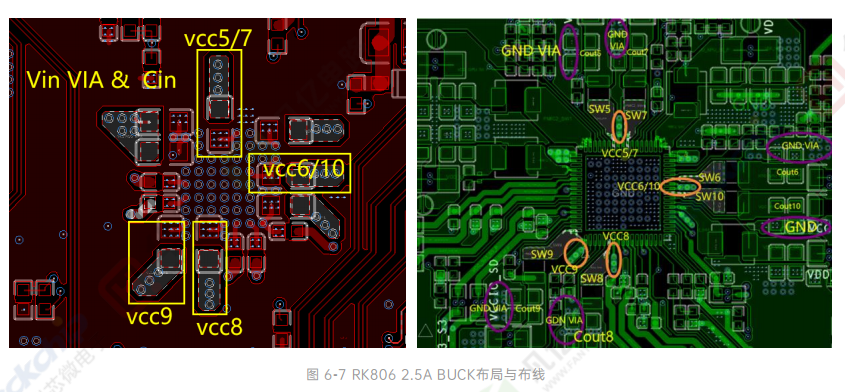

5、RK806的2.5A BUCK电路PCB要求

① 输入电容必须离芯片尽可能近,如果输入电容放在芯片的背面,需保证电容的GND端朝向芯片,这样让输入电容与VCC和GND的连接环路尽可能小,如图6-7所示。

② 应当保证SW的走线出焊盘后尽可能短粗以提高载流能力及电源效率。

③ 对于需要打过孔的地方,VCC5/6/7/10供电至少需要3个0.5*0.3mm的过孔,VCC8/9至少需要2个0.5*0.3mm的过孔,输出电容的GND端至少要5个及以上的0.5*0.3mm过孔,如果空间不足可以打盲孔补充,如图6-8所示。

④ 输出如果要换层至少保证5个及以上的0.5*0.3mm过孔换层。

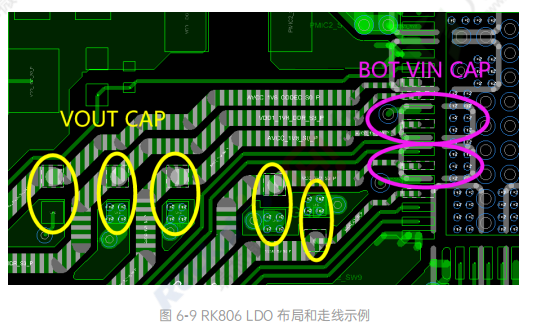

6、RK806 的 LDO电路PCB布局布线要求

① 输入电容必须离芯片尽可能近,输入电容与VCC11/12/13/14和GND的连接环路尽可能小。

② 输出电容必须离芯片尽可能近,输出电容与PLDO1/2/3/4/5/6及NLDO1/2/3/4/5和GND的连接环路尽可能小。

③ RK806的VCCA电容必须靠近管脚放置,远离其它干扰源,电容的地焊盘必须良好接地,即VCCA电容地焊盘和RK806 EPAD之间路径必须保证最短,不得被其他信号分割。

④ RK806的Pin 67(RESETB)的100nF电容必须靠近RK806管脚,提高芯片抗干扰能力。

⑤ RK806 LDO部分管脚不建议覆铜,所有管脚通过走线方式和外面连接,焊盘内走线宽度不得超过焊盘宽度,防止制板后,焊盘变大贴片容易连锡。

⑥ 走线粗线一般按1mm宽度走1A来设计,大电流输出的LDO根据后端实际供电需求,走线在从芯片引出后应尽快变粗到需求大小,要特别关注低压大电流NLDO的走线长度及损耗,以满足目标芯片的供电电压及纹波需求。如图6-9所示。

1.2 分立电源的DC-DCPCB设计

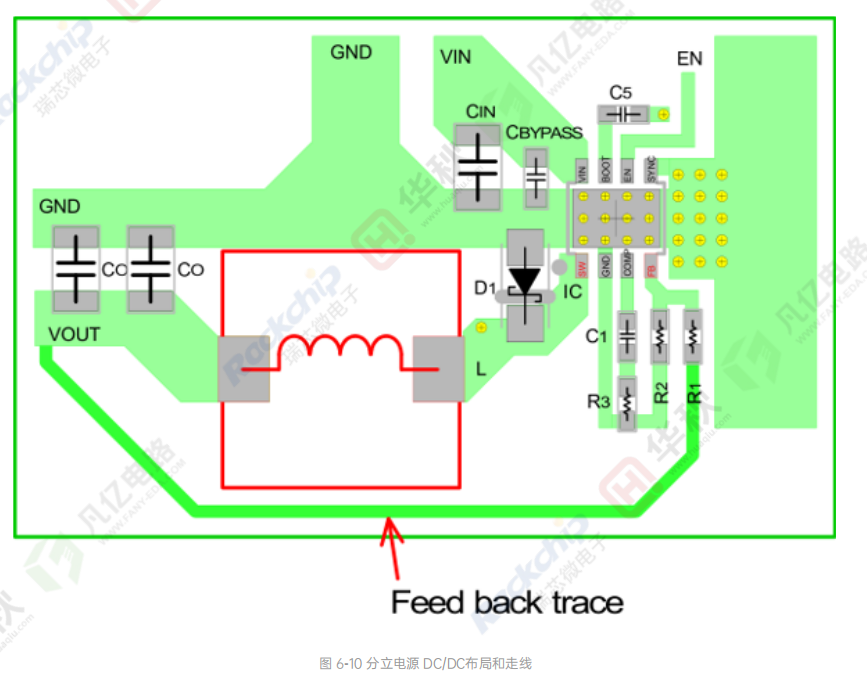

输入电容Cin、输出电容Cout放置于Vin管脚、Vout管脚与DC/DC的GND之间,尽量减小Vin、Vout与DC/DC的GND之间的环路面积,这样可以减小电源纹波幅度,大大提高芯片的可靠性,如图6-10所示。

输入电容Cin、输出电容Cout以及DC/DC的GND,要尽量多打一些过孔,建议4个及以上的0.5*0.3mm过孔,如果 Vin,Vout电源有换层,建议过孔也要多打一些过孔,建议4个以上的0.5*0.3mm过孔(和电流有关系,参考上面RK3588峰值电流表)。电感要尽量靠近DC/DC,走线要尽量粗而短,FB端的电阻地尽量远离干扰源,不要从电感下面走线。

1.3 RK860电源PCB设计

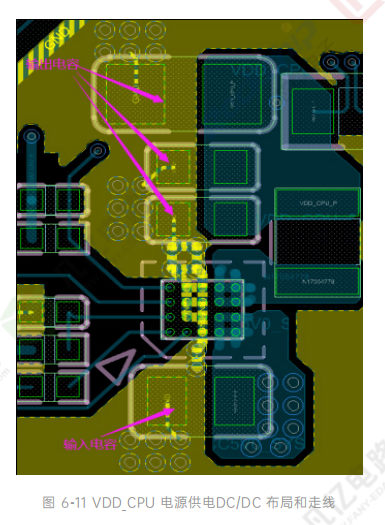

RK860-X做为单颗RK806-1的辅助补充供电,一般给CPU、GPU或NPU等大电流供电。整体布局时应尽量靠近RK3588(10mm以内为佳)。RK860 PCB布局推荐参考如图6-11所示,需要注意的是输入或者输出的回路。

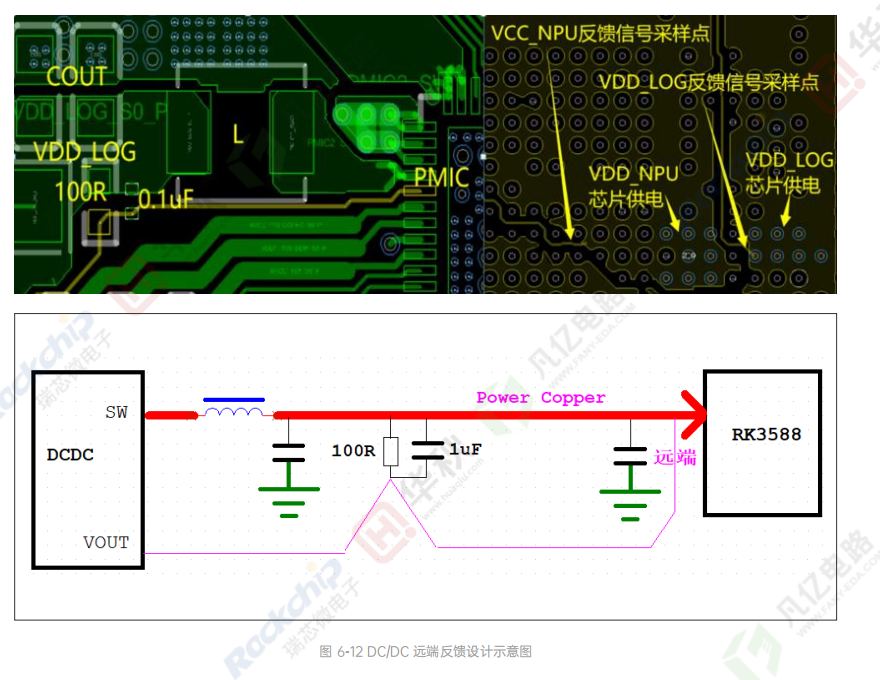

DC-DC转换中会涉及到反馈电压,远端反馈是反馈点选择在负载端;在PCB进行布线的时候,需要慎重考虑布线的方式,要充分考虑到布线产生的线路阻抗100欧姆反馈电阻需要靠近输出电容尽量靠近PMIC放置,电阻一端连接到DC-DC输出电容,另一端连接到PMIC的VOUT反馈脚上,并同时连接到RK3588电源管脚同一电源网络的最远端负载处。

反馈线宽度使用4mil,必须与电源覆铜伴随走线,以避免干扰;反馈线与其他信号间隔6mil以上,如图6-12所示, VDD_GPU电源覆铜及反馈线走线示意图,其它路电源类似处理。

1、输入输出电容分别摆在芯片的两端并尽量靠近芯片,电容、电感和芯片布局在同一层,电容的GND焊盘和芯片的GND在焊盘朝向是同一个方向,形成一个最小的闭环。

2、电感放在输出电容和芯片两端保证SW走线尽可能短,防止对其他模块造成干扰。

3、芯片VOUT反馈信号要保证取自输出电容(避免从电感焊盘上取),并避免离SW太近。

4、对于需要打过孔的地方,可以5个0.5*0.3mm的过孔,Buck输出至少需要12个0.5*0.3mm的过孔。特别是GND过孔尽量靠近芯 GND和电容焊盘,如果是盲埋孔的板子就在芯片和电容的GND焊盘补一些盲孔。

1.4 VDD_LOGIC,VDD_GPU,VDD_NPU,VDD_CPU电源的DC-DC远端反馈设计

DC-DC转换中会涉及到反馈电压,远端反馈是反馈点选择在负载端;在PCB进行布线的时候,需要慎重考虑布线的方式,要充分考虑到布线产生的线路阻抗100欧姆反馈电阻需要靠近输出电容尽量靠近PMIC放置,电阻一端连接到DC-DC输出电容,另一端连接到PMIC的VOUT反馈脚上,并同时连接到RK3588电源管脚同一电源网络的最远端负载处。

反馈线宽度使用4mil,必须与电源覆铜伴随走线,以避免干扰;反馈线与其他信号间隔6mil以上,如图6-12所示, VDD_GPU电源覆铜及反馈线走线示意图,其它路电源类似处理。

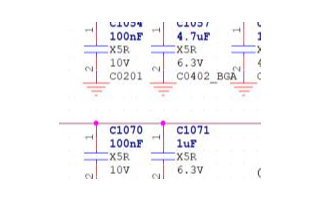

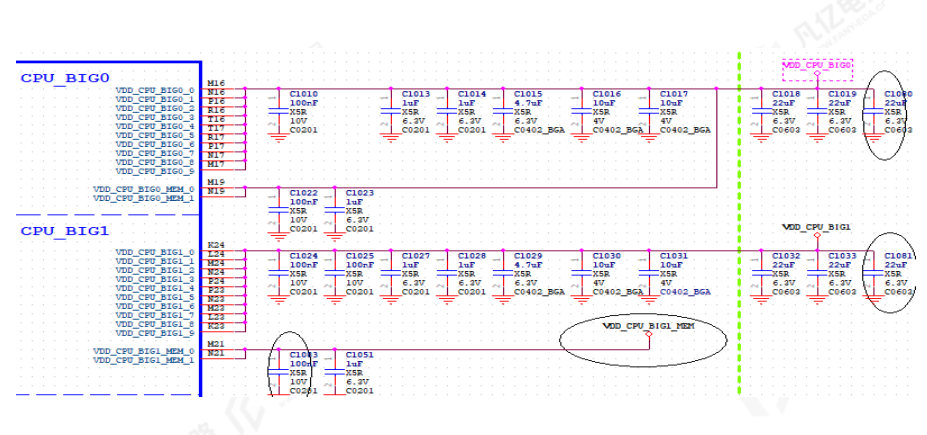

1.5 RK3588VDD_CPU_BIG0/1 电源PCB设计

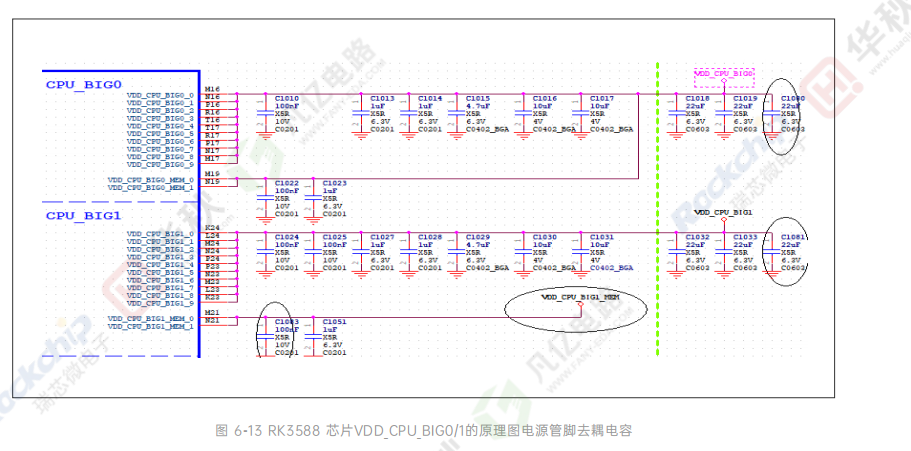

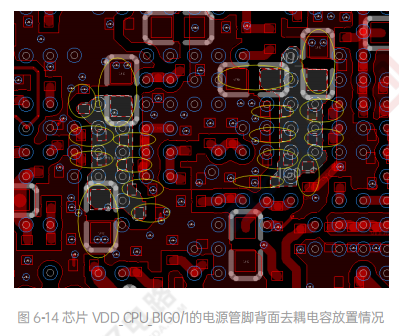

1、如图6-13所示的滤波电容,原理图上靠近 RK3588的VDD_CPU_BIG电源管脚绿线以内的去耦电容务必放在对应的电源管脚背面,电容GND PAD尽量靠近芯片中心的GND管脚放置,如图6-14所示。其余的去耦电容尽量摆放在3588芯片附近,而却需要摆放在电源分割来源的路径上。

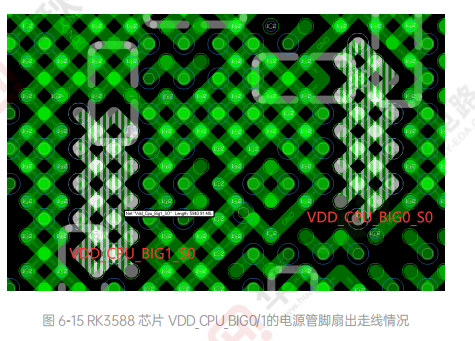

2、RK3588芯片VDD_CPU_BIG0/1的电源管脚,保证每个管脚边上都有一个对应的过孔,并且顶层走“井”字形,交叉连接,如图6-15所示,建议走线线宽10mil。

3、VDD_CPU_BIG0/1覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚路径都足够。

4、VDD_CPU_BIG的电源在外围换层时,要尽可能的多打电源过孔12个及以上0.5*0.3mm的过孔,降低换层过孔带来的压降;去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用。

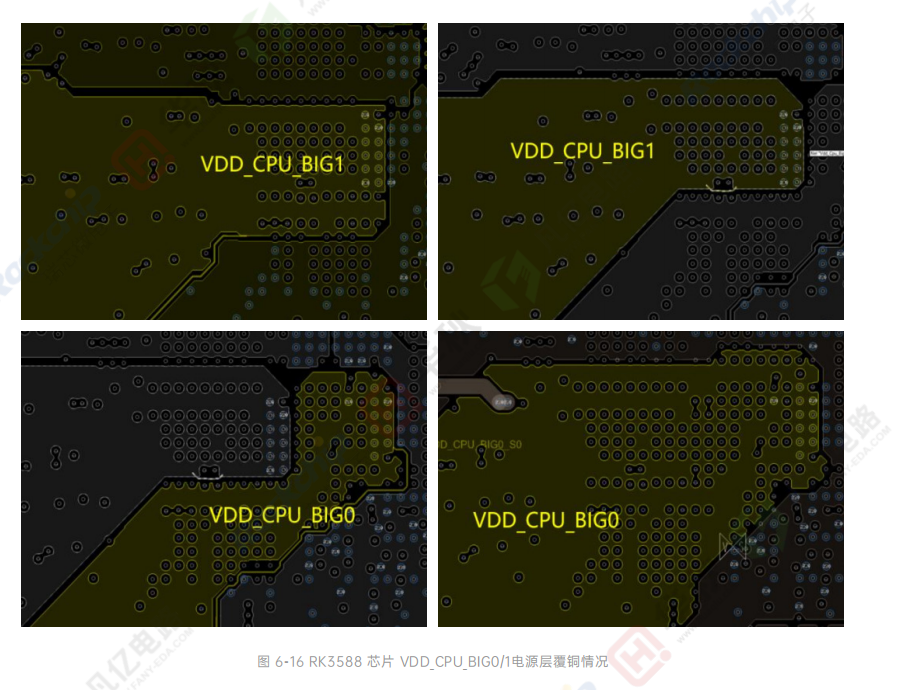

5、VDD_CPU_BIG电流比较大需要双层覆铜,VDD_CPU_BIG 电源在 CPU 区域线宽合计不得小于 300mil,外围区域宽度不小于600mil,尽量采用覆铜方式,降低走线带来压降其它信号换层过孔请不要随意放置,必须规则放置,尽量腾出空间走电源,也有利于地层的覆铜,如图6-16所示。

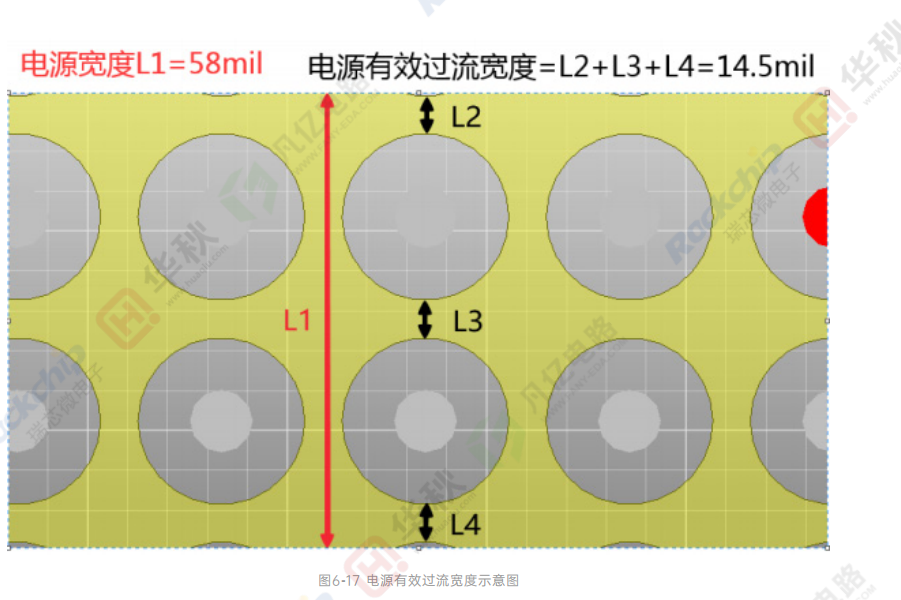

6、电源平面会被过孔反焊盘破坏,PCB设计时注意调整其他信号过孔的位置,使得电源的有效宽度满足要求。下图L1为电源铜皮宽度58mil,由于过孔的反焊盘会破坏铜皮,导致实际有效过流宽度仅为L2+L3+L4=14.5mil,如图6-17所示。

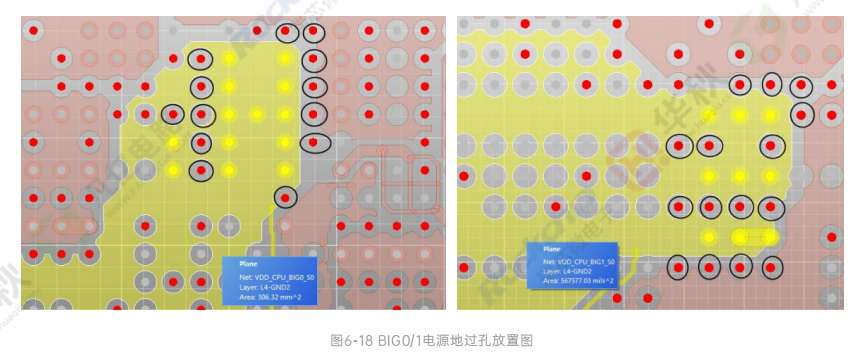

7、BIG0/1电源过孔40mil范围(过孔中心到过孔中心间距)内的GND过孔数量,建议≧12个,如图6-18所示。

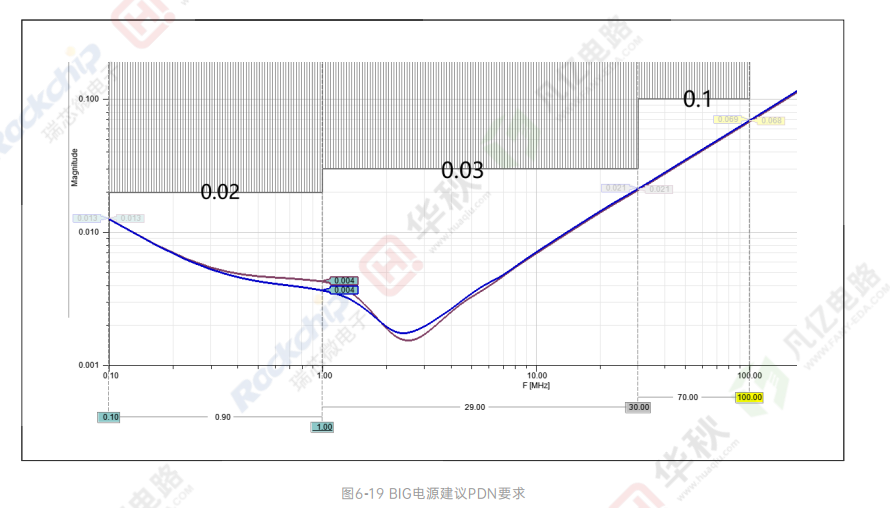

8、BIG电源PDN目标阻抗建议值如下表6-2所示和图6-19所示:

1.6 RK3588 VDD_LOGIC电源PCB设计

1、VDD_LOGIC的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚路径都足够。

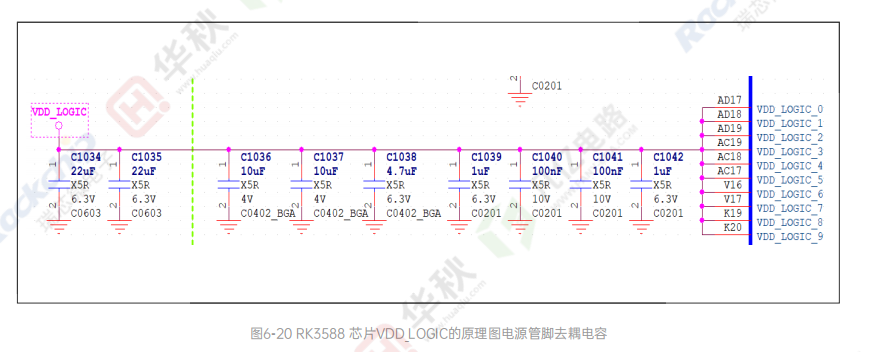

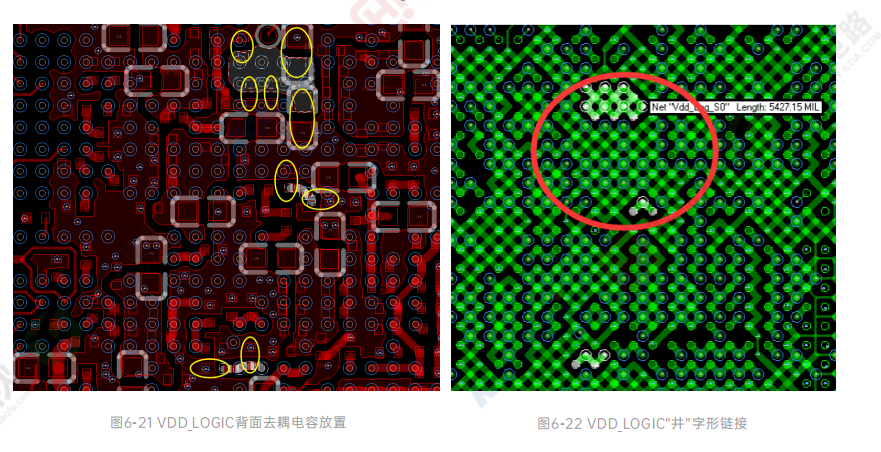

2、如图6-20所示,原理图上靠近RK3588的VDD_LOGIC电源管脚绿线以内的去耦电容务必放在对应的电源管脚背面,电容的GND管脚尽量靠近芯片中心的GND管脚放置,如图6-21所示。其余的去耦电容尽量摆放在RK3588芯片附近,并摆放在电源分割来源的路径上。

3、RK3588芯片VDD_LOGIC的电源管脚,每个管脚需要对应一个过孔,并且顶层走“井”字形,交叉连接,如图6-22所示,建议走线线宽10mil。

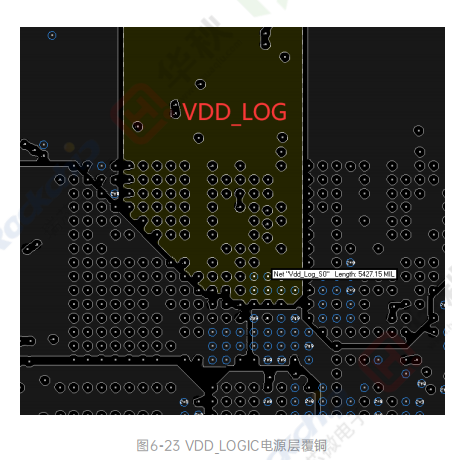

4、VDD_LOGIC电源在CPU区域线宽不得小于120mil,外围区域宽度不小于200mil,尽量采用覆铜方式,降低走线带来压降(其它信号换层过孔请不要随意放置,必须规则放置,尽量腾出空间走电源,也有利于地层的覆铜),如图6-23所示。

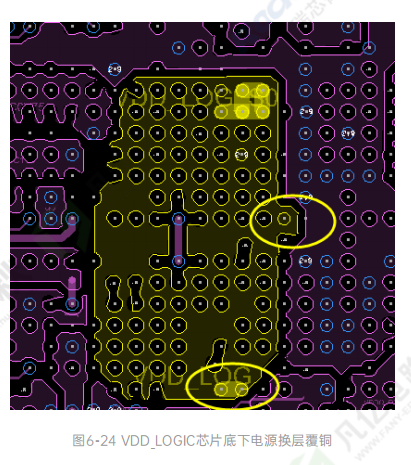

5、VDD_LOGIC的电源在外围换层时,要尽可能的多打电源过孔(8个以上10-20mil的过孔),降低换层过孔带来的压降;去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用,如图6-24所示。

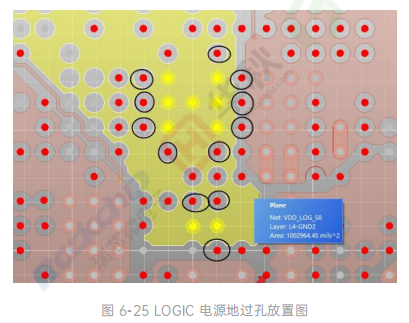

6、电源过孔40mil范围(过孔中心到过孔中心间距)内的GND过孔数量,建议≧11个,如图6-25所示。

1.7 RK3588 VDD_GPU电源PCB 设计

1、VDD_GPU的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。

2、VDD_GPU 的电源在外围换层时,要尽可能的多打电源过孔(10个以上0.5*0.3mm的过孔),降低换层过孔带来的压降;去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用。

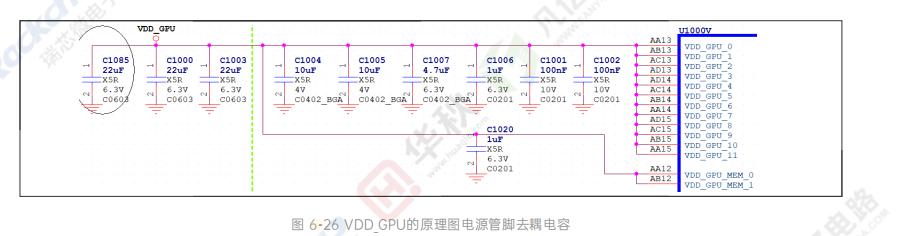

3、如图6-26所示,原理图上靠近RK3588的VDD_GPU电源管脚绿线以内的去耦电容务必放在对应的电源管脚背面,电容的GND PAD尽量靠近芯片中心的GND管脚放置,如图6-27所示。其余的去耦电容尽量摆放在RK3588芯片附近,并需要摆放在电源分割来源的路径上。

4、RK3588芯片VDD_GPU的电源管脚,每个管脚需要对应一个过孔,并且顶层走“井”字形,交叉连接,如图6-28所示,建议走线线宽10mil。

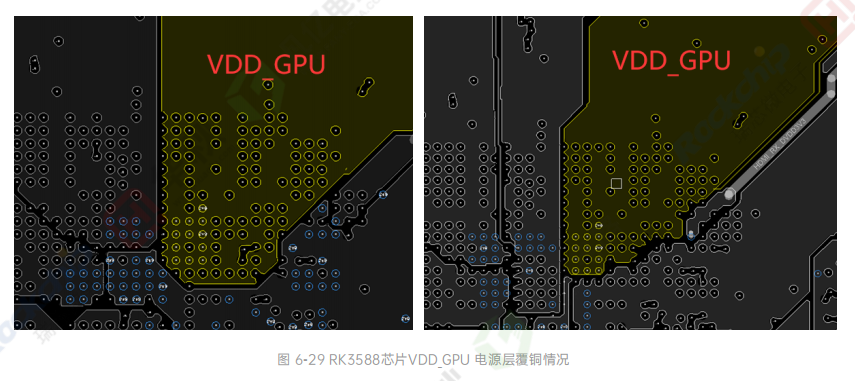

5、VDD_GPU电源在GPU区域线宽不得小于300mil,外围区域宽度不小于500mil,采用两层覆铜方式,降低走线带来压降,如图6-29所示。

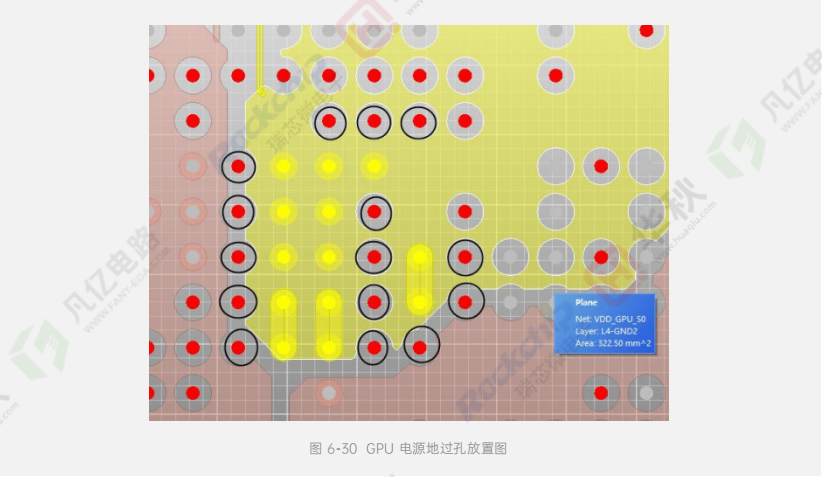

6、电源过孔40mil范围(过孔中心到过孔中心间距)内的GND过孔数量,建议≧14个,如图6-30所示。

1.8 RK3588 VDD_NPU电源PCB设计

1、VDD_NPU的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。

2、VDD_NPU的电源在外围换层时,要尽可能的多打电源过孔(7个以上0.5*0.3mm的过孔),降低换层过孔带来的压降;去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用。

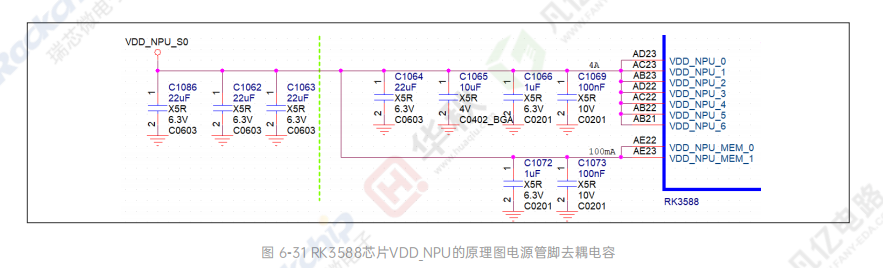

3、如图6-31所示,原理图上靠RK3588的VDD_NPU电源管脚绿线以内的去耦电容务必放在对应的电源管脚背面,电容的GND PAD尽量靠近芯片中心的GND管脚放置,如图6-32所示。其余的去耦电容尽量摆放在RK3588芯片附近,并需要摆放在电源分割来源的路径上。

4、RK3588芯片VDD_NPU的电源管脚,每个管脚就近有一个对应过孔,并且顶层走“井”字形,交叉连接,如图6-33所示 ,建议走线线宽10mil。

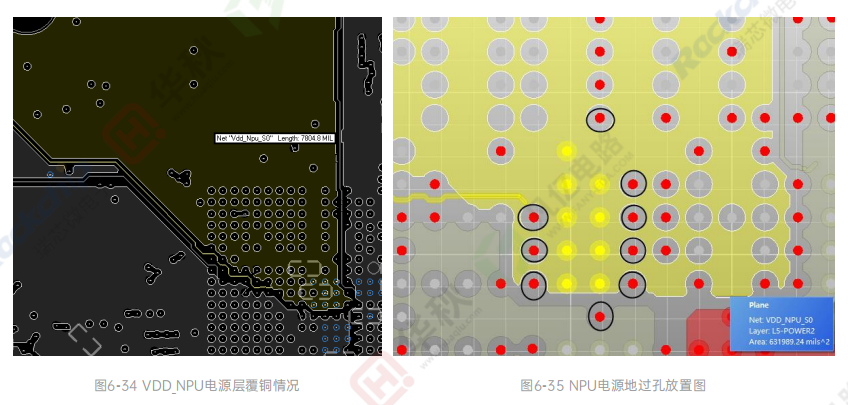

5、VDD_NPU电源在NPU区域线宽不得小于300mil,外围区域宽度不小于500mil,尽量采用覆铜方式,降低走线带来的压降(其它信号换层过孔请不要随意放置,必须规则放置,尽量腾出空间走电源,也有利于地层的覆铜,如图6-34)。

6、电源过孔40mil范围(过孔中心到过孔中心间距)内的GND过孔数量,建议≧9个。如图6-35所示。

1.9 RK3588 VDD_CPU_LIT电源PCB设计

1、VDD_CPU_LIT覆铜宽度需满足芯片电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。

2、VDD_CPU_LIT的电源在外围换层时,要尽可能的多打电源过孔(9个以上0.5*0.3mm的过孔),降低换层过孔带来的压降;去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用。

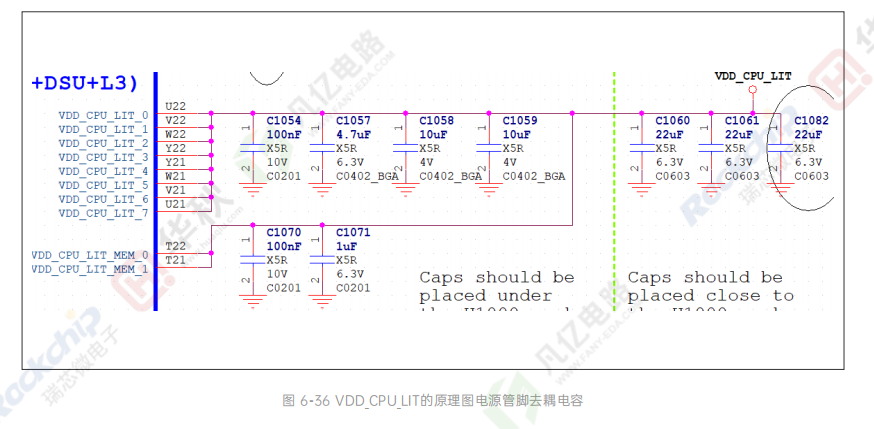

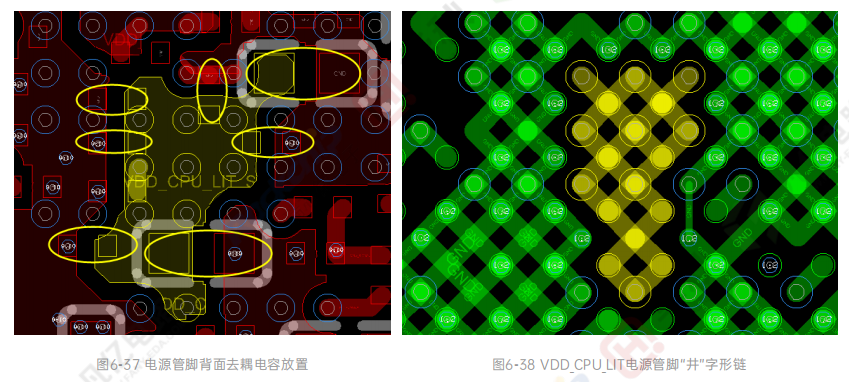

3、如图6-36所示,原理图上靠近RK3588的VDD_CPU_LIT电源管脚绿线以内的去耦电容务必放在对应的电源管脚背面,电容的GND PAD尽量靠近芯片中心的GND管脚放置,如图6-37所示。其余的去耦电容尽量摆放在RK3588芯片附近,并需要摆放在电源分割来源的路径上。

4、RK3588芯片VDD_CPU_LIT的电源管脚,每个管脚就近有一个对应过孔,并且顶层走“井”字形,交叉连接,如图6-38所示,建议走线线宽10mil。

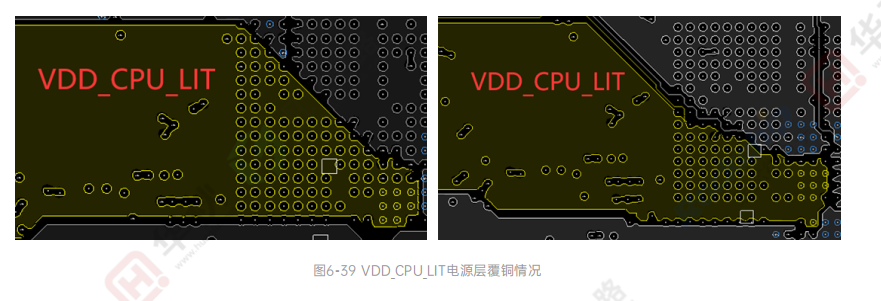

5、VDD_CPU_LIT电源在CPU 区域线宽不得小于120mil,外围区域宽度不小于300mil,采用双层电源覆铜方式,降低走线带来压降(其它信号换层过孔请不要随意放置,必须规则放置,尽量腾出空间走电源,也有利于地层的覆铜,如图6-39所示)。

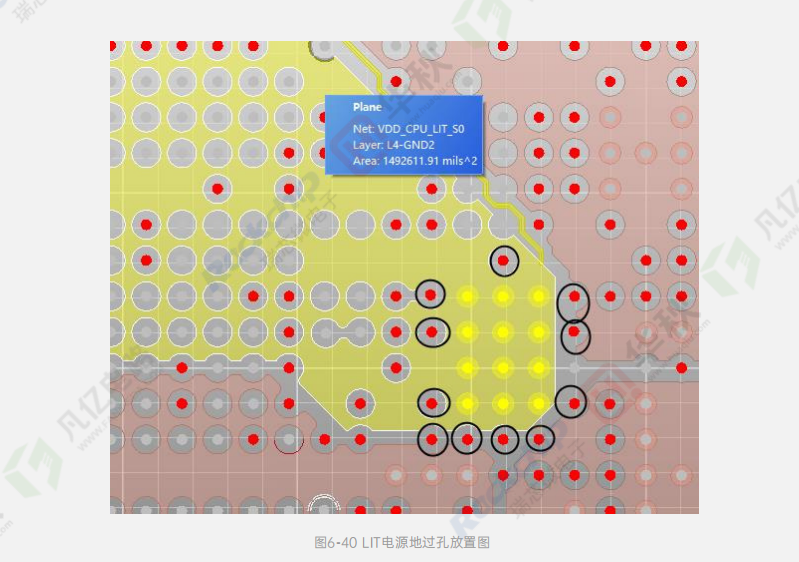

6、电源过孔40mil范围(过孔中心到过孔中心间距)内的GND过孔数量,建议≧9个。如图6-40所示。

1.10 RK3588 VDD_VDENC电源PCB设计

1、VDD_VDENC覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。

2、VDD_VDENC电源在外围换层时,要尽可能的多打电源过孔(9个以上0.5*0.3mm的过孔),降低换层过孔带来的压降;去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用。

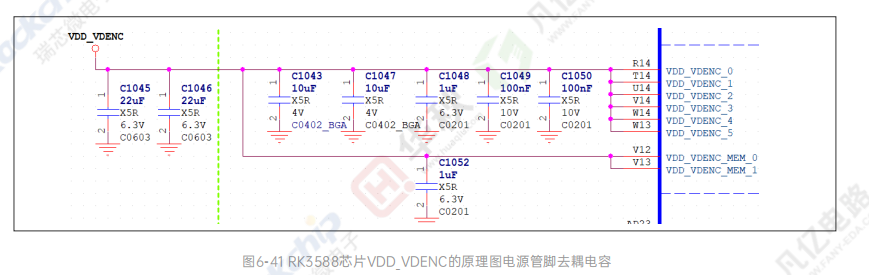

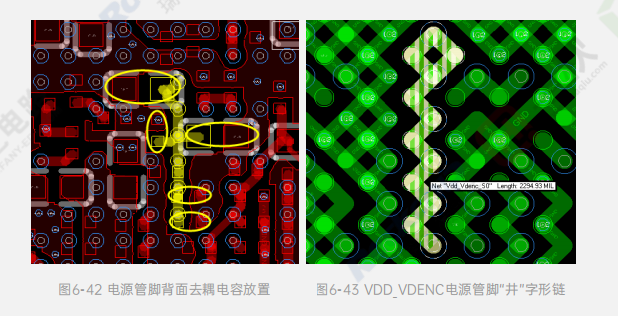

3、如图6-41所示,原理图上靠近RK3588的VDD_VDENC电源管脚绿线以内的去耦电容务必放在对应的电源管脚背面,电容的GND PAD尽量靠近芯片中心的GND管脚放置,如图6-42所示。其余的去耦电容尽量摆放在RK3588芯片附近,并需要摆放在电源分割来源的路径上。

4、RK3588芯片VDD_VDENC的电源管脚,每个管脚就近有一个对应过孔,并且顶层走“井”字形,交叉连接,如图6-43所示,建议走线线宽 10mil。

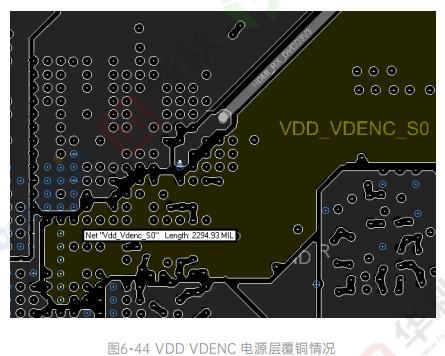

5、VDD_VDENC电源在CPU区域线宽不得小于100mil,外围区域宽度不小于300mil,采用双层电源覆铜方式,降低走线带来压降,如图6-44所示。

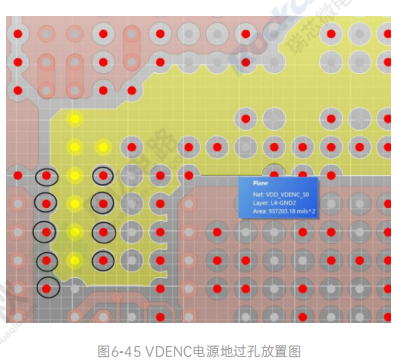

6、电源过孔30mil范围(过孔中心到过孔中心间距)内的 GND 过孔数量,建议≧8个。如图6-45所示。

1.11 RK3588 VCC_DDR电源PCB设计

1、VCC_DDR覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。

2、VCC_DDR的电源在外围换层时,要尽可能的多打电源过孔(9个以上0.5*0.3mm的过孔),降低换层过孔带来的压降;去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用。

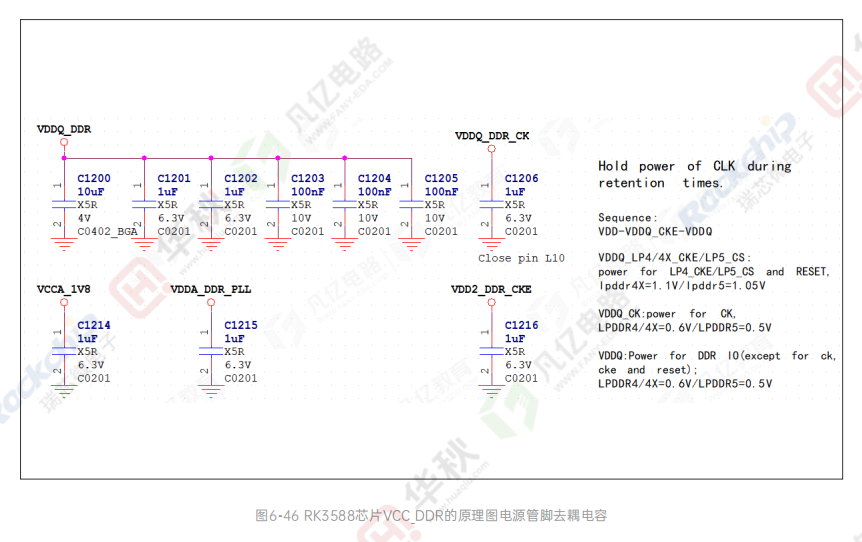

3、如图6-46所示,原理图上靠近RK3588的VCC_DDR电源管脚的去耦电容务必放在对应的电源管脚背面,电容的GND PAD尽量靠近芯片中心的GND管脚放置,其余的去耦电容尽量靠近RK3588,如图6-47所示。

4、RK3588 芯片 VCC_DDR 的电源管脚,每个管脚需要对应一个过孔,并且顶层走“井”字形,交叉连接,如图6-48所示,建议走线线宽 10mil。

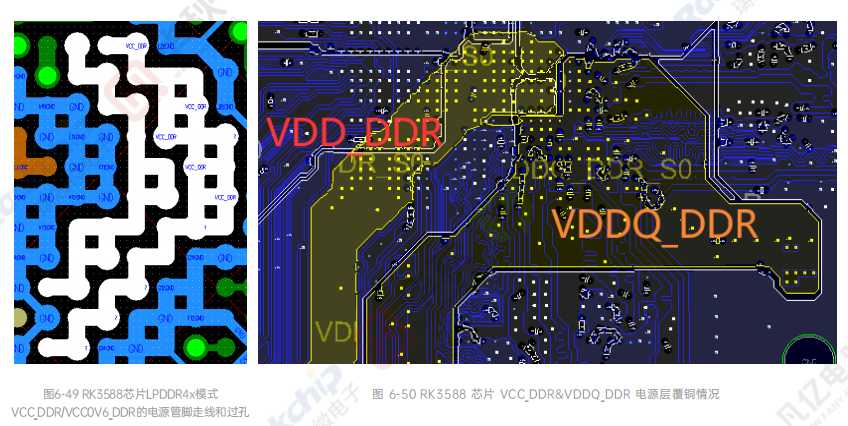

当LPDDR4x 时,链接方式如图6-49所示:

5、VCC_DDR电源在CPU区域线宽不得小于120mil,外围区域宽度不小于200mil,尽量采用覆铜方式,降低走线带来压降(其它信号换层过孔请不要随意放置,必须规则放置,尽量腾出空间走电源,也有利于地层的覆铜,如图6-50所示)。

1.12 RK3588 GND管脚PCB设计

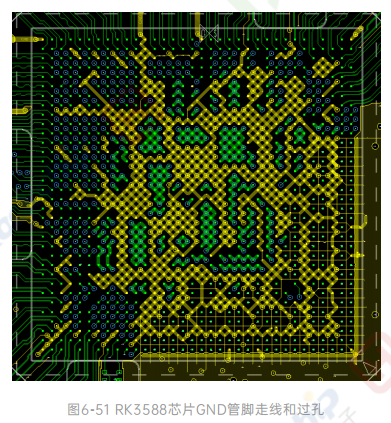

1、RK3588芯片的GND管脚,至少保证每2个管脚需要对应一个过孔,尽量每个管脚对应一个过孔,提供更优的SI(信号完整性),PI(电源完整性)条件,以及对散热也有帮助。

2、RK3588芯片的相邻层必须是一个完整的 GND 平面,保证主参考地靠近CPU的管脚,用于保证电源完整性以及加强PCB 的散热。

3、RK3588芯片下方相同网络的GND管脚在顶层走“井”字形,交叉连接,建议走线线宽10mil。如图6-51所示。

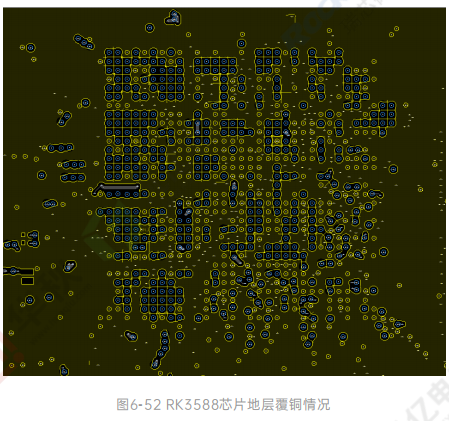

4、在Layout 时,RK3588的各信号放置换层过孔时,要求打在管脚间隔的正中间,有规律的放置,如图6-52,GND层的覆铜情况,RK3588芯片中间的地有大面积的铜皮和外面地铜皮连接,一方面有利于电源信号完整性,另外一方面有利于芯片散热。

1.13 RK3588 其它电源的PCB设计

1、RK3588其它电源去耦电容,必须放在芯片管脚背面,走线时尽量形成先经过电容焊盘再到芯片管脚。

2、无论是输入或是输出、功率环路或信号环路,应尽可能的小。功率环路发射电磁场,将导致较差的EMI特性或较大的输出噪声;同时,若被控制环接收,很可能引起异常。

3、另一方面,若功率环路面积较大,其等效寄生电感也会增大,可能增加漏极噪声尖峰。

审核编辑:汤梓红

-

电源电路

+关注

关注

48文章

998浏览量

65208 -

PCB设计

+关注

关注

394文章

4689浏览量

85678 -

PMIC

+关注

关注

15文章

335浏览量

109500 -

RK3588

+关注

关注

6文章

329浏览量

4353

原文标题:RK3588 PMIC/Power电路PCB设计(附白皮书下载)

文章出处:【微信号:发烧友研习社,微信公众号:发烧友研习社】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

RK3588 VDD_CPU_LIT电源PCB设计

瑞芯微RK3588开发板RK3588 EVB和RK3588S EVB解读

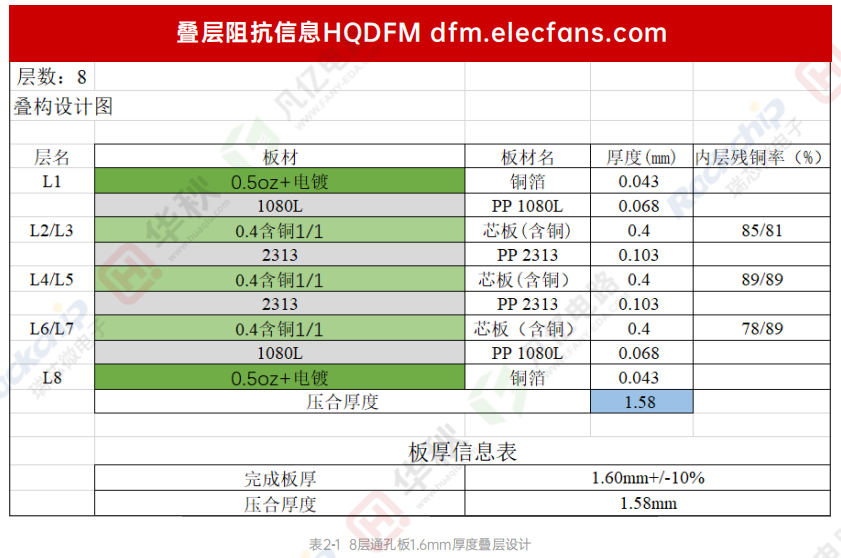

RK3588 PCB推荐叠层及阻抗设计

RK3588 VDD_LOGIC电源PCB设计注意事项

用这份PCB设计实战手册轻松搞定RK3588

用这份PCB设计实战手册,轻松搞定RK3588

【全是干货】《RK3588 PCB设计指导白皮书》线上发布&实战解读

PCB设计没头绪?RK3588 PCB设计指导,搞硬件必入手!

RK3588和RK3588S之间的区别是什么

rk3588和rk3588s的区别

RK3588与3588s的区别

RK3588 VDD_CPU_BIG0/1 电源PCB设计注意事项

RK3588电源电路PCB设计方案

RK3588电源电路PCB设计方案

评论