前言:

近20年来,EUV光源、EUV掩模和EUV光刻胶一直是EUV光刻的三大技术挑战。

近几年来,随着EUV光源的不断进展,EUV掩模开始位居三大技术挑战之首,而EUV掩模最困难的环节之一就是EUV薄膜。

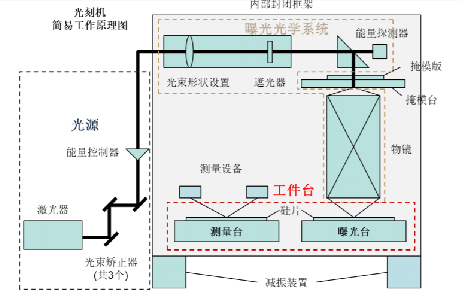

***的一系列流程,掩模是其中一环

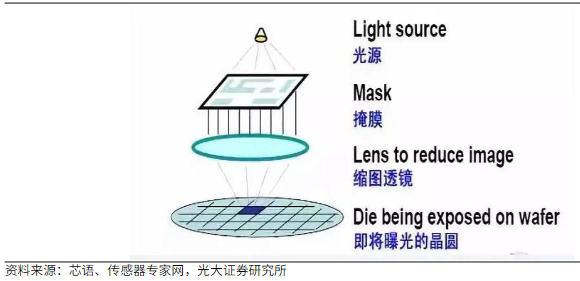

光刻的原理是在硅片表面覆盖一层具有高度光敏感性光刻胶,再用光线透过掩模照射在硅片表面,被光线照射到的光刻胶会发生反应。

此后用特定溶剂洗去被照射/未被照射的光刻胶,就实现了电路图从掩模到硅片的转移。

光刻完成后对没有光刻胶保护的硅片部分进行刻蚀,最后洗去剩余光刻胶,就实现了半导体器件在硅片表面的构建过程。

***通过一系列的光源能量、形状控制手段,将光束透射过画着线路图的掩模;

经物镜补偿各种光学误差,将线路图成比例缩小后映射到硅片上;

然后使用化学方法显影,得到刻在硅片上的电路图。

EUV薄膜容错成本高,成芯片良率的关键

芯片生产的难点和关键点在于将电路图从掩模上转移至硅片上。

这一过程通过光刻来实现,光刻的工艺水平直接决定芯片的制程水平和性能水平。

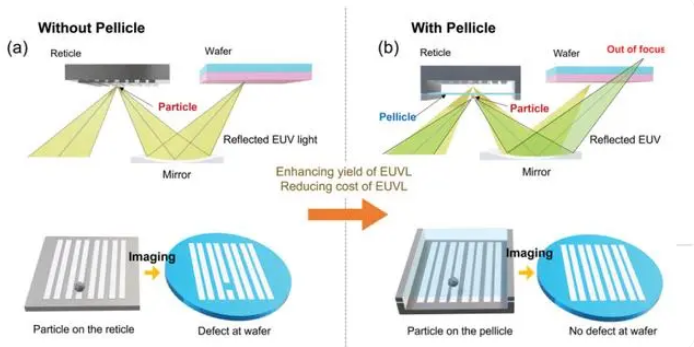

EUV薄膜是一种超薄薄膜形态的、需要定期更换的高端消耗品,防止在EUV掩模的顶层,同时允许高EUV光透射率。

它安装在光掩模表面上方几毫米处,在EUV曝光工艺中保护EUV掩模表面免受空气中颗粒或污染物影响。

如果颗粒落在EUV薄膜上,由于这些颗粒离焦,不会曝光在晶圆上,从而最大限度地减少曝光缺陷。

但是,在EUV光刻工艺中,EUV光通过EUV薄膜两次。

一次入射到EUV掩模,另外一次出射到EUV投影光学系统。

当EUV灯击中防护薄膜时,膜的温度将从600摄氏度升高到1000摄氏度。

单块EUV掩模成本超过30万美元,EUV薄膜在EUV光刻中保护极其昂贵的6英寸EUV掩模,使其远离可能落在其表面的颗粒。

这对于CPU芯片的生产最为重要,CPU芯片使用的是单芯片掩模,任何一个EUV掩模缺陷就会有可能使整个晶圆失效。

同时,EUV薄膜在EUV工艺时代起着至关重要的作用,可以防止EUV受污染而导致良率性能不佳。

ASML率先研发推出,三星、台积电等紧随其后

ASML公司在2014年研制出面积达106mm×139mm的多晶硅EUV薄膜,但是其厚度为70nm,EUV透过率最高为86%。

芬兰Canatu公司在2015年建立了第一个生产碳纳米管的生产线,与IMEC合作,开发基于碳纳米管的EUV薄膜。

不同于ASML的技术路线,IMEC采用的是碳纳米管,EUV透过率高达97.7%,可以将生产效率提高约25%。

从2019年以来,台积电一直在其量产线上使用自己开发的EUV薄膜;2021年其EUV薄膜生产能力比2019年提高了20倍。

三星电子显然也意识到了EUV薄膜在提升EUV光刻良率的重要性,一直在积极开发和评估由碳纳米管和石墨烯制成的EUV薄膜。

在2021年三星表示已经开发出一种EUV透射率为82%的薄膜,并计划在年底前将透射率提高到88%。

并投资S&STECH公司和FST公司,确保研发出EUV透射率为90%的石墨烯EUV薄膜。

据台媒DIGITIMES报道,三星电子将在其3nm工艺中采用透光率超过90%的最新EUV薄膜以提高良率,这些薄膜将来自韩国公司S&STech。

材料和转移工艺挑战,石墨烯是最大希望

此前,硅已被用于制造薄膜,但石墨烯是一种更好的材料,因为它比硅更薄、更透明。

EUV薄膜必须能够承受曝光过程中发生的800度或更高的高温,由于其在高温下的硬化特性,硅胶非常容易破裂。

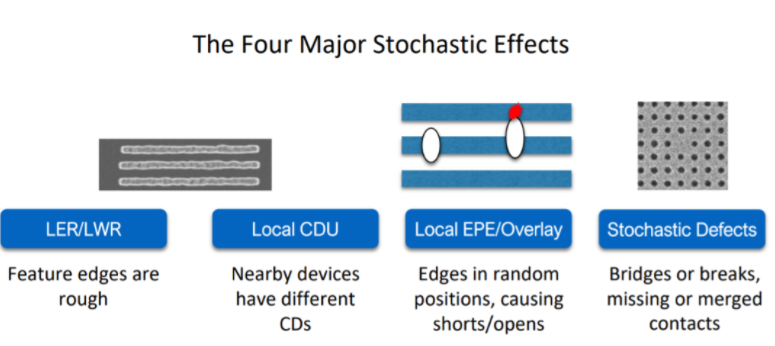

薄膜材料制造面临着结构挑战,因为制程基于独立在几十纳米的框架上,很容易导致薄膜出现裂缝或断裂。

为了满足这些严格的标准,需要在薄膜材料和转移工艺方面的研发取得突破。

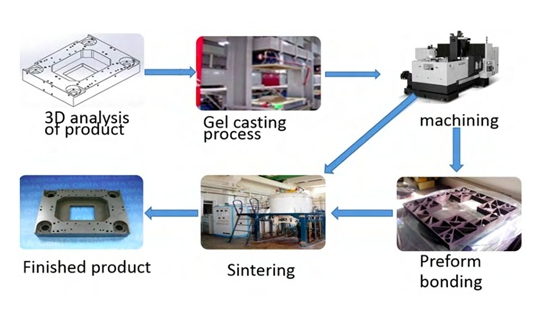

石墨烯是一个单原子层,仅包含具有sp2杂化化学键的碳原子,具有优异的导热性和导电性、化学和机械特性,以及隔离金属表面的保护屏障,使其能够成为满足EUVL技术的保护膜。

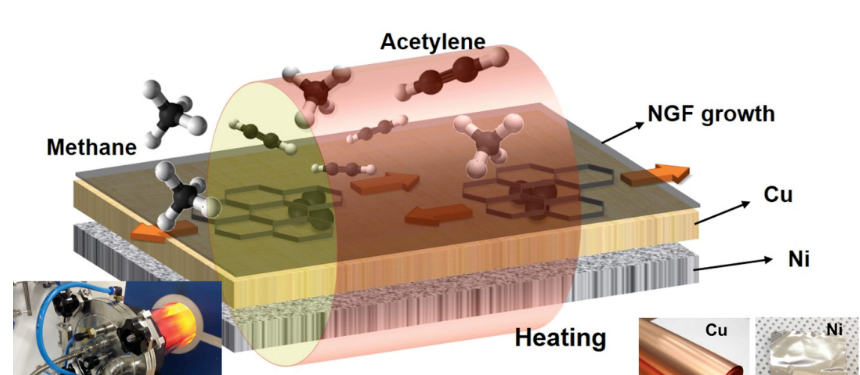

CVD因具有可控、高质量生长石墨烯的优点而引起国内外关注,据报道石墨烯薄膜可在多个衬底上生长,如Fe、Cu和Ni、Pt等。

研究表明,采用CVD工艺生长单层石墨烯,可实现晶粒可调、降低石墨烯固有强度、降低碳原料分解的能量屏障。

竞争新顺位,各大厂开始自研+合作

韩国石墨烯广场股份有限公司是石墨烯EUV薄膜商业化的先驱,该公司由首尔国立大学化学教授KwonYong-deok实验室孵化。

该公司已经宣称开发出5nm及以下芯片EUV光刻所需的石墨烯EUV薄膜,并正在为首次公开募股做准备。

其大面积石墨烯EUV薄膜采用专用化学气相沉积(CVD)方法,在高温下使用二氧化碳与铜等催化剂衬底合成的。

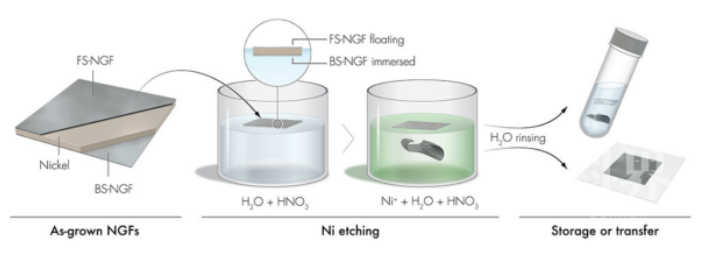

CVD技术将高分子化合物粘附在铜合成的石墨烯上,然后使用蚀刻剂去除铜,最后将石墨烯与分子化合物分离。

半导体和显示材料开发商石墨烯实验室已开发出用石墨烯制造小于5纳米的EUV薄膜的技术,并已准备好量产新型薄膜。

近日,巴西柔性薄膜制造商Packseven宣布已将世界上第一个石墨烯增强拉伸薄膜商业化。

这种新型超薄膜采用GerdauGraphene的专业石墨烯添加剂技术开发而成,更薄且更耐用。

三星电子还开始研究高数孔径(NA)的薄膜,这被称为下一代EUV工艺。该公司在最新招聘通知中提到了基于新材料的下一代薄膜的开发。

它宣布将与外部研究机构合作开发和评估由碳纳米管和石墨烯制成的EUV薄膜。

该公司还计划挑选研究人员,负责设计该公司自行开发的纳米石墨薄膜(NGF)的大规模生产设施。

今年8月,我国首个实现超100微米高性能大厚度石墨烯制膜产业化项目[烯材高性能石墨烯薄膜产业化基地]在沈阳浑南科技城启动试生产。

由深圳烯材科技有限公司投资建设,分两期推进,当日启动试生产的是一期项目,主要生产用于热管理的石墨烯薄膜,项目全面建成后可实现年产值超6亿元。

该项目破解了大厚度、高质量石墨烯膜的制备技术难题,将有力吸引高端专业技术人才加速集聚,为沈阳抢占产业竞争制高点提供关键支撑。

结尾:

为了满足这些严格的标准,需要在薄膜材料和转移工艺方面的研发取得突破。

业界预测,今年EUV薄膜的需求将比去年增加近2倍,而韩国国产的EUV薄膜最早将会在1—2年内商用化。此外,台积电也正在加快开发自己的产品以确保EUV薄膜可控。

审核编辑:刘清

-

单芯片

+关注

关注

3文章

425浏览量

34765 -

cpu芯片

+关注

关注

0文章

46浏览量

13729 -

光刻机

+关注

关注

31文章

1159浏览量

47725 -

ASML

+关注

关注

7文章

722浏览量

41491 -

EUV光刻机

+关注

关注

2文章

128浏览量

15224

原文标题:深度丨当EUV薄膜成为“高精尖”芯片良率的关键

文章出处:【微信号:World_2078,微信公众号:AI芯天下】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

EUV薄膜容错成本高 成芯片良率的关键

EUV薄膜容错成本高 成芯片良率的关键

评论