在ASIC/FPGA项目中,我们会用到很多IP,其中有很多IP存在内部控制信号以及内部状态信号。这些控制信号和内部状态信号影响数据流的接收和发送。

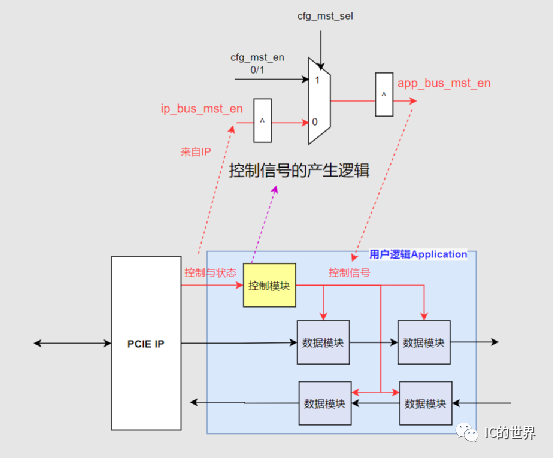

以PCIe为例,蓝色框图部分为PCIe用户侧逻辑,是需要用户实现的逻辑。

左侧白色为PCIe IP,PCIe内部配置空间有一个控制信号,名为bus_master_en(简写),当bus_master_en为0时,不期望用户逻辑发送dma请求(memory读写请求)。

所以在用户逻辑中,我们就需要感知到这些信号的数值,用于控制数据逻辑模块。

通常我们期望这些信号是可控的,能够灵活配置,既给芯片加了一层保障,又方便debug。

即使对IP或者协议的理解有误,也能通过配置规避大部分问题。

那一种很常见的方式就是,添加一个mux,默认情况下,使用ip驱动的控制信号。

如图所示:

ip_bus_mst_en是ip输出的控制信号。

app_bus_mst_en用于控制内部数据模块。

cfg_mst_en和cfg_mst_sel都来自配置csr模块,可灵活配置成0或者1.

cfg_mst_sel默认值为0,表示选择ip_bus_mst_en,在默认情况下,app_bus_mst_en的数据与ip_bus_mst_en相同

这种设计小技巧在IC项目中比较普遍,但是又时常被忘记。

审核编辑:刘清

-

FPGA

+关注

关注

1629文章

21736浏览量

603214 -

控制器

+关注

关注

112文章

16356浏览量

177973 -

FPGA设计

+关注

关注

9文章

428浏览量

26514 -

CSR

+关注

关注

3文章

118浏览量

69631 -

Mux

+关注

关注

0文章

38浏览量

23377 -

PCIe接口

+关注

关注

0文章

120浏览量

9703

原文标题:IC设计:一种IP控制信号的处理方式

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

介绍一种IP控制信号的处理方式

介绍一种IP控制信号的处理方式

评论