1、什么是Pause帧

Pause帧是一种报文类型。在IEEE802.3协议中规定中,pause帧是一种控制帧,用于控制数据流停止发送,在MAC 发送侧产生,在MAC接收侧解析并执行。当此端设备输入数据量过大,无法及时处理时会在此端发送侧MAC产生pause帧,发给对端,要求对端在一定时间内停止发送数据。

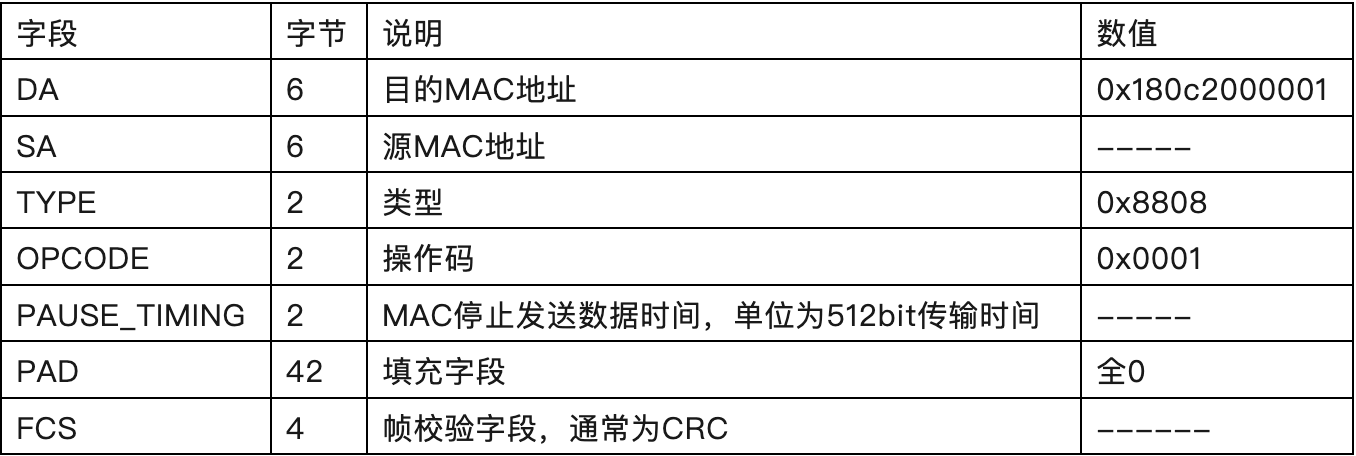

Pause报文由IEEE802.3协议规定,与标准以太帧格式相似:

DA表示目的地址,地址数据固定为0x180c2000001

SA表示源地址 地址由发送方确定

TYPE为报文类型字段,固定为0X8808

OPCODE为操作码,固定为0X0001

PAUSE_TIMING字段为上游MAC停止发送数据的时间,每单位为512bit传输时间,数值为16’d1024表示暂停时间为MAC传输1024*512bit数据所需要的时间

PAD:为填充字段,所有值为0

FCS: 为校验字段,通常为CRC校验值

2、Pause帧的流程过程

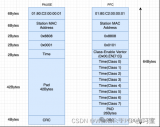

如图所示,左侧为本端芯片,右侧为对端芯片。MAC0和MAC1都包含发送侧tx和接收侧rx。左侧芯片内部mac上游模块A与mac0发送侧有流控信号fc_rdy。信号高表示模块A无法及时处理输入数据,需要进行流控。为了方便突出重点,图中省略了PCS以及serdes等模块。

流程处理如下:

1~2步:对端mac1发送数据给mac0接收侧,进行发送到模块A

3步:模块A无法及时处理输入的数据,需要减少数据输入,从而将fc_rdy拉高。

4步:mac0发送侧tx发现流控信号fc_rdy为高,产生pause帧,发送给mac1接收侧。只要fc_rdy为高,mac0发送侧tx每隔一段时间发送一个pause帧,间隔时间由配置寄存器控制。间隔时长计算由计数器counting计算。Pause帧内停止发送数据的时间由另外一个配置寄存器控制。只要fc_rdy为高期间,mac0发送侧不发送普通数据。

5步:mac1接收侧rx接收到pause报文后,提取pause帧内包含的暂停时间,产生流控信号fc通知MAC发送侧上游模块module B停止发送数据

678:mac1 TX侧在暂停时间内,停止发送数据。MAC0 TX侧可能会发起多个Pause帧。一旦模块A处理完之前的数据后将fc_rdy拉低,则进入第9步

9:步:第9步分2种情况。

情况1:fc_rdy拉低,并且counting在计数没有到一个间隔周期,此时发送pause帧,但是帧内暂停时间为0. Mac1接收到pause帧后,控制tx控制立即开始发送数据。

情况2:fc_rdy拉低的同时,counting正好计数到一个间隔周期,此时不发送pause帧。等到上一个pause帧的暂停时间到达后,mac1发送侧tx继续发送数据。

3、pause帧处理协议强制要求

1)pause的产生发送过程不能中断一个完整的数据报文。即在第4步中,fc_rdy拉高后,首先mac0 tx侧需要判断当前是否正常数据报文在传输。如果有,则需要在当前数据报文传输完成后才能发送pause帧。也就是说在发送过程中,只能在完整数据报文的间隙插入pause帧。

2)新的pause报文暂停时间会覆盖上一个暂停时间。对mac1来说,当mac1接收到新的pause帧后,暂停时间以最新时间为准。

-

处理器

+关注

关注

68文章

19160浏览量

229117 -

寄存器

+关注

关注

31文章

5317浏览量

120004 -

CRC校验

+关注

关注

0文章

84浏览量

15188 -

PCS

+关注

关注

1文章

136浏览量

14621 -

MAC控制器

+关注

关注

0文章

6浏览量

2614

发布评论请先 登录

相关推荐

基于Xilinx FPGA的千兆以太网控制器的开发

基于DWC_ether_qos的以太网驱动开发-MAC帧格式介绍

以太网MAC怪异

以太网控制器(MAC)的基本框架怎么搭建

基于FPGA的以太网MAC控制器的设计与实现

工业以太网协议的历史及其优势

设置AMD以太网IP核的Pause帧处理

深入探究以太网PAUSE帧处理流程及长距离链路控制阈值

什么是Pause帧?以太网MAC的pause流控介绍

什么是Pause帧?以太网MAC的pause流控介绍

评论