HCSL:高速电流控制逻辑(High-speed Current Steering Logic)是Intel为PCIe参考时钟定义的差分时钟,用于PCIe2.0电气规范中定义对RefClk时钟所定义的标准;PCIe时钟采用HCSL这个电平标准使RC(CPU)侧与EP(子卡)侧时钟,在不同生产厂家之间能够保持电平兼容。它需要串行33Ω电阻和驱动源端50Ω电阻下拉到地。HCSL为电流输出驱动,输出结构通过50Ω电阻器下拉接地的15mA开关电流驱动,标称信号摆幅750mV。

HCSL基本电路结构

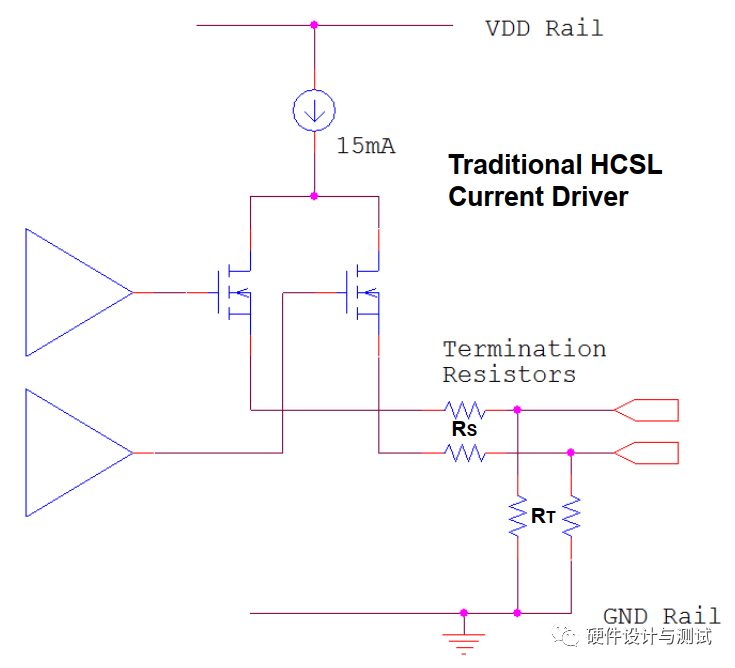

如下图所示,HCSL驱动器是点对点电流驱动电路,具有开源输出的差分逻辑,每个输出引脚在0和14mA之间切换:当一个输出引脚为低电平(0)时,另一个输出引脚为高电平(驱动14mA);OUT+引脚和OUT-引脚通常连接到差分传输线(Z0 =100Ω)或单端传输线(Z0 =50Ω),这需要一个外部端接电阻(50Ω到GND),从而为HCSL输入结构提供700mV的摆幅电平;V = 14mA * 50Ω = 700mV;HCSL输出是经过控制正负输出差分对中的14mA电流,其电源功耗为14mA * 3.3V ≈ 50mW;

HCSL输入要求IN +和IN-的两个输入引脚上的单端摆幅为700mV,共模电压约为350mV;

HCSL电平匹配

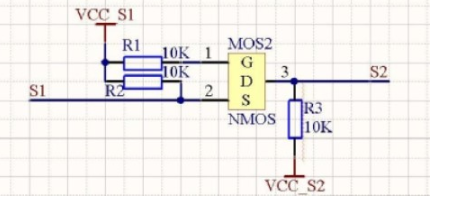

HCSL的电平匹配方法如下图所示,有两种电平匹配方式:终端匹配和源端匹配;正如我们在PCIe时钟设计所示,只要在芯片内部内置50Ω的下拉电阻,那么只需直连设计。

LVPECL到HCSL的转换

如下图所示,在LVPECL驱动器输出端向GND放置一个150Ω电阻对于开路发射极提供直流偏置以及到GND的直流电流路径至关重要。为了将800mV的LVPECL摆幅衰减到700mV的HCSL摆幅时,必须在150Ω电阻之后放置一个衰减电阻(RA =8Ω)。应在HCSL接收器前面放置一个10nF交流耦合电容,以阻止来自LVPECL驱动器的直流电平。放置交流耦合电容后,HCSL输入需要重新偏置,可以通过将470Ω电阻连接3.3V和56Ω电阻到GND上来实现HCSL接收机输入共模的350 mV直流电平

HCSL到LVDS的转换

在下图中,每个HCSL输出引脚在0和14mA之间切换。当一个输出引脚为低电平(0)时,另一个为高电平(驱动14mA)。HCSL驱动器的等效负载电阻为48Ω,与50Ω并联,相当于23.11Ω。LVDS输入的摆幅为14mAx23.11Ω= 323mV。应在LVDS接收器前放置一个10nF交流耦合电容,以阻止来自HCSL驱动器的直流电平。放置交流耦合电容后,LVDS输入需要重新偏置,可以通过将一个8.7KΩ电阻连接到3.3V和5KΩ电阻连接到GND来实现LVDS接收器输入共模的1.2V直流电平。如果LVDS接收器差分输入引脚上已经存在有100Ω电阻,则不需要外部100Ω电阻。

HCSL到CML的转换

在下图中,每个HCSL输出引脚在0和14mA之间切换, 当一个输出引脚为低电平(0)时,另一个为高电平(驱动14mA)。HCSL驱动器的等效负载电阻为68Ω,与50Ω电阻并联,相当于28.81Ω。CML输入的摆幅为14mAx28.81Ω= 403mV。应在CML接收器前面放置一个10nF交流耦合电容,以阻止来自HCSL驱动器的直流电平。另外,必须确认CML接收器输入内部的自偏置。如果没有CML输入端的自偏置,则必须在CML偏置和传输线端接的PCB上放置一个50Ω的端接电阻到VCC。

-

电阻器

+关注

关注

21文章

3827浏览量

62564 -

lvds

+关注

关注

2文章

1050浏览量

66292 -

PCIe

+关注

关注

15文章

1280浏览量

83610 -

电平匹配

+关注

关注

1文章

2浏览量

1370 -

差分时钟

+关注

关注

0文章

10浏览量

4597

发布评论请先 登录

相关推荐

3.3转5V的电平相互转换电路设计

PADS9.5 LOGIC 与 OrCad 原理图相互转换

字符 数字相互转换

字符数字相互转换‘0’是代表字符0吗?

求助LVDS电平转HCSL的转换电路

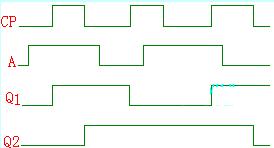

触发器的相互转换

HCSL基本电路结构及其相互转换

HCSL基本电路结构及其相互转换

评论