Sub-LVDS是一种低功耗、低误码率、低串扰和低辐射的差分信号技术,是LVDS技术在Camera接口上的一种应用。Sub-LVDS采用低摆幅电流模式传输系统,同传统的电压模式相比较,在达到几乎相同的性能水平时,由于有比传统模式更好的抗电源噪声能力,它可以在噪声容限低得多,而且摆幅也低得多的情况下工作。目前,Sub-LVDS技术在Sony的Camera/Sensor中比较常见,主要传输的数据格式为RAW10或者RAW12。SUB-LVDS的电压更低,共模电压为1.8V,差模电压为150mV。

Sub-LVDS是LVDS电气规范的低电压版本,不同于LVDS,它的共模和差分信号电平降低,但仍然能够驱动LVDS接收器。当LVDS驱动需要与Sub-LVDS接收器接口连接时,问题就出现了。从驱动的信号开始电压水平不在一个合适的范围内,以确保与接收器的正常通信,必须改变驱动器输出以保证适当的电压水平。本文讨论如何将LVDS驱动器和Sub-LVDS接收器之间的接口互联,以及如何使用简单的电阻网络修改信号电压等级以保证兼容性。

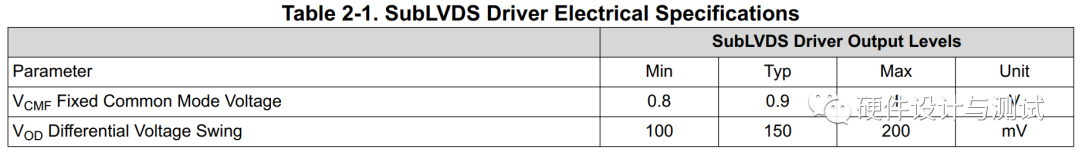

Sub-LVDS驱动器输出参数

Sub-LVDS驱动器接收参数

LVDS输出与Sub-LVDS驱动器接收参数

从以上表格得知,SubLVDS作为LVDS的发展,采用低摆幅电流模式传输系统,同传统的电压模式相比较,在达到几乎相同的性能水平时,由于有比传统模式更好的抗电源噪声能力,它可以在噪声容限低得多,而且摆幅也低得多的情况下工作。设计一个高效电流模式电路的主要挑战是静态功耗,但这在超高速网络中不成问题,因为这时的动态功耗往往起主要作用。再者,此处采用了更加先进的工艺,将供电电压从2.5 V降到1.8 V,输出电压摆幅从350 mV降为150mV,从而可以达到更低的功耗和提供更高的传输速率。

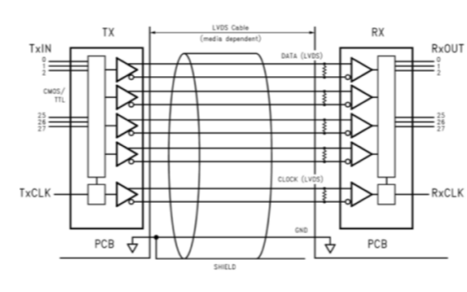

SubLVDS驱动电路

驱动电路是SubLVDS中的重要部分,其功能是实现将输入的CMOS信号转换为差分输出信号,使得在传输过程中,抗噪特性更好。

SubLVDS与LVDS的互联

由于 LVDS 驱动器具有1.2V的典型固定共模电压输出和350mV的典型差分电压摆幅,因此降压电阻网络的目标是实现 0.9V 的固定共模电压以及 150mV 的输出差分电压摆幅。使用简单的电阻网络连接 LVDS 驱动器和 Sub-LVDS 接收器是支持 Sub-LVDS 接收器所需较低信号电压电平的可行且经济的选择。

Sub-LVDS在7系列FPGA的应用

Sub-LVDS在手册xapp582和wp393都有描述,直接看图

选择DIFF_HSTL_II_F I/O标准用于Sub-LVDS发射机,因为它具有0.9V标称的共模电压。DIFF_HSTL_II_F_18的摆幅太大,不能用于subblvds信号。串联终端放置在线路中,以减少信号摆幅,从而满足Sub-LVDS规范,同时保持共模在正确的范围内。

-

FPGA

+关注

关注

1630文章

21761浏览量

604388 -

驱动器

+关注

关注

53文章

8260浏览量

146639 -

接口

+关注

关注

33文章

8650浏览量

151427 -

lvds

+关注

关注

2文章

1043浏览量

65866 -

差分信号

+关注

关注

3文章

378浏览量

27725

发布评论请先 登录

相关推荐

基于FPGA的高速LVDS数据传输

FPGA编程LVDS信号图像处理技术

DLPC3433+DLPA2000+DLP3010开发需要DLP3010把每一帧都投射到不同颜色的幕布上

LVDS接口技术在DAC系统中的应用

基于索尼SUB-LVDS并行桥的设计应用

索尼图像传感器桥接的解决方案

FPGA上LVDS接收器的速度是否会降低?

UltraScale FPGA中的LVDS上的1000Base-X的介绍

如何解决FPGA引脚与LVDS信号相连时兼容性的问题

LVDS在FPGA中的使用教程之LVDS的介绍

基于Sony Sub-LVDS to MIPI CSI-2 Sensor Bridge图像传感器的参考设计

FPGA与LVDS信号兼容性分析方法

基于FPGA的内部LVDS接收器设计

将 LVDS 驱动器与 Sub-LVDS 接收器对接应用说明

Sub-LVDS技术在FPGA上的应用

Sub-LVDS技术在FPGA上的应用

评论