DDR3带宽计算之前,先弄清楚以下内存指标:

型号:MT41K256M16HA-125 IT_4Gb

位宽 :单个DDR读写位宽 X DDR个数=16bit X 4片=64Bit。

内存容量 :256M16;512M8;1G4。

256Meg16:32 Meg x 16 x 8 banks。

- 32Meg:每个BANK的存储大小为32M,1Meg = 1/8MB=1Mbit;

- 中间的16:代表每个bank的读写位宽为16bit;

- 8banks:代表这个DDR的型号有8个bank;

32 Meg x 16 x 8 banks的含义:

每个逻辑BANK的单元格数×每个单元格的位数×逻辑BANK数量,即每个逻辑BANK的单元格数为32兆,每个单元格的数据位是16bit,逻辑BANK的数量为8个。

总大小:32Meg x 16bit x 8banks = 2048Mbit=512MB=0.5GB

tCK :

IO时钟频率 :

时钟频率是指DDR芯片IO管脚CK和CK#上的时钟信号的频率;

最大IO时钟频率=1/tCK=1/1.25ns=800MHz。

内存时钟/核心频率 :

DDR3的时钟频率是核心频率的4倍,200MHz。

DDR2芯片内核每次预读取4倍的数据至IO Buffer中,为了进一步提高外传速度,芯片的内核时钟与外部接口时钟(即我们平时接触到的Clock管脚时钟)不再是同一时钟,外部Clock时钟频率变为内核时钟的2倍。同理,DDR3每次预读取 8倍的数据,其芯片Clock频率为内核频率的4倍。

数据速率 :

DDR方式传输数据(上升和下降沿都传输),所以芯片的一根数据线上的传输速率 = 2*800Mhz = 1600MT/s。

MT/s全称 Million Transfers Per Second意为每秒百万次传输;1Hz=2T/s,1MHz=2MT/s。

传输速率 :

因为DDR信号每个时钟信号可以传输2次,所以实际的传输速率= 2*800Mhz = 1600Mbit/s。

理论带宽 :

理论带宽=传输速率*位宽=1600Mbit*64bit(4片)=12.5GB/s。

有效带宽 :

有效带宽=理论带宽*有效系数=12.5GB/s*0.8=10GB/s。

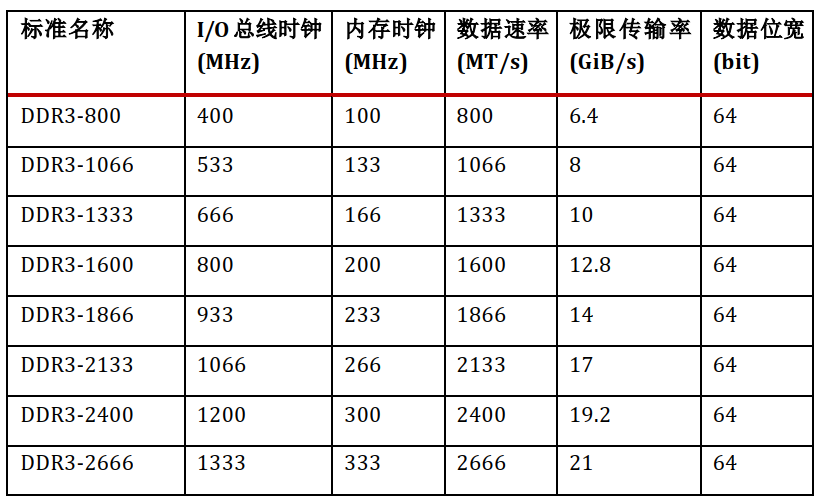

DDR参数不完全统计表

带宽计算表

FPGA所支持的最大频率 :

A7-ds181_Artix_7_Data_Sheet

K7-ds182_Kintex_7_Data_Sheet

V7-ds183_Virtex_7_Data_Sheet

-

FPGA

+关注

关注

1629文章

21729浏览量

602986 -

DDR3

+关注

关注

2文章

276浏览量

42242 -

DDR

+关注

关注

11文章

712浏览量

65318 -

内存

+关注

关注

8文章

3019浏览量

74003 -

带宽计算

+关注

关注

0文章

2浏览量

6333

发布评论请先 登录

相关推荐

基于FPGA的DDR3多端口读写存储管理系统设计

【小知识分享】SDR/DDR1/DDR2/DDR3的接口区别

【小知识分享】SDR/DDR1/DDR2/DDR3的接口区别

如何提高DDR3的效率

基于FPGA的DDR3 SDRAM控制器的设计与优化

如何用中档FPGA实现高速DDR3存储器控制器?

基于FPGA的DDR3 SDRAM控制器用户接口设计

基于FPGA的DDR3多端口读写存储管理的设计与实现

DDR3带宽计算方法 FPGA所支持的最大频率

DDR3带宽计算方法 FPGA所支持的最大频率

评论