概述

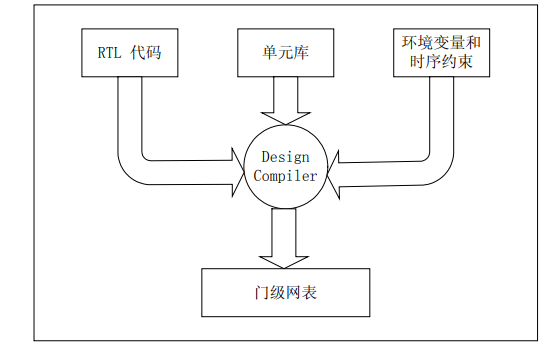

逻辑综合是将RTL描述的电路转换成门级描述的电路,将HDL语言描述的电路转换为性能、面积和时序等因素约束下的门级电路网表。综合后的门级网表也是.v构成的Verilog代码,但是里面并没有我们所写的always或者assign这种语句,而是将标准单元(Standard Cell)实例化并进行连接。

图1 RTL网表转为门级网表

常见的工具是synopsys公司的Design Compiler。

原因

综合最重要的目的是对电路进行约束,从而在性能、面积和时序之间寻求平衡。

图2 性能面积和时序的平衡关系

与DFT的关系: DFT插入的测试逻辑也要与Function的逻辑一起综合,也受上述三个因素的制约,所以Synthesis与DFT关系密切。

流程

逻辑综合的流程为:翻译(Translation)、优化(Optimize)、映射(Mapping)。

图3 综合流程

1.翻译: 综合工具将RTL-level的逻辑电路用门级的逻辑来实现,DC工具用自带的GTECH库中的标准单元去搭建门级逻辑电路,最终形成一个初级的、未优化的门级电路。

(GTECH:Generic Technology, 是Synopsys公司提供的独立于工艺的, 不包含约束的元件库)

2.映射: 将门级逻辑电路映射到由制造商提供的工艺库上。(工艺库包含时序、面积、功耗等约束信息)

3.优化: 综合工具对门级逻辑电路进行分析,去掉电路中的冗余单元,根据设计者添加的约束条件对电路进行优化。

步骤

(1)准备HDL文件和dc_synthesis.tcl运行脚本

对于DFT工程师,需要准备好插入DFT测试逻辑之后RTL-level的HDL 文件和dc_synthesis.tcl运行脚本

(2)设置路径和库文件

设置DC工作路径和库文件搜索路径

define_design_lib work –path work

set search_path /project/dft/library/db

在dc_synthesis.tcl运行脚本中设置target_library(目标库),和link_lbirary(链接库)

set link_library [list adk.db memory.db pad.db]

set target_library [list adk.db memory.db pad.db]

(3)用analyze/elaborate命令读入设计

读入1st insertion和2nd insertion之后的所有RTL文件

*source ../inputs/use_in_synthesis.tcl *

分析HDL文件代码检查设计错误。

读入1st insertion和2nd insertion之后的sdc文件

source ../../tsdb_outdir/dft_inserted_designs/{design_name}_{design_id}.dft_inserted_ design/${design_name}.sdc。

elaborate ${design_name} //建立HDL代码的门级描述

link //将读到DC中的模块连接起来

current_design ${design_name} //设置当前设计名称

check_design //设计规则检查

(4) 设置约束条件

可以在constrait.tcl约束脚本里将约束条件设置好,再导入到dofile。也可以直接在dofile里设置。

*set preserve_instances [tessent_get_preserve_instances icl_extract]

*

set optimize_instances [tessent_get_optimize_instances icl_extract]

set_boundary_optimization $preserve_instances false

set_ungroup $preserve_instances false

set_boundary_optimization $optimize_instances true

preserve_instances表示不做边界优化的instances

optimize_instances表示做边界优化的instances

set_boundary_optimization表示对指定instance做边界优化

boundary_optimization即边界优化是一种优化策略, 指是否允许DC跨module的边界优化, 允许的话, 有些没用的端口会被去掉, 有些逻辑会被优化掉, 有些信号的名字也会丢失。对于DFT工程师不希望插入的逻辑被优化掉,所以要对插入的逻辑有选择地进行边界优化

set_ungroup表示对指定instance做ungroup

ungroup指的是打破设计的层次关系, 把hierarchical设计变成flat设计, 不需要层次关系的端口, 更有利于优化

图4 ungroup过程

(5) 用compile命令对施加约束的门级网表进行编译,生成优化的门级网表

(6) 用write/write_sdf/write_sdc/命令将优化后的门级网表以指定的格式保存到指定的路径

write -f verilog -output ../outputs/${design_name}.synthesis.v

write_file -format ddc -output ../outputs/${design_name}.synthesis.ddc

write_sdc ../outputs/${design_name}.synthesis.sdc

write_sdf ../outputs/${design_name}.synthesis.sdf

图5 综合具体流程

约束

DC综合流程中设置约束的种类有:时序约束、面积约束。时序约束:包括时钟约束、输入/输出接口约束和时序例外约束。时序约束是通过约束各类延迟信息,保证门级电路能够正常工作。

图6 约束的分类

1. 时钟约束: 是对主时钟进行约束定义,帮助时序分析工具定义时序路径分析的一个时间零点,时钟传输过程中的延时和不确定性也都会基于这个时间零点进行计算和分析。

主时钟: 是指由外部输入模块内部的时钟,或是内部模块产生的时钟。

约束的命令为:

create_clock -name clk -period 10 -waveform {0 5}

该命令用于定义有特定周期和波形的时钟

create_clock用于定义一个时钟

-name用于指定时钟名

-period用于指定时钟周期

-waveform用于指定上升沿和下降沿的时刻

图7 时钟约束1

图8 时钟约束2

set_clock_latency –source 3 [get_clks CLK]

上述命令用于对时钟源延时进行约束

set_clock_latency 1 [get_clks CLK]

上述命令用于对时钟网络延时进行约束

set_clock_uncertainty -setup -hold

上述命令用于对时钟的偏移和抖动进行约束

可通过*-setup 和 -hold*参数设置建立时间和保持时间的偏移值

set_clock_transition -max 3 [get_clks CLK]

上述命令用于对时钟的转换时间进行建模。默认的上转换时间为从电压的20%上升至80%的时间,下转换时间为从电压的80%下降至20%的时间

可通过*-rise 和 -fall*参数设置上转换时间和下转换时间:

set_clock_transition -rise 2 -fall 3 [get_clks CLK]

图9 时钟约束3

2. IO约束: 指定input信号和output信号输入或输出模块的延迟时间。

set_input_delay

用于指定输入数据的路径延时, 分析从外部输入到内部寄存器的延迟, 需满足内部寄存器的建立/保持时间。

set_output_delay

用于指定输出数据的路径延时, 分析从内部寄存器到外部输出的延迟,需满足外部寄存器的建立/保持时间。

图10 IO约束

3.时序例外约束: 可以对某些路径放宽时序要求, 减少对布局布线资源的占用, 从而尽可能多地释放出宝贵的资源给时序约束要求较高的关键路径,合理分配资源,能够更好地确保整个系统的时序收敛。

对时序例外进行约束的命令有:

set_multicycle_path

在2个时钟域之间传输数据,指定从起始时钟沿到目标时钟沿所需的时钟周期数。允许数据在多个周期后稳定并接收, 时序要求宽松。

set_false_path

指定在设计中不做分析的时序路径,即最低优先级的路径。

图11 时序例外约束

4.面积约束: 就是告诉DC工具, 综合完成后的电路面积不能超过多少。

set_max_area 100

指定综合完成后的最大面积为100(单位与工艺库的要求一致)。

-

寄存器

+关注

关注

31文章

5389浏览量

121836 -

RTL

+关注

关注

1文章

386浏览量

60146 -

SDC

+关注

关注

0文章

49浏览量

15640 -

DFT算法

+关注

关注

0文章

27浏览量

7612 -

HDL语言

+关注

关注

0文章

47浏览量

8979

发布评论请先 登录

相关推荐

[启芯工作室]逻辑综合 06 Timing Analysis

FPGA的逻辑仿真以及逻辑综合的一些原则

DC逻辑综合

ASIC逻辑综合及Synopsys Design Compiler 的使用资料说明

什么是逻辑综合?逻辑综合的流程有哪些?

什么是逻辑综合?逻辑综合的流程有哪些?

评论