0****1

仿真验证平台结构

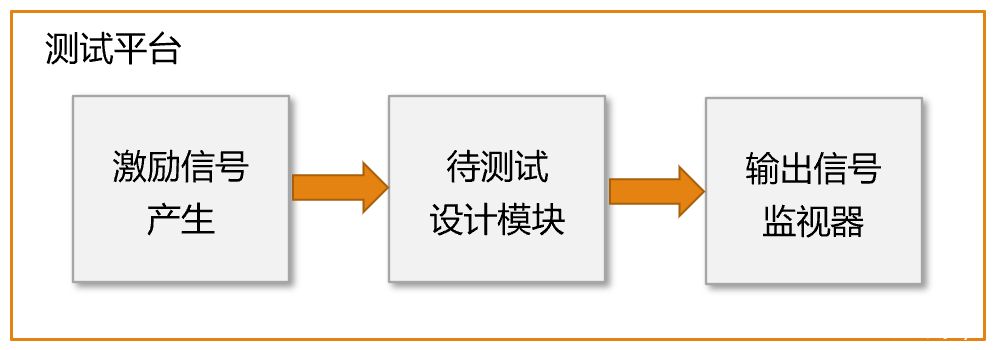

仿真验证主要作用是搭建一个测试平台,测试和验证程序设计的正确性,验证设计是否实现了我们所预期的功能。其结构如下图所示。

图中可以看到,这个测试平台本身对外没有输入输出端口的,我们需要通过实例化的方式将待测试模块放置于仿真中,然后设计相应的激励信号加载在待测试模块的输入端,运行仿真后观测输出信号是否正确。

下图是2选1多路选择器的仿真测试代码,我们依次解读各部分内容。

`timescale 1ns/1ps

`timescale是预编译指令,用于定义时间单位和时间精度。此处,时间单位为1ns,时间精度为1ps。

因此,语句 always #10 a=~a 中“#10”表示延时10ns。

reg a,b,sel;

wire out;

信号声明部分包含两部分。

待测试模块的输入信号,在仿真文件中是需要设计的激励信号,一般在always和initial语句中描述,因此,声明为reg型。

待测试模块的输出信号是待观察的信号,声明为wire型。

initial begin

a=0;b=0;sel=0;

end

always #10 a=~a;

always #20 b=~b;

always #40 sel=~sel;

以上是激励信号的描述。

mux2_1 uut(

.a(a),

.b(b),

.sel(sel),

.out(out)

);

以上是待测试模块的实例化。uut是实例名,由用户自定义,不能缺少。

0****2

仿真验证一般步骤

• 新建仿真文件(.v),与源程序文件名不能相同。

• 模块声明:对外没有输入、输出端口。

• 信号声明:待测模块的输入信号声明为reg型,输出信号声明为wire型。

• 设计激励信号:对待验证模块的输入端口信号进行模拟,覆盖所有情况。

• 实例化待测模块:对待测模块进行实例化。

• 运行仿真:Run Behavioral Simulation(行为仿真)

• 观察仿真结果:判断被测试模块的输出响应是否符合预期要求

03

如何观察内部信号

①scope窗口选则待测试模块(uut是待测模块实例名)。

②将想要观察的信号拖到仿真波形窗口。

③重新加载仿真(relaunch simulation)。

-

仿真验证

+关注

关注

0文章

25浏览量

8138 -

HDL语言

+关注

关注

0文章

47浏览量

8916 -

Verilog设计

+关注

关注

0文章

20浏览量

6520 -

多路选择器

+关注

关注

1文章

22浏览量

6529

发布评论请先 登录

相关推荐

Verilog HDL入门教程(全集)

硬件验证语言——简介

使用ModelSim进行设计仿真

使用 ModelSim 进行设计仿真

Verilog HDL硬件描述语言_验证

设计与验证:Verilog HDL(清晰PDF)

基于System Verilog的可重用验证平台设计及验证结果分析

如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真

如何使用Verilog语言进行仿真验证

如何使用Verilog语言进行仿真验证

评论