0****1

什么是有限状态机

如果一个对象(系统或机器),由若干个状态构成,在某种条件下触发这些状态,会发生状态相互转移的事件,那么此对象称之为状态机。描述对象的状态往往是有限的,所以状态机又称为有限状态机(Finite-state machine,FSM)。

有限状态机是一种数学模型,是时序电路常用的设计工具,更是一种设计思想、设计方法。

有限状态机的本质是在描述一系列具有先后顺序和时序规律的事件。

有限状态机核心是处理各种输入事件和状态切换,产生输出控制信号。

0****2

有限状态机的四要素

现态:当前的状态;

条件:触发状态转移的事件,即状态输入;

动作:执行某种操作,即状态输出;

次态:满足条件后跳转到下一状态。

03

有限状态机描述方法

第一步, 逻辑抽象,得出状态图或状态表。主要包括:

· 分析给定的逻辑问题,确定系统的状态、输入变量和输出变量。

· 分析确定每一个状态的输入、状态转移条件和输出。

第二步,根据状态转移图或表进行状态化简。

第三步,状态编码。

第四步,根据状态转移图或表进行代码描述。

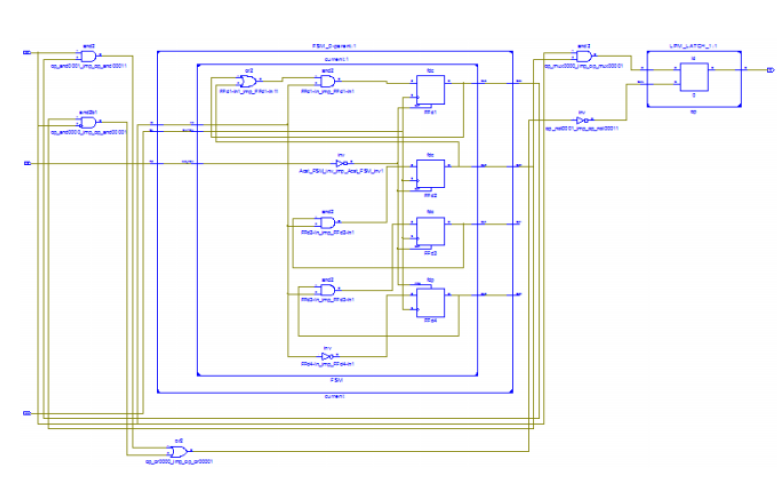

使用Verilog HDL描述状态机,有一定的固定格式,以三段式状态机为例:

第一段,使用时序逻辑,描述现态,使用非阻塞赋值。

第二段,使用组合逻辑,描述次态,使用阻塞赋值。

第三段,使用可以使用组合逻辑,也可以使用时序逻辑进行描述,主要描述的是输出控制信号。

-

编码器

+关注

关注

45文章

3719浏览量

136001 -

有限状态机

+关注

关注

0文章

52浏览量

10423 -

状态机

+关注

关注

2文章

493浏览量

27838 -

HDL语言

+关注

关注

0文章

48浏览量

9008

发布评论请先 登录

相关推荐

什么是有限状态机呢

有限状态机的建模与优化设计

VHDL有限状态机设计-ST

初学者对有限状态机(FSM)的设计的认识

如何使用FPGA实现序列检测有限状态机

有限状态机设计是HDL Designer Series的关键应用

基于事件驱动的有限状态机介绍

基于事件驱动的有限状态机介绍

一个基于事件驱动的有限状态机

什么是有限状态机?有限状态机的四要素介绍

什么是有限状态机?有限状态机的四要素介绍

评论